【《硬件架构的艺术》读书笔记】02 时钟和复位(2)

2.4 时钟方案

2.4.1 内部产生的时钟

应尽量避免內部产生时钟。

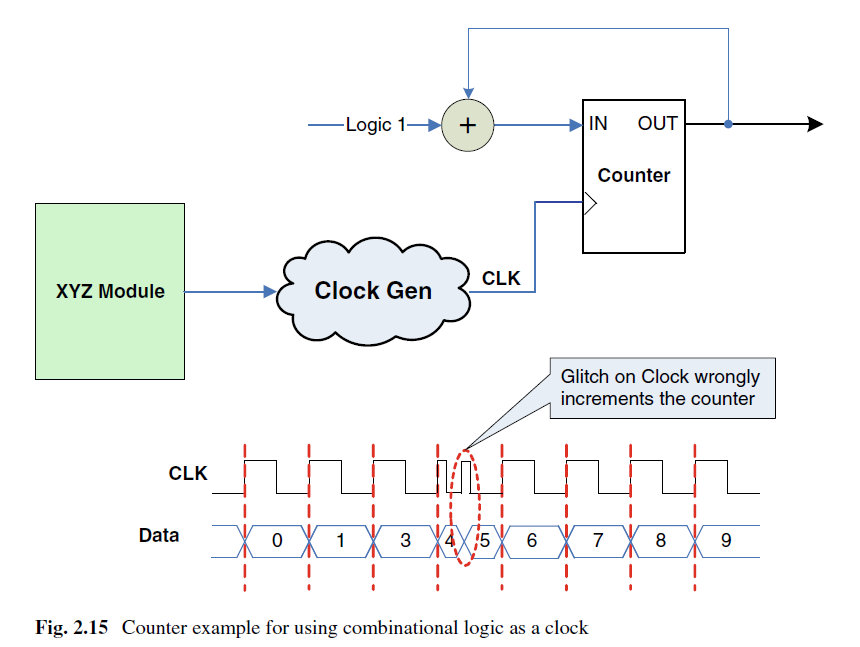

组合逻辑产生时钟会引入毛刺,也会引起时序方面的问题。同步时序电路数据的毛刺不会引起任何问题,而毛刺出现在时钟输入端或异步输入端就会产生明显的影响。

毛刺到达时钟输入端如果数据变化,会违背建立和保持时间。即使没有违背时序要求,寄存器也可能输出意料外的值。

毛刺可能导致计数器增加额外的计数值,如图。

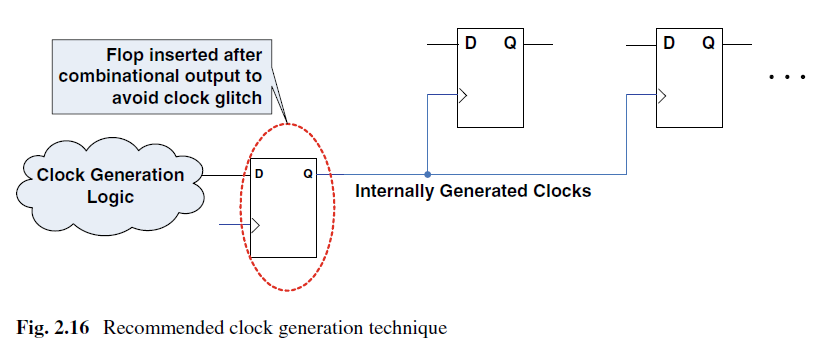

解决方法:组合逻辑输出增加一个寄存器输出,这个寄存器可以阻止组合逻辑产生的毛刺。

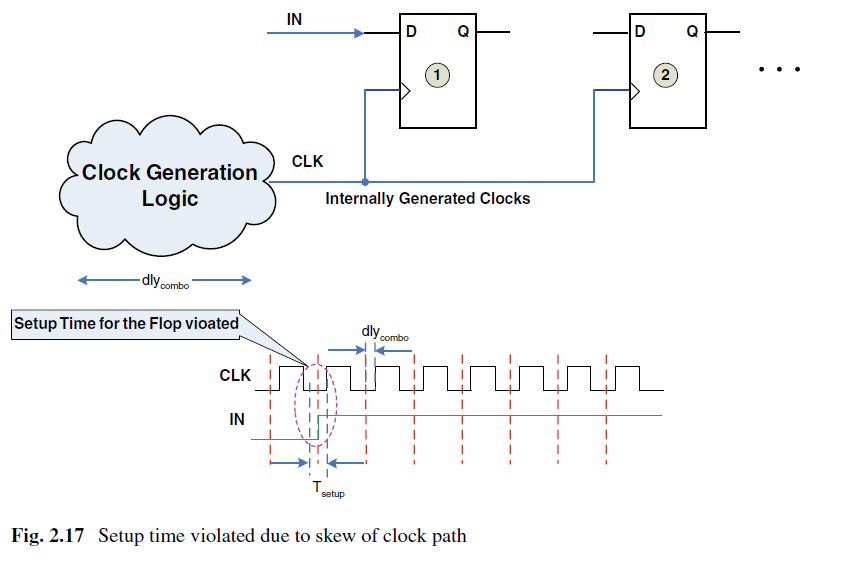

组合逻辑时钟也会增加时钟延迟,可能导致违背时序要求。

图中由于时钟偏移导致违背了建立时间。(这里应该也有问题,这图上CLK往左移dlycombo不也违背建立时间了吗)

一种减少时钟偏移的方法:将产生的时钟放到SoC中高扇出且低偏移值的时钟树上。

2.4.2 分频时钟

设计中要保证大多数时钟来自于PLL,避免异步时钟分频逻辑引起的许多问题。对主时钟分频时应使用同步计数器或状态机。

保证总是由寄存器直接产生分频时钟信号,不要使用组合逻辑避免毛刺和尖峰脉冲。

2.4.3 行波技术器

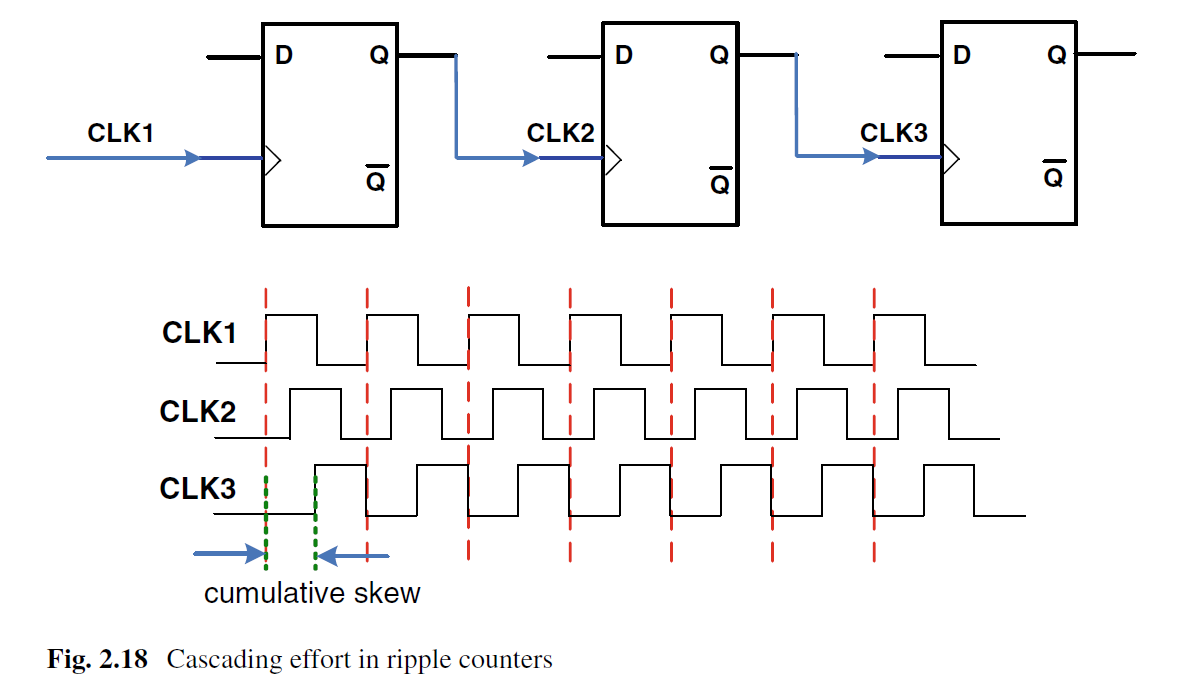

使用行波计数器对时钟进行幂为2的分频。

优点:使用的门更少。

缺点:对STA和综合工具带来麻烦,应尽量避免。

功耗较高的系统中很适合使用这种计数器,可以大量降低由逻辑或SoC所引起的峰值功耗。

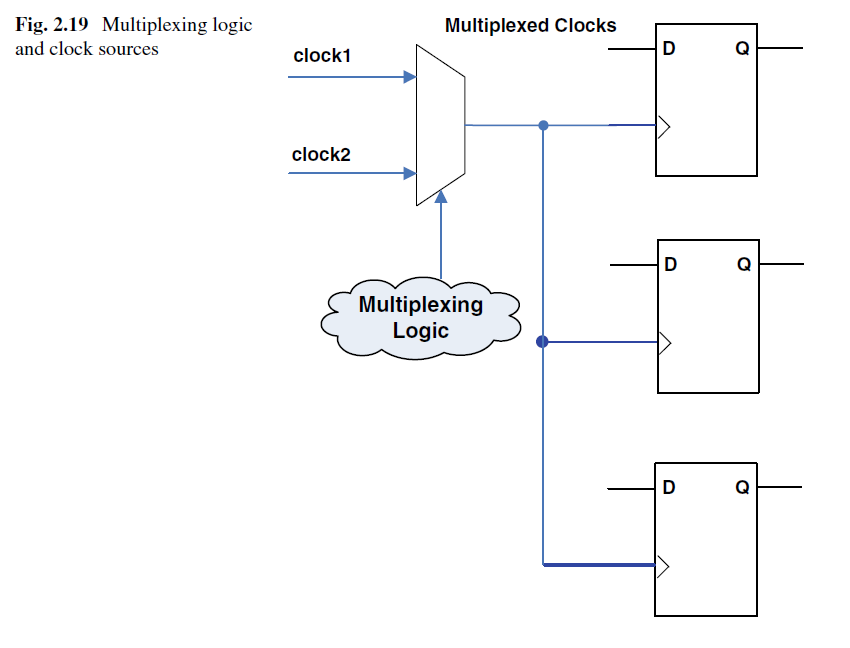

2.4.4 多路时钟

需要处理多个频率标准的通信应用常常使用多个时钟。

使用多路时钟的前提:

2.4.5 同步时钟使能和门控时钟

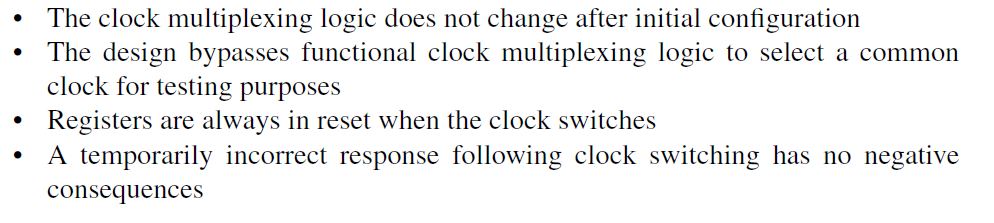

优点:减少功耗。

缺点:不是同步设计,显著增加设计时间和验证的工作量。增加时钟偏移并对毛刺敏感,所以能导致设计失败。

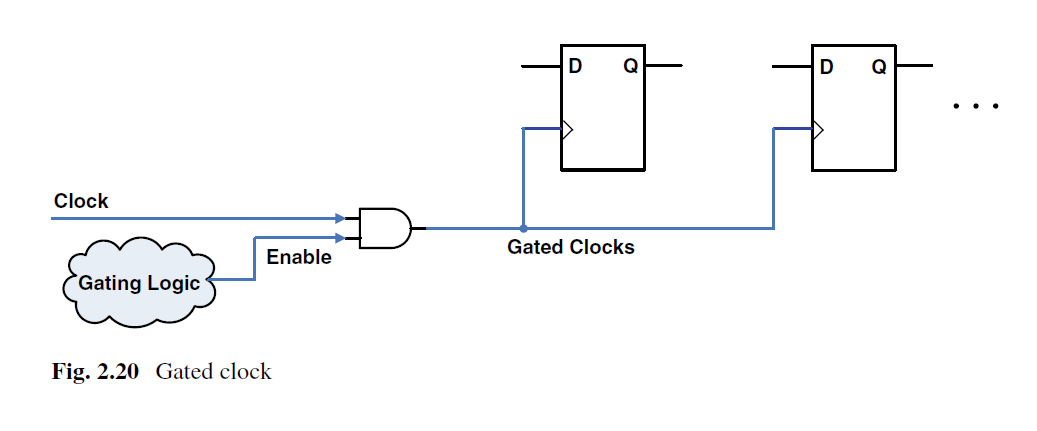

可以使用同步的时钟使能,用纯同步的方法关闭时钟域,但这样时钟树一直保持反转,触发器保持内部活跃,无法降低功耗。

这里通过选通信号选择触发器输入,但是并没有真正意义上关闭触发器,只是使其值保持。

2.5 门控时钟方法学

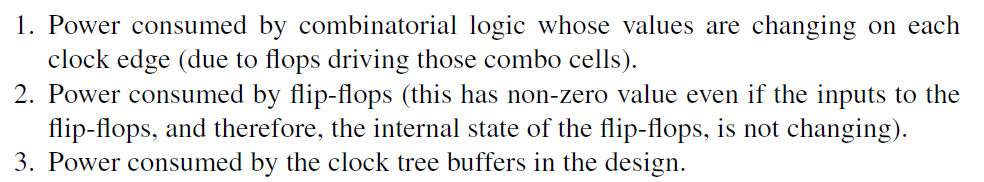

同步设计风格中,功耗主要由三个部分组成

对时钟门控能够大幅降低触发器的功耗,门控可以在时钟数的根部、末端或者两者之间的任何位置。

时钟数几乎消耗了整个芯片功耗的50%,所以最好在根部产生或者关闭时钟。

使用图2.21的方法则会使用三个多路选择器。

2.5.1 不带锁存器的门控时钟电路

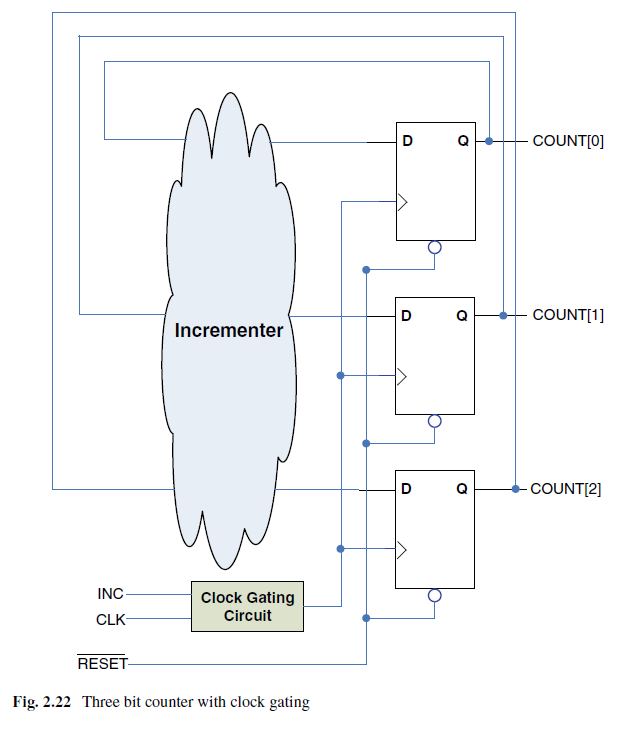

使用与门、或门实现。为避免过早截断或产生多个时钟脉冲、应强制要求使能在时钟上升沿到下降沿一直保持常量。该限制使得基于单时钟触发器的设计中不适合使用不含锁存器的门控时钟。(因为对使能信号有较高的要求)

图中为过早截断的情况。

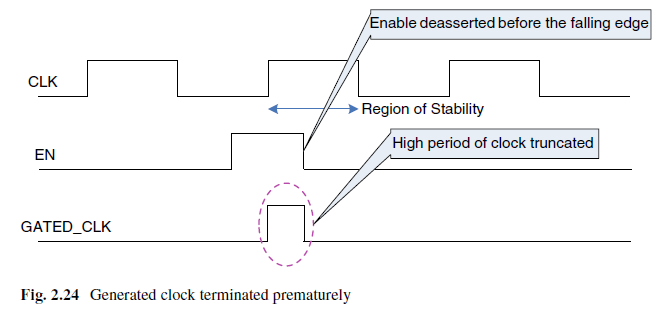

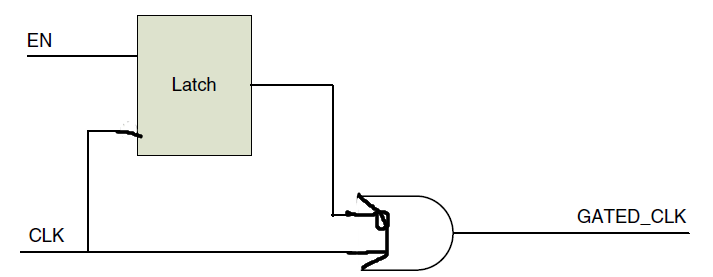

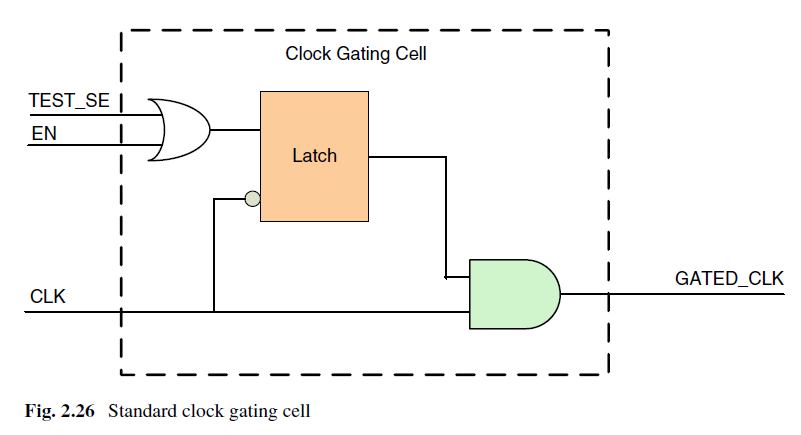

2.5.2 基于锁存器的门控时钟电路

使用锁存器就可以使门控时钟电路不需要满足上面的条件了。

使用与门控制上升沿有效的时钟,反之使用或门控制。

这个电路在使能关闭时为低电平,当打开时便不会漏掉下降沿。

使用这项技术时,使能信号必须在半时钟周期内产生。(锁存器只在半个时钟周期内具有锁存功能)

要保证设计中所有时钟能同时使能以便DFT,可以再加一个或门。

2.5.3 门控信号

特殊部分使用门控信号提高能效。(感觉这里的意思就是减少组合逻辑的功耗)

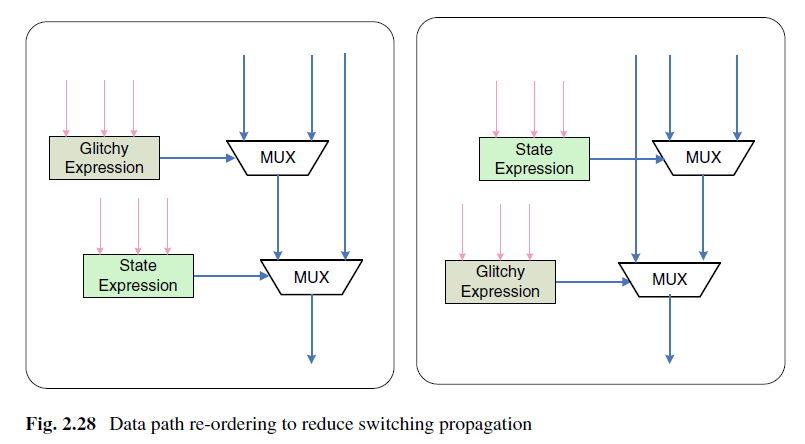

2.5.4 重组数据路径以减少转换传播

这里的意思应该是把容易产生毛刺或者会经常翻转电平的电路放在电路后级,可以减少转换传播从而降低功耗。

浙公网安备 33010602011771号

浙公网安备 33010602011771号