A Proposal To Remove Those Ugly Register Data Types From Verilog

不同于VHDL,Verilog中的数据类型分成了寄存器型(register type)和线型(net type)两种。其中寄存器型包括

reg integer time real realtime

线型包括

wire tri wor trior wand triand tri0 tri1 supply0 supply1 trireg

一个简单的使用原则为

- 连续赋值的左值(LHS)必须是net型

- 过程赋值的左值必须是register型

文章提到了一个我以前不知道的点就是多驱动的问题。首先是net型,下面的代码

module drivers1(y,a1,en1,a2,en2);

output y;

input a1,en1,a2,en2;

assign y = en1 ? a1 : 1'bz;

assign y = en2 ? a2 : 1'bz;

endmodule

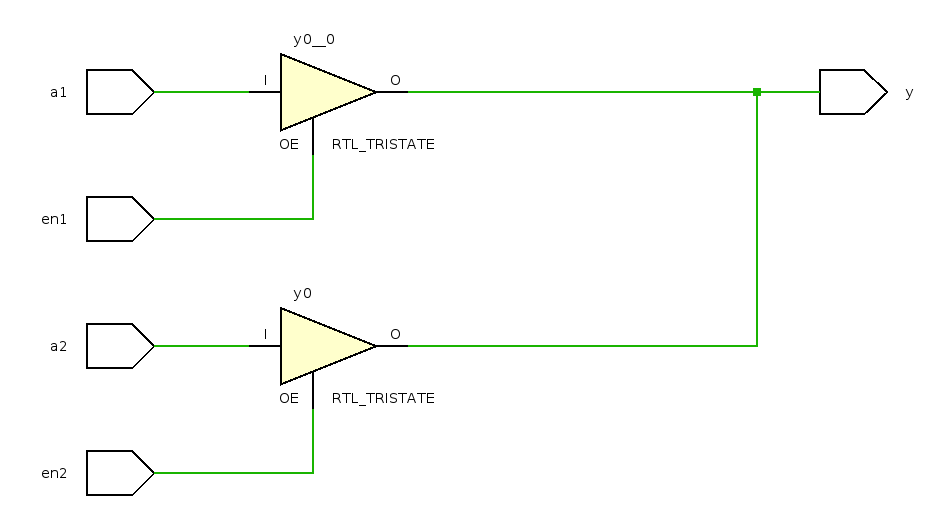

这段综合出的电路如下图所示

也就是一个net型是可以有多个驱动源的。但是register型就不可以,例如下面的代码

module driver1s2(y,a1,en1,a2,en2);

output y;

input a1,en1,a2,en2;

reg y;

always@(en1,a1)

if(en1)

y = a1;

else

y = 1'bz;

always@(en2,a2)

if(en2)

y = a2;

else

y = 1'bz;

endmodule

按照原文的说法,这里应该是最后一个always块生效,也就是只有en2和a2起作用。但是我用vivado实际测试发现这两种写法生成的电路是一样的。这里就没有进一步在design comile里尝试了。

对于reg和wire的讨论有很多。有的说法是一开始Verilog只是用来仿真的,reg代表具有存储功能的变量,在仿真过程中它的值需要被记录,而wire代表连线,本身不具有驱动能力。

浙公网安备 33010602011771号

浙公网安备 33010602011771号