Quartus 调试笔记

Quartus 调试笔记

@(verilog)

最近忙于芯片跟测试FPGA联调,解锁了不少quartus的用法,在此记录一下备忘。

目录

一. modelsim 联仿

1. tb文件创建

- Processing --- Start --- Start testbench template writer

- 自动创建当前top 模块的testbench, 自动例化完整,创建的tb文件一般在simulate/modelsim文件夹下(.vt类型)

2. modelsim联仿环境

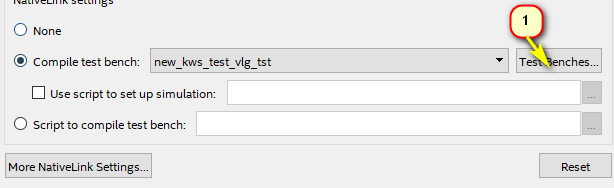

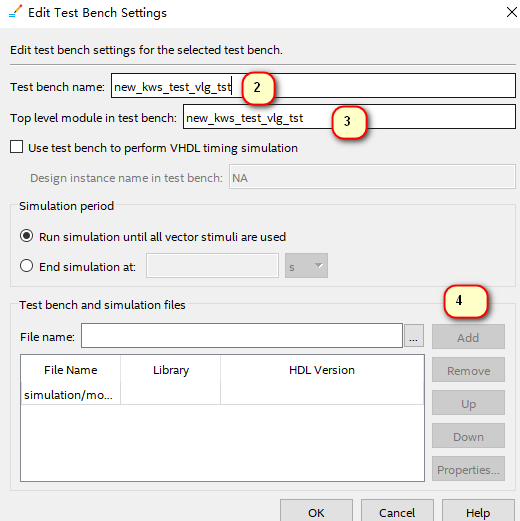

- Assignment -- setting -- EDA tool settings -- simulation 中选择tool为modelsim之后勾选compile test bench。

点击testbenches, New , 之后填入tb name, top module name (tb顶层名要和实际tb里的一致),然后file name中选择之前自动创建的tb.vt文件,然后就可以一路ok了

最后点击 Tool--- run simulation tool --- rtl simulation就可以打开modelsim仿真了。

二. modelsim - quartus 动态调试仿真

实际上每次在quartus中对工程做了修改以后,再次仿真没必要关掉之前的modelsim。 只需要配置一下wave.do文件即可,具体步骤如下:

- 首先在modelsim中,File --- Save Format ,将当前调试环境保存为wave.do文件。一般是放在simulation/modelsim文件夹下。之后建议把这个wave.do文件加入到工程中方便修改。

- 打开wave.do文件,可以看到里面都是modelsim中调试过程进行的一些操作,包括添加信号,仿真时间设定等等,比如我的是:

onerror {resume}

quietly WaveActivateNextPane {} 0

add wave -noupdate /new_kws_test_vlg_tst/clk_50M

add wave -noupdate /new_kws_test_vlg_tst/rstn

add wave -noupdate /new_kws_test_vlg_tst/clk_200k

add wave -noupdate /new_kws_test_vlg_tst/I_threshold_load_finish

add wave -noupdate -radix decimal /new_kws_test_vlg_tst/i1/mem_addr

TreeUpdate [SetDefaultTree]

WaveRestoreCursors {{Cursor 1} {130261609 ps} 0}

quietly wave cursor active 1

configure wave -namecolwidth 353

configure wave -valuecolwidth 100

configure wave -justifyvalue left

configure wave -signalnamewidth 0

configure wave -snapdistance 10

configure wave -datasetprefix 0

configure wave -rowmargin 4

configure wave -childrowmargin 2

configure wave -gridoffset 0

configure wave -gridperiod 1

configure wave -griddelta 40

configure wave -timeline 0

configure wave -timelineunits ns

update

WaveRestoreZoom {5044059661 ps} {5543637850 ps}

后面要添加波形也可以参照这里的写法直接在do文件里修改。

但是光这些脚本还没法做到一键运行,缺少.v文件的信息,所以需要下面的流程。

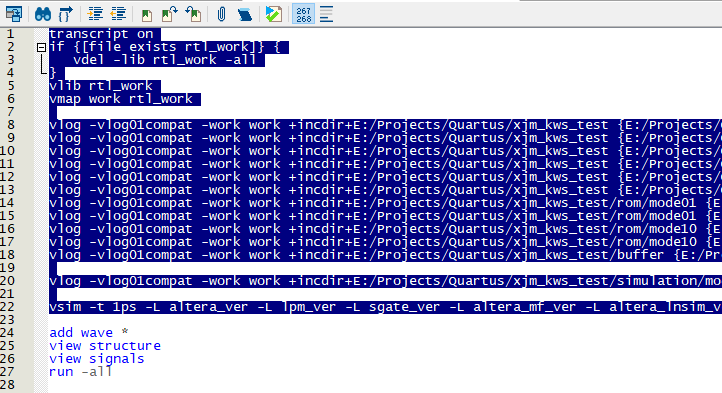

- 在simulation/modelsim中找到一个_rtl_verilog.do后缀的文件,里面包含上面提到的缺失脚本,大概长这样:

把选中部分粘贴到wave.do里就可以了。

- 之后的仿真流程就是,在quartus中编写verilog和testbench并保存,之后跳到modelsim中依次输入命令:

quit -sim

do wave.do

就可以仿真修改后的工程了,无需“反复横跳”。当然,如果工程中加入了新的.v,只要在wave.do中仿照之前的格式添加就可以了。

前几天看到有FPGA

三. quartus-modelsim仿真ROM注意事项

- modelsim中仿真quartus中的ROM IP时,不支持mif格式,最好在quartus中File,save as将mif 保存为hex

- 最好把rom ip和hex都放在工程文件同目录下。

四. SignalTap 使用

基本使用方法可以参考:

https://blog.csdn.net/k331922164/article/details/47623501

抓数据神器,只需要一个jtag, 虽然每次添加新信号都要重新编译烧录,但总比示波器方便多了。

波形图跟采样深度大小有关,深度越大采样的数据越多。目前还不知道如何将一段时间内所有数据点存下来,(貌似只能保存触发点之后采样深度大小的波形,不知道有没有什么方法可以存一段时间内的所有波形)。但就调试基本使用而言足够了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号