mutli-lane情况

PCIE3.0支持x1,x2,x4,x8,x16,x32 Lane widths.

在多条Lane情况下,有2类symbol framing,一类包含Ordered Sets,一类是TLP和DLLP。

Ordered Sets会同时在每条Lane上传输,所以每条Lane都会有完整的OS.

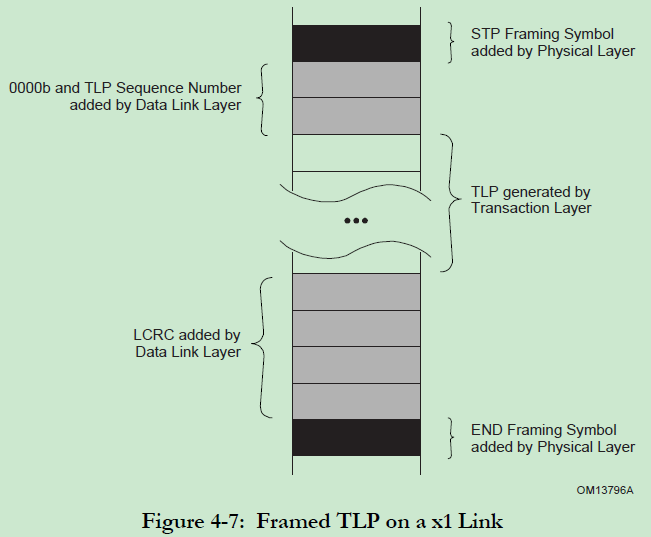

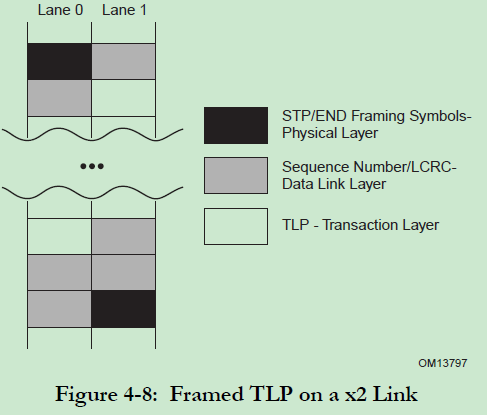

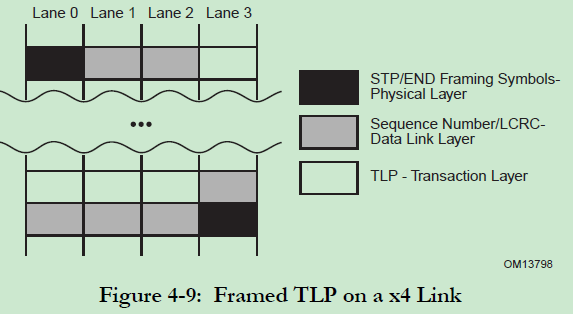

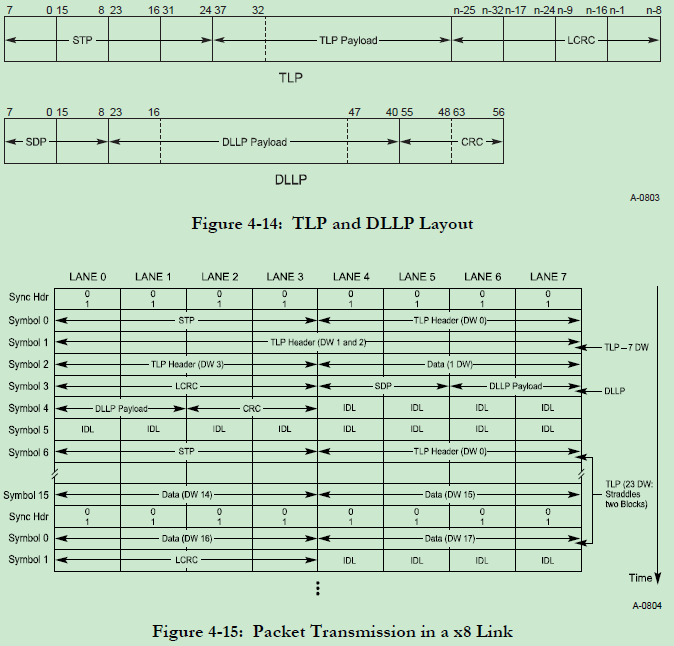

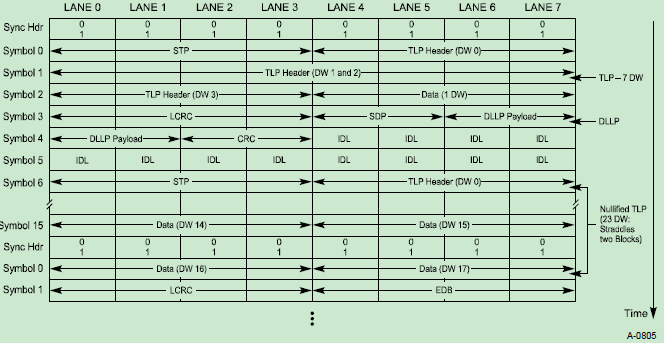

对于TLP/DLLP来说,Symbol在多条Lane上的传输方式是第一个Symbol放在Lane 0,第二个在Lane 1,然后依次类推。

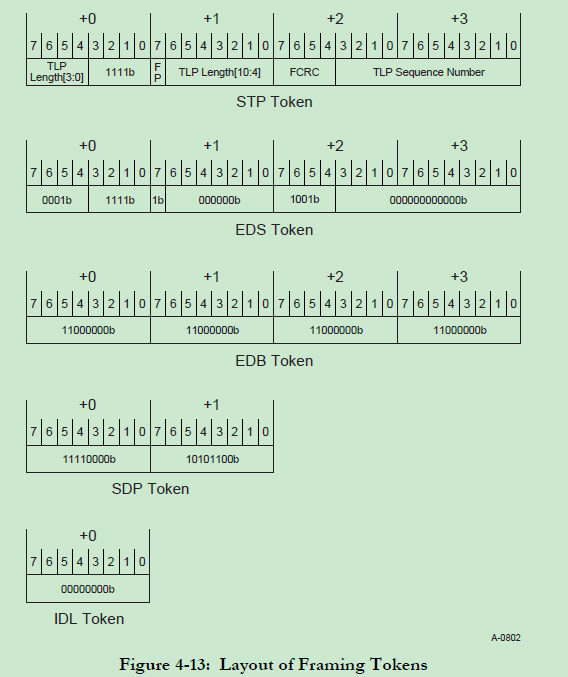

由于TLP是由STP+TLP+END组成,DLLP是由SDP+DLLP+END组成,所以如果是从logical IDLE 状态开始传输,STP/SDP需要放在Lane 0.

在multi-lane情况下,一个symbol时间内,STP只能出现一次,SDP也只能出现一次,但STP可以和SDP出现在同一个symbol时间内,需要注意的是STP或SDP需放在4的倍数Lane上。

对于xN link,如果N大于等于8,END/EDB symbol放在k<N-1, 且后面不跟TLP或DLLP,则需要在K+1至N-1的Lane上放置PAD。

二:对于8Gbps情况

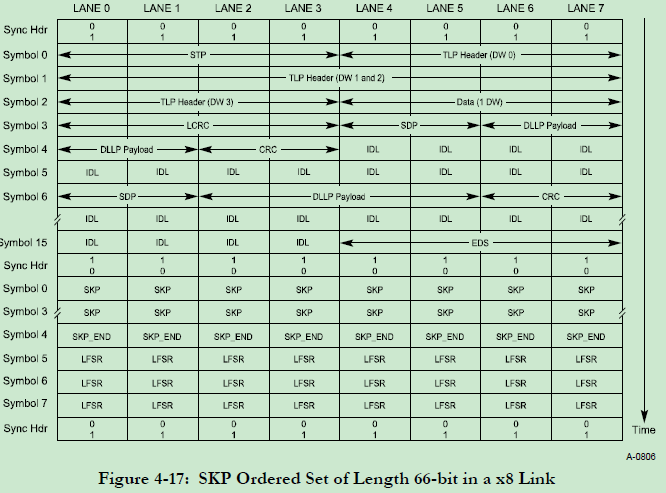

8Gbps采用128b/130b,数据以Block方式传输,分为Data Block和Ordered Set Block,每个Block有128Bit的payload,再加上2Bit的Sync Header. Data Block的Sync Header是10b,Ordered Set Block是01b。

当有多条Lane存在时,每条Lane上都需要同时传输Sync Header。Block是针对每条Lane的概念,即每条Lane上的两个Sync Header之间应该是16 symbols。

在128b/130b情况下,发送端不会截断TLP,即使是nullified TLP,总是会发送STP中定义的长度。

浙公网安备 33010602011771号

浙公网安备 33010602011771号