RISC-V特权模式spec学习笔记

本文基于官方spec进行整理学习 https://wiki.riscv.org/display/HOME/RISC-V+Technical+Specifications

特权模式spec讲了啥,内容有哪些

- 特权模式的软件视角

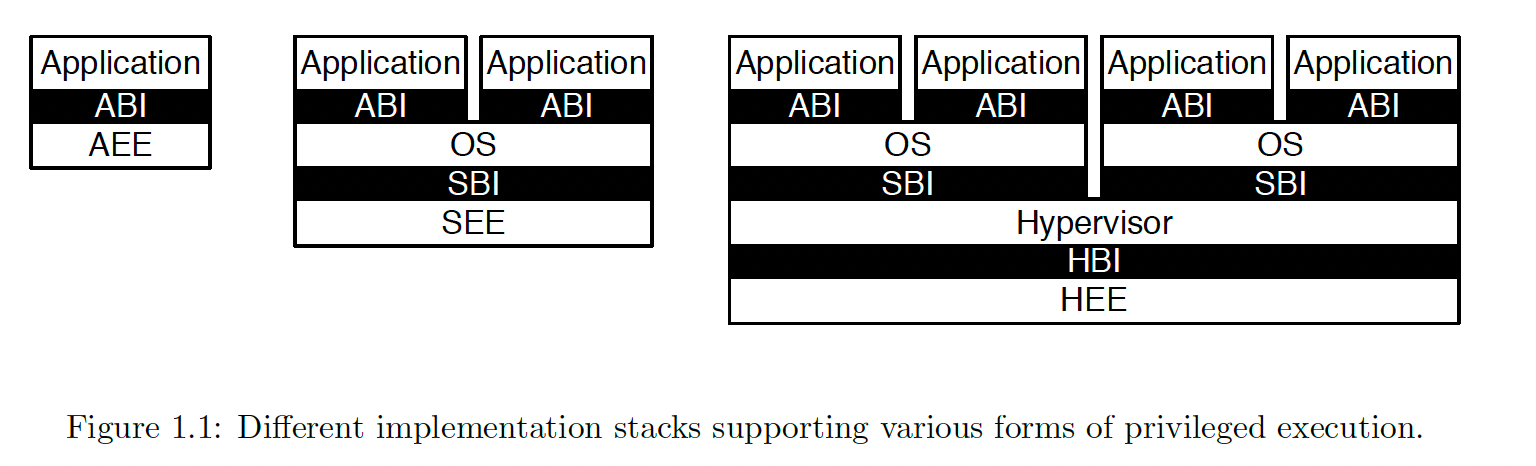

- 软件分层:AEE/SEE/HEE

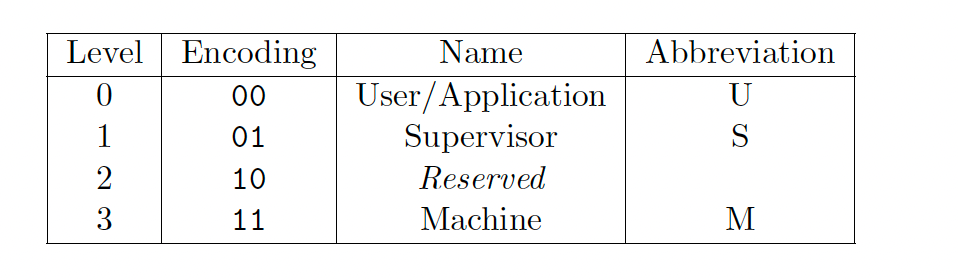

- 特权等级:User/Supervisor/Hypervisor/Machine

- debug模式

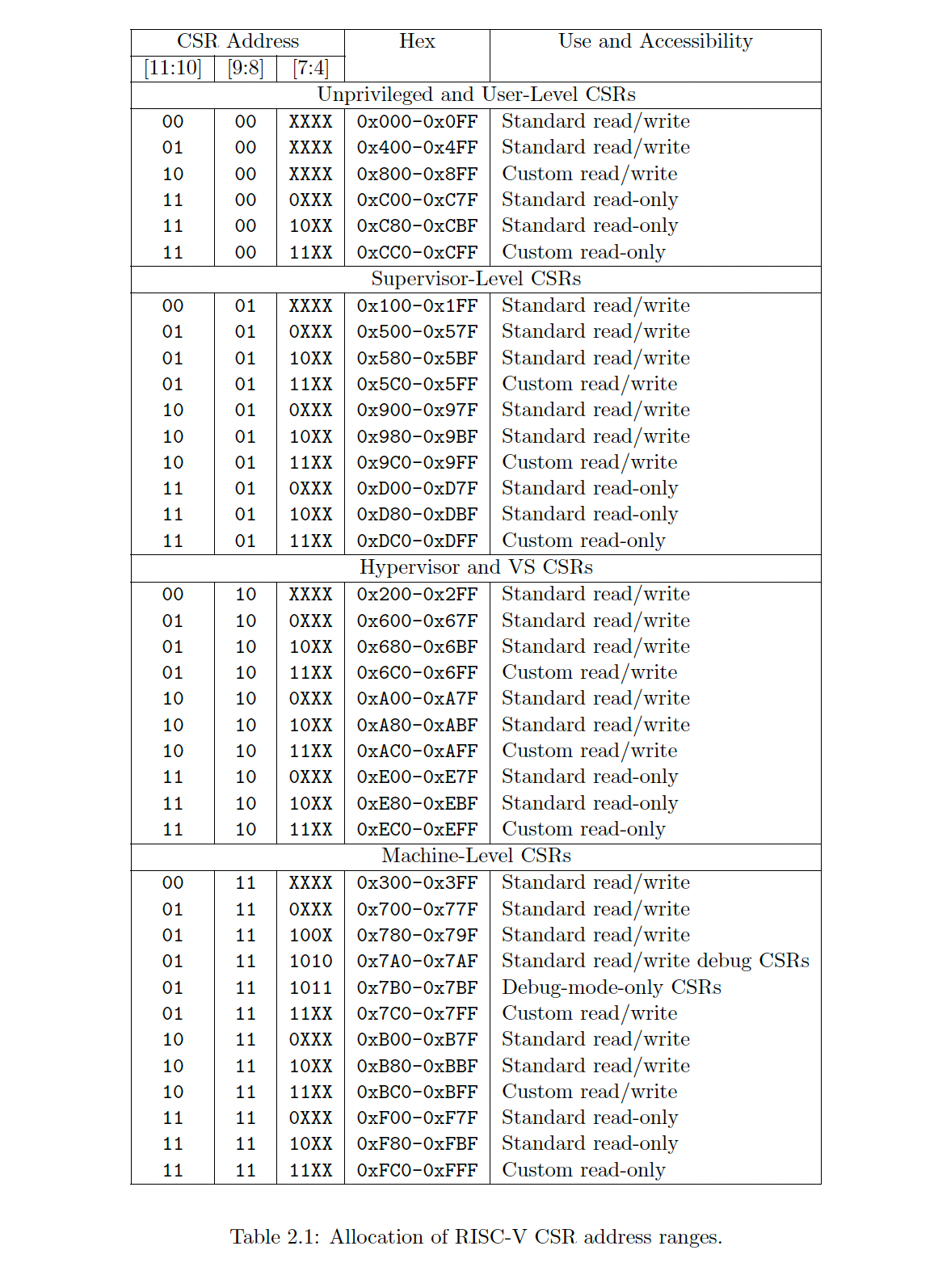

- CSR寄存器 Control and Status Registers (CSRs)

- CSR寄存器编址约定:特权等级划分、读写属性标识

- CSR地址映射表

- CSR寄存器读写属性

- Machine-Level ISA

- machine mode读写的寄存器,如mhartid、mstatus、mtvec、mcause

- machine特权指令,如ecall(所有模式)、mret、sret、wfi(所有模式、U模式可选)

- 复位、NMI发生后hart状态

- PMA物理内存属性,原子、order、一致性

- PMP物理内存保护机制和寄存器

- Supervisor-Level ISA

- Supervisor mode读写的寄存器,如sstaus、stvec、scause、satp

- Supervisor特权指令,如ecal、sret、sfence.vma

- Page-Based 32/39/48/57-bit Virtual-Memory Systems

- Hypervisor Extension

- hypervisor 虚拟化读写的寄存器,如hstatus、vstvec、vepc

- hypervisor特权指令,load/store、fence

特权模式的软件视角

-

RISC-V指令架构可以运行的3种软件栈分层

-

特权模式划分

所有硬件必须提供M-mode,因为它拥有访问整个机器的能力,最简单的RISC-V实现只有M-mode,但是不能抑制恶意APP。

未扩展前,不支持hypervisor模式

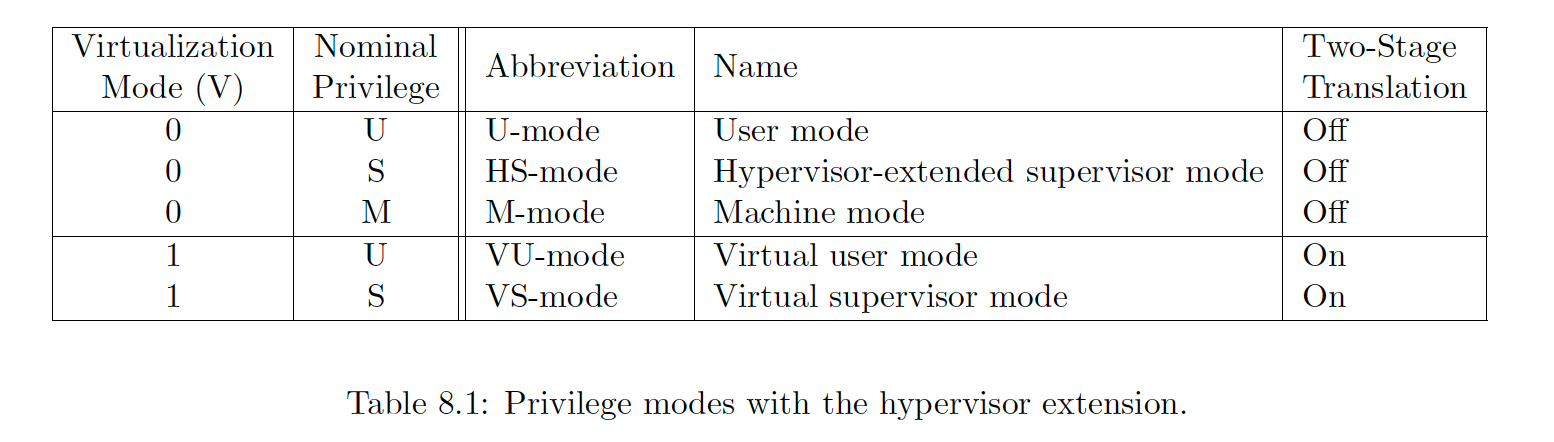

hypervisor扩展模式,V标识当前hart是否处于虚拟化模式

-

debug mode

通常RISC-V实现包括一个debug mode来支持片外调试或者制造测试。D-mode可认为是一个额外的特权模式,它甚至比M-mode拥有更多访问能力。调试模式会保留一些只能在D-mode访问的CSR寄存器。

Control and Status Registers (CSRs)

CSR地址映射编码约定

RISC-V ISA使用12bits编码空间定义了最多4096个CSRs,其中[11:10]用于表示读写属性,[9:8]用于表示对应的特权等级,剩余[7:0]作为内部编码。

| [11:10] | [9:8] | [7:0] |

|---|---|---|

| 读写属性:读写(00/01/10),只读(11) | 特权等级:U(00)/S(01)/H(10)/M(11) | 内部编码 |

CSR访问异常类型

- 访问不存在的CSR会引发illegal instruction exception

- 访问不适当特权级别的CSR也会引发illegal instruction exception

- 写入只读寄存器也会引发illegal instruction exception

- 读写寄存器也可能包含一些只读的位,在这种情况下写入只读位会被忽略

寄存器字段规范

-

WPRI (Reserved Writes Preserve Values, Reads Ignore Values )

写时保护保留值,读时忽略值,以备将来使用。软件应忽略从这些字段读出的值,在修改其他字段时,应该同时保留这些字段的值。为了向前兼容,实现不提供这些字段时必须将它们硬连线为零。在寄存器描述中标记为WPRI。 -

WLRL(Write/Read Only Legal Values )

只允许读写合法值。软件只能向这些字段写入合法值,而且只有最后一笔是合法的写操作或者复位时,读取的值才是合法值。当写入不支持的值时,根据具体实现来决定是否引发指令异常。 -

WARL(Write Any Values, Reads Legal Values )

写入任意值,总是返回合法值。字段规定合法值的范围,但是允许写入任意值,同时保证返回值是合法值。

Machine Level ISA

重要寄存器

mtvec

mcause

mepc

supervisor Level ISA

Hypervisor Level ISA

缩写

| 缩写 | 全拼 |

|---|---|

| CSR | Control and Status Registers |

浙公网安备 33010602011771号

浙公网安备 33010602011771号