深入浅出计算机组成原理学习笔记: 第十三讲

一、上节回顾

上一讲,我们看到了如何通过电路,在计算机硬件层面设计最基本的单元,门电脑,我给你看的门电路非常简单,只能做简单的“与(AND)”“或(OR)”“NOT(非)”和“异或(XOR)”,

这样最基本的单比特逻辑运算。下面这些门电路的标你需要非常熟悉,后续的电路都是由这些门电路组合起来的。

这些基本的门电路,是我们计算机硬件端的最基本的“积木”,就好像了高积木里面最简答的小方块,看似不起眼但把他们组合起来满最终可以搭出一个星际大战里面千年年隼这样的大玩意儿。

我们今天包含十亿级别晶体管的现代 CPU,都是由这样一个一个的门电路组合而成的。

二、异或们和半加器

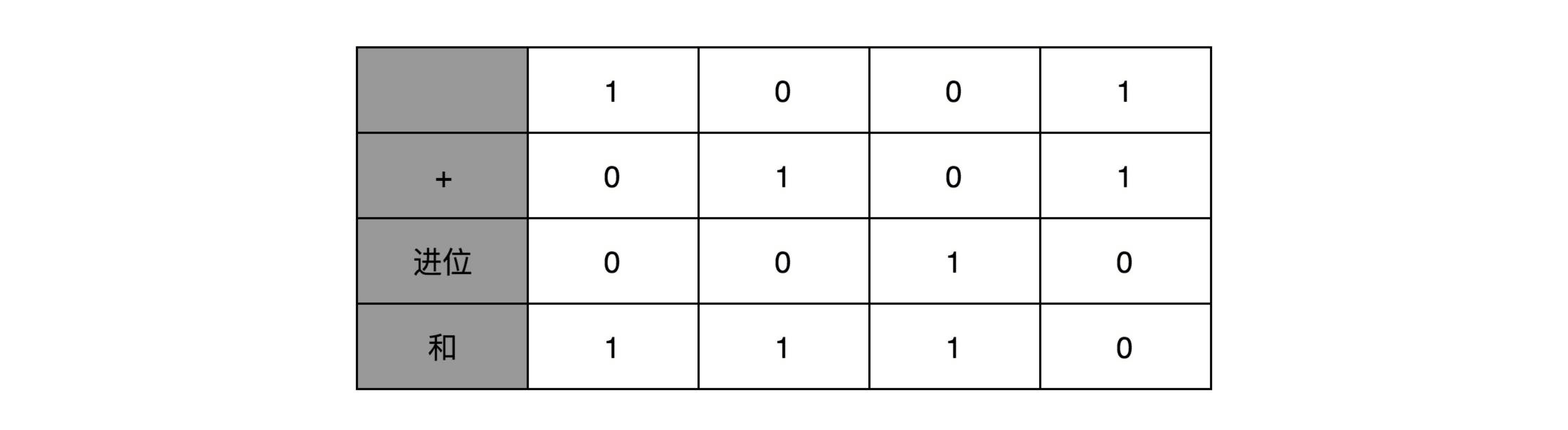

1、2个8位整数的加法

1、2排8个开关加法得到结果

2、需要1排8位的开关

2、其实加法器就是像一个办法把三排开关电路连起来

3、我们人在计算加法的时候一般会怎么操作

4、为什么我们需要异或?

其实异或就是一个最简单的整数加法,所需要使用的基本电路

5、进位

那这个就对应一个与门,也就是有且只有在加数和被加数都是1的时候,我们的进位才是1

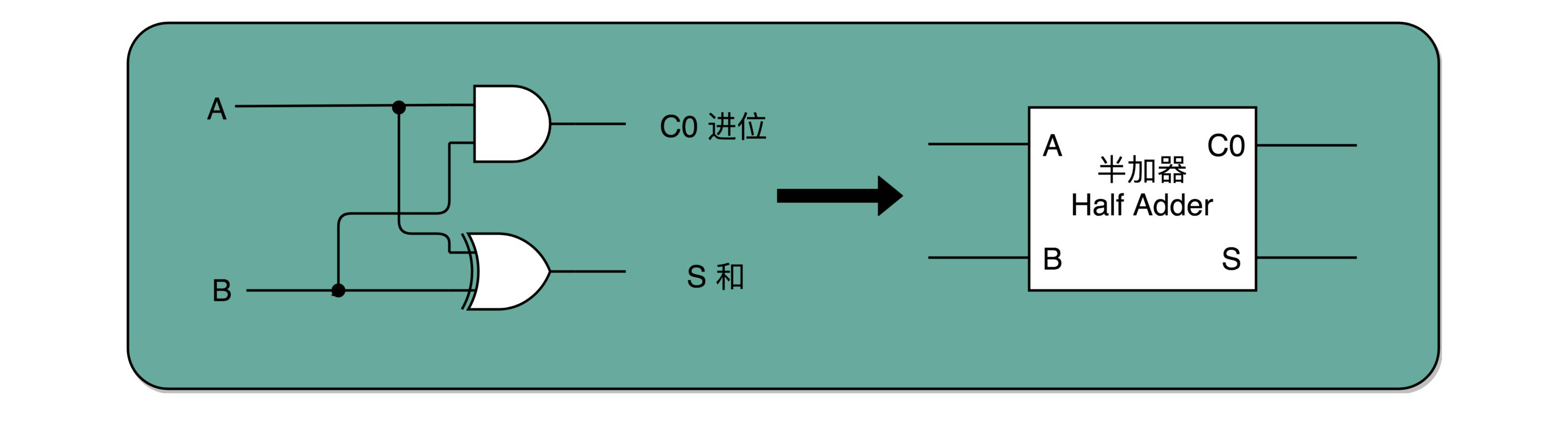

6、半加器

所以、通过一个异或们计算机出个位,通过一个与或门计算出是否仅为,我们就通过电脑算出了一位数的加法、于是、我们把两个门电路打包,给它取一个名字,就叫做半加器

7、半加器的电路演示

三、全加器

1、半加器存在的问题

1、解决了什么问题?

2、存在什么问题?

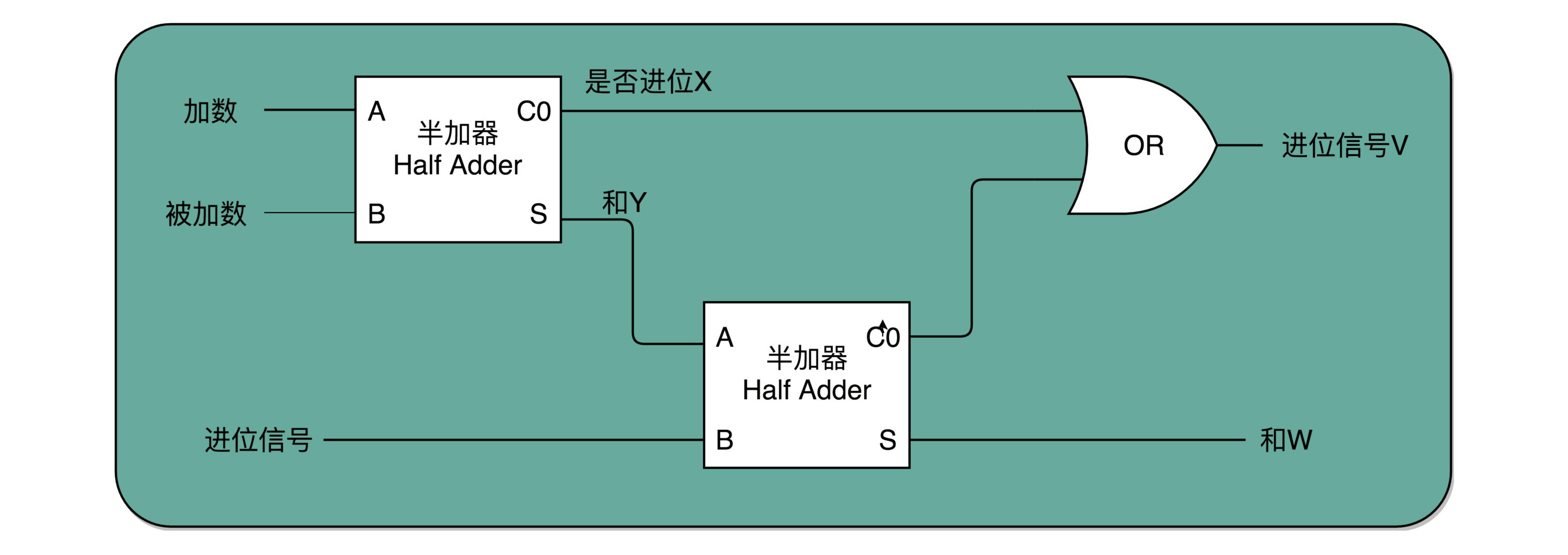

2、全加器就是两个半加器加上一个或门

1、工作原理

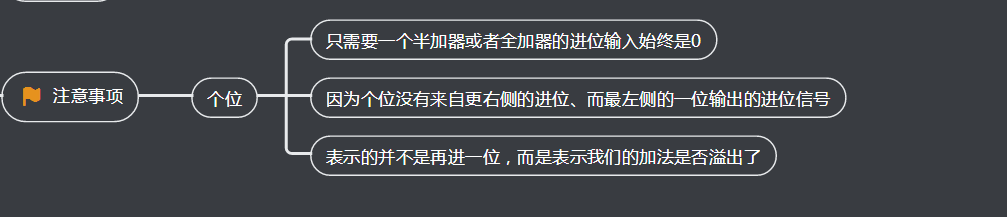

2、注意事项

3、全加器图解

4、8位加法器可以由8个半加器串联而成

我们在写程序的时候如何知道自己的计算机结果是否会溢出?

看到全加器的电路设计,相信你应该明白,在整个加法器的结果中,我们其实有一个电路的信号,会标识出加法的结果是否溢出。我们可以把这个对应的信号,

输出给到硬件中其他标志位里,让我们的计算机知道计算的结果是否溢出。而现代计算机也正是这样做的。这就是为什么你在撰写程序的时候,能够知道你的计算结果是否溢出在硬件层面得到的支持。

四、总结延伸

相信到这里,你应该已经体会到了,通过门电路来搭建算数计算机的一个小功能,就好像搭乐高积木一样

我们用两个门电路,搭出一个半加器,就好像我们拿两块乐高,叠在一起,变成一个长方形的乐高,这样我们就有了一个新的积木组件,柱子。

我们再用两个柱子和一个长条的积木组合一下,就变成一个积木桥。然后几个积木桥串接在一起,又成了积木楼梯。

当我们想要搭建一个摩天大楼,我们需要很多很多楼梯。但是这个时候,我们已经不再关注最基础的一节楼梯是怎么用一块块积木搭建起来的。

这其实就是计算机中,无论软件还是硬件中一个很重要的设计思想,分层。

从简单到复杂,我们一层层搭出了拥有更强能力的功能组件。在上面的一层,我们只需要考虑怎么用下一层的组件搭建出自己的功功能,而不需要下沉到更低层的其他组件。

就像你之前并没有深入学习过计算机组成原理,一样可以直接通过高级语言撰写代码,实现功能

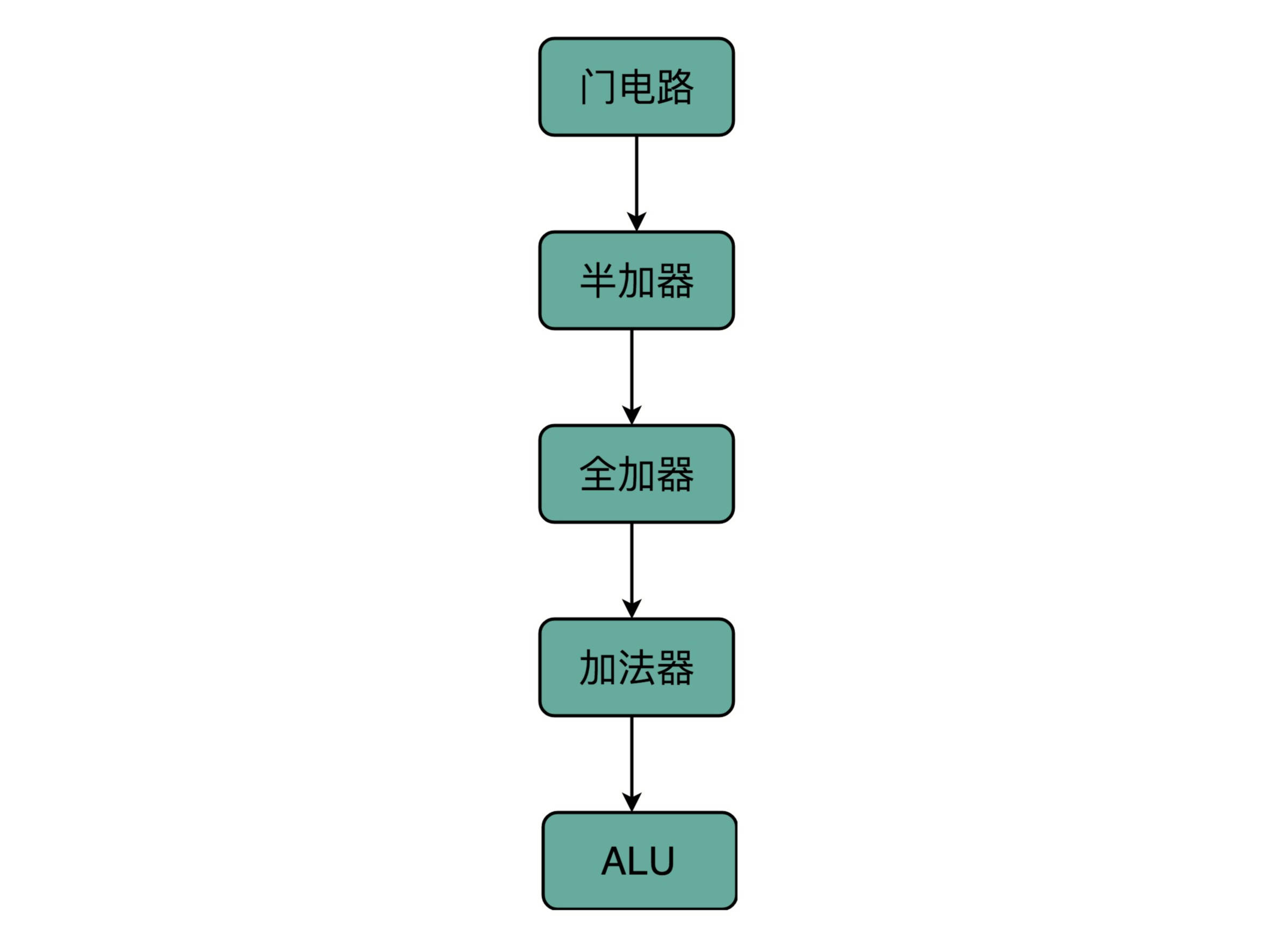

在硬件层面,我们通过门电路、半加器、全加器一层层搭出了加法器这样的功能组件。我们把这些用来做算术逻辑计算的组件叫作 ALU,也就是算术逻辑单元。当进一步打造强大的 CPU 时,

我们不会再去关注最细颗粒的门电路,只需要把门电路组合而成的 ALU,当成一个能够完成基础计算的黑盒子就可以了。

以此类推,后面我们讲解 CPU 的设计和数据通路的时候,我们以 ALU 为一个基础单元来解释问题,也就够了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号