0331-后悔做硬件了

之前接了一个 Vivado CPU 设计的活

我原本想的是就当作对往昔 CPU 设计的回忆和致敬,认真做一做。

但是因为各种原因,一直拖到现在。结果今天客户来找我催。

唉,这种滋味就是又愤怒,又懊悔,又自责,又担忧,还焦虑完不成,害怕丢单子。

也对自信心有一点点打击。

但是吧,我觉得“态度决定一切”,如果我好好的做,即使最后做不出来。我觉得也没什么大不了的。

实在不行就跟客户坦白,说我没有估算好工作量和时间,导致延期了。实在不行就减200。再不行就让他退1200。

我现在开始好好认真做,一切都来得及。

- 旧版项目的指令数约15条,要求的指令数40条,需要新增大量指令及相关的控制通路、数据通路,且需要调试验证。

- 伪指令,并非直接对应于处理器的实际机器指令,而是由汇编器在汇编过程中将其转换为一条或多条实际的机器指令。伪指令主要用于简化编程工作,提高代码的可读性和灵活性。在汇编阶段,已经完成处理,将其转化成若干条机器指令了。CPU里无需处理。

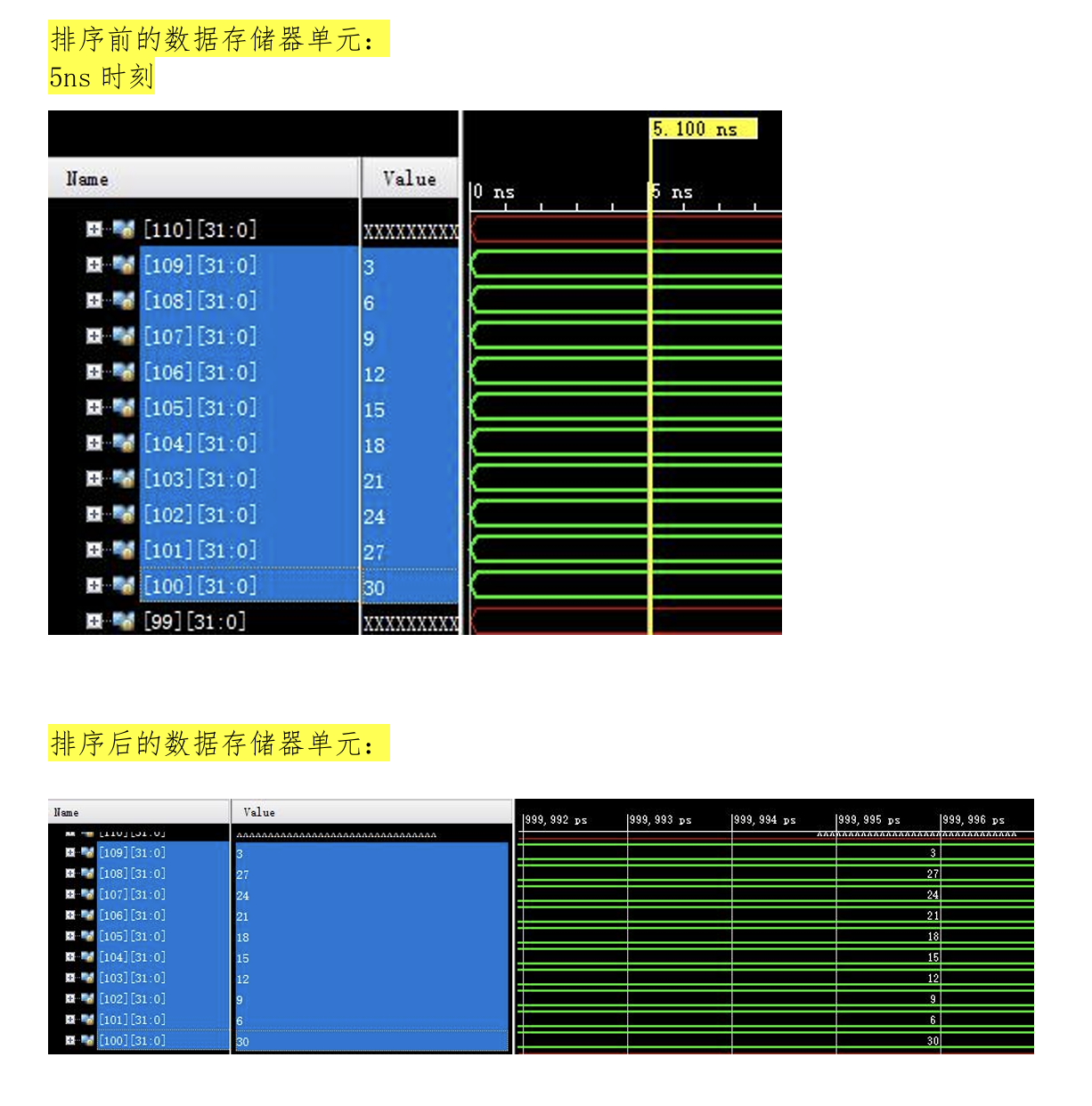

- 波形图类似于这样,(仅供参考)会显示出指定信号的高低电平。到最后完成,比如一个排序程序,在运行程序前后,分别会显示指定内存地址的值。运行前,会手动赋予一系列无序值。如果执行程序后,内存地址中的值变成按顺序排列的,那么就可以认为是汇编和CPU工作正常 。这个可以作为整个项目的验证结果。

浙公网安备 33010602011771号

浙公网安备 33010602011771号