[FPGA] 数字IC/FPGA 跨时钟域问题详解(1)同步与异步时钟

https://mp.weixin.qq.com/s?__biz=Mzk5MDkzNjU2OA==&mid=2247484247&idx=1&sn=a7a91e914b105e962e107743a4e0c651&scene=21&poc_token=HD4cwmijQS9EoxsA3rJWzMgcOC1XXd7RCbwMuydW

一、同步时钟还是异步时钟?

在数字系统中,时钟的属性包括:频率、相位及时钟源。

因此,区分同步时钟还是异步时钟的关键点在于各时钟的频率及相位关系是否固定、时钟是否同源(具备可预知性)。

1.1 什么是同步时钟?

所谓同步电路,即整个设计都使用了同一时钟源,且时钟之间的频率和相位关系都是事先预知的,如下述时钟:

- 同频同相

- 同频不同相(固定相位差):通常由时钟路径延迟导致的ClockSkew

- 同源不同频(整数倍频率比):分频器或同一PLL输出的整数倍多路时钟

需要注意的是,某些情况(下文会详解)即使是源端和目的端属于同步时钟,也需要进行跨时钟域处理以确保数据被正确传输。

同步设计的优势在于,EDA工具能够很方便地对全同步设计进行时序检查;另一方面,同步设计具备时钟边沿采样的特点,能够避免毛刺传播至整个电路。

1.2 什么是异步时钟?

所谓异步时钟,即时钟不同源(两个PLL的输出或来自于不同晶振的输出),或者是时钟同源但频率比为非整数倍的两个时钟为异步时钟(非整数频率比会导致两个时钟的相位关系不固定),如下述时钟:

- 不同源: 时钟由不同的晶振或PLL输出,相位关系不明确

- 同源不同频(非整数倍频率比):分频器或同一PLL输出的整数倍多路时钟

二、为什么会出现异步设计?什么时候需要进行跨域处理?

一句话总结:不得已而为之。

全同步设计的劣势主要体现在这两方面:

1、在功能复杂的数字设计中(如SoC系统),往往集成有各类低速模块(如Uart)与高速模块(如CPU、GPU),几乎不可能使用同一个时钟,多采用GALS(全局异步/局部同步)设计;

举个例子,某CPU内核的核心频率为1GHz,用于调试CPU内核的JTAG接口的频率一般不会超过20MHz,

因此必须在CPU和JTAG之间设计异步处理电路(使1GHz与20MHz这两个时钟域可以安全地交互调试信息)。

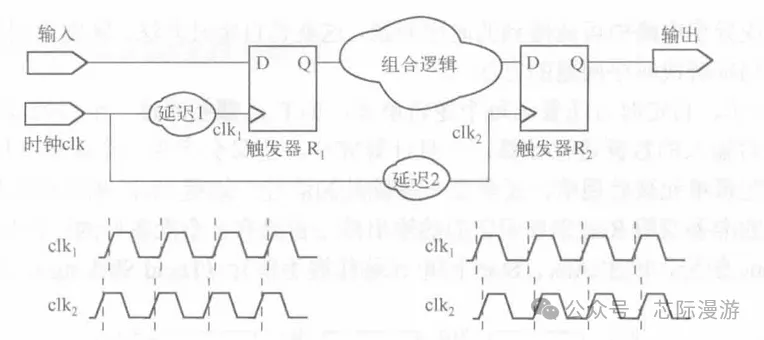

2、Clock Skew(时钟偏斜)问题,即时钟边沿到达各Flip-Flop的时间有所不同(如下图中clk1和clk2所示,CTS(时钟树综合)可解决该问题,但需要向低延迟的时钟路径插入延迟单元,不可避免地会增加面积和功耗);

3、同源不同频(整数倍频率比)情况,看起来没有跨时钟域。

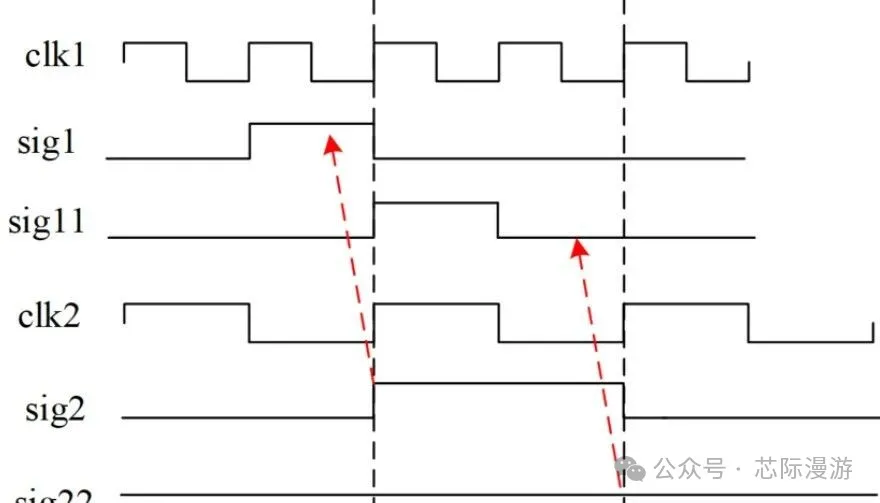

然而,当出现下图所示的慢时钟采样快时钟时,快时钟过快反转导致慢时钟无法正确采样到快时钟的数据。这时候也需要进行处理,将快时钟信号展宽,使慢时钟域能够正确采样。

需要明确的是,跨时钟域处理的核心目标是保证数据能够正确从源端传输到目的端。

下一篇文章,我们将会围绕 亚稳态问题 进行讲解。

浙公网安备 33010602011771号

浙公网安备 33010602011771号