RFSOC+VU13P在无线电信号大带宽采集存储中的技能应用分析

一、技术背景

随着无线电通信、雷达探测、电子对抗等领域的快速发展,对无线电信号的分析精度和处理效率提出了前所未有的要求。其中,大带宽无线电信号的采集与存储是核心环节之一,直接决定了后续信号分析、特征提取及数据回溯的有效性。传统的信号采集存储方案往往面临“带宽瓶颈”与“存储压力”的双重挑战——要么难以实现超高带宽信号的实时采集,要么在采集后无法完成高速可靠的存储,导致数据丢失或分析滞后。

在这一背景下,基于异构计算架构的解决方案逐渐成为主流。Xilinx的射频系统级芯片(RFSOC)与VU13P可编程逻辑器件(FPGA)的组合,凭借RFSOC集成的高性能模拟前端与VU13P强大的逻辑处理能力,为大带宽无线电信号的采集存储提供了全新的技术路径,能够有效突破传统方案的性能限制,满足困难场景下的应用需求。

二、报告目的与范围

本报告旨在系统分析RFSOC+VU13P组合在无线电信号大带宽采集存储中的科技应用价值。报告将从核心组件技术特性出发,深入探讨该组合方案的技术优势、实现原理、关键技术突破点,结合实际应用场景验证其可行性,并针对现有困难提出优化方向,为相关领域的科技选型与系统设计提供参考。

报告范围涵盖:RFSOC与VU13P的核心技术参数、大带宽信号采集存储的核心需求、组合方案的架构设计、关键技术实现、应用案例及性能对比分析等。

三、核心组件手艺特性解析

RFSOC+VU13P方案的性能优势源于两者的技术互补性——RFSOC承担“信号入口”角色,实现从射频到数字信号的高效转换;VU13P承担“数据中枢”角色,完成信号的高速处理与存储调度。两者的协同工作构建了“采集-处理-存储”的全链路高效架构。

3.1 RFSOC:射频信号采集的核心载体

RFSOC(Radio Frequency System on Chip)是Xilinx推出的集成射频前端与可编程逻辑的系统级芯片,其核心优势在于将射频模拟电路与FPGA逻辑单元、处理器内核高度集成,减少了外部链路损耗,提升了信号采集的带宽与精度。以典型的Zynq UltraScale+ RFSOC为例,其关键技术参数如下:

• 射频前端:集成多通道12位/14位高速ADC(模数转换器),单通道采样率最高可达5 GSps,承受7 GHz以下射频信号直接采样,无需外部混频器,简化了系统架构;

• 逻辑处理单元:内置UltraScale+ FPGA架构,具备大量查找表(LUT)、触发器(FF)及数字信号处理单元(DSP48E2),可实现信号的实时滤波、降采样、正交解调等预处理;

• 接口能力:提供高速串行接口(如JESD204B/C),支持ADC数据与FPGA逻辑单元的高速传输,数据速率可达10 Gbps以上。

在大带宽信号采集中,RFSOC的核心价值在于其高采样率ADC与低噪声射频前端的集成设计。传统方案中,射频信号需经过“天线-混频器-放大器-ADC”的多环节外部链路,易引入噪声与信号衰减,而RFSOC的直接射频采样能力可将信号链路缩短至“天线-ADC”,显著提升了大带宽信号的保真度。

3.2 VU13P :高速数据处理与存储调度的核心引擎

面向高端计算与高速数据处理的核心器件。其技术特性与RFSOC形成完美互补,重点解决大带宽数据的实时处理与存储瓶颈问题,关键参数如下:就是VU13P是Xilinx推出的UltraScale+系列FPGA开发板,搭载XCvu13P芯片,

• 逻辑资源:包含超过300万个LUT、600万个FF,以及数千个DSP48E2单元,支持大规模并行逻辑运算,可完成麻烦的信号处理算法与内容调度逻辑;

• 存储资源:内置大容量Block RAM(单芯片可达数百MB)与UltraRAM,支持高速数据缓存,减少外部存储的访问压力;

• 高速接口:协助PCIe 4.0、100G以太网、NVMe等高速接口,其中PCIe 4.0 x16接口信息速率可达32 Gbps,NVMe接口协助与高速固态硬盘(SSD)的直接连接,为海量数据存储提供通道;

• 扩展性:开发板提供丰富的外设接口与扩展插槽,支持与RFSOC通过JESD204C或高速串行总线连接,实现多芯片协同工作。

VU13P的核心优势在于其强大的并行处理能力与高速接口扩展能力。在大带宽信号存储场景中,RFSOC采集的高速数据流需经过实时处理(如数据压缩、格式转换)后才能高效存储,VU13P可经过并行逻辑架构同时完毕多通道资料的处理与存储调度,避免数据在传输过程中出现拥塞。

四、大带宽无线电信号采集存储的核心需求与技术挑战

4.1 核心业务需求

不同领域对大带宽无线电信号采集存储的需求虽存在差异,但核心诉求可归纳为以下四点:

1. 高带宽采集:需拥护1 GHz以上带宽信号的采集,部分雷达与电子对抗场景需达到5 GHz以上带宽;

2. 高保真存储:信号失真度需控制在0.1%以下,确保后续分析中信号特征的完整性;

3.实时性处理:信息从采集到存储的延迟需低于10 ms,避免高速数据流导致的缓冲区溢出;

4. 大容量扩展:单套系统需帮助TB级以上存储容量,且具备多设备级联扩展能力,满足长时间信号记录需求。

4.2 传统方案的手艺挑战

传统的大带宽信号采集存储方案主要分为“独立ADC+通用处理器”与“低端FPGA+普通存储”两类,均存在明显手艺瓶颈:

1. 带宽瓶颈:独立ADC与处理器之间的接口速率有限(如PCIe 3.0仅支持8 Gbps),无法匹配5 GSps以上采样率的数据流;

2.处理瓶颈:通用处理器采用串行运算架构,难以完成大带宽信号的实时滤波与数据压缩,易导致数据堆积;

3.存储瓶颈:普通存储接口(如SATA 3.0)速率仅为6 Gbps,无法满足高速数据流的写入需求,且存储延迟较高;

4.集成度瓶颈:多组件分散设计导致系统体积庞大,且外部链路引入的噪声降低了信号采集精度。

五、RFSOC+VU13P方案的架构设计与手艺优势

5.1 架构整体架构

RFSOC+VU13P方案采用“分层架构+协同调度”设计,将信号采集、预处理、处理、存储四个环节高效衔接,整体架构分为三层:

1. 信号采集层:由RFSOC承担,经过内置射频前端接收无线电信号,经ADC完成“射频-数字”转换,输出高速数字基带信号;同时通过RFSOC内置的FPGA逻辑完成信号的初步预处理(如增益控制、直流偏移校正);

2. 数据处理层:由VU13P承担核心角色,通过JESD204C接口接收RFSOC传输的高速数据流,完成实时信号处理(如正交解调、数字滤波、数据压缩),并通过内部缓存单元实现资料的临时存储与调度;

3.存储扩展层:基于VU13P的NVMe接口连接多块高速SSD,构建RAID阵列,实现海量信息的高速写入与安全存储;同时通过PCIe 4.0接口与上位机通信,支持数据的实时回传与后续分析。

此外,系统通过RFSOC内置的ARM处理器与VU13P的逻辑单元构建协同控制模块,建立采样率、存储策略、接口速率等参数的动态配备,确保系统在不同带宽场景下的自适应运行。

5.2 核心技术优势

相较于传统方案,RFSOC+VU13P组合在大带宽信号采集存储中展现出四大核心优势:

5.2.1 全链路高带宽贯通

体系利用三级高速接口实现带宽贯通:RFSOC内置ADC支持5 GSps采样率(14位精度下对应带宽2.5 GHz),通过JESD204C接口(速率16 Gbps)将数据传输至VU13P;VU13P经过内部高速总线(速率达40 Gbps)完成数据处理,再经过NVMe接口(单通道速率8 Gbps,多通道RAID阵列可达64 Gbps)写入SSD。全链路无带宽瓶颈,可支持5 GHz以下带宽信号的稳定采集存储。

5.2.2 并行处理提升实时性

VU13P的UltraScale+架构承受大规模并行运算,可将信号处理任务拆解为多个子模块(如滤波模块、压缩模块、存储调度模块),通过流水线方式并行执行。例如,在1 GHz带宽信号处理中,并行滤波模块可将信号延迟控制在2 ms以内,压缩模块(采用LZ77算法)可将数据量压缩至原大小的40%,显著降低存储压力,同时确保实时写入。

5.2.3 高集成度降低信号损耗

RFSOC将射频前端、ADC、FPGA逻辑、处理器集成于单芯片,VU13P通过高速串行接口与RFSOC直接连接,减少了外部线缆与连接器的使用,使信号链路损耗从传统方案的10%以上降至2%以下。同时,RFSOC的低噪声射频前端(噪声系数≤1.5 dB)与高分辨率ADC(14位),确保了大带宽信号的高保真采集。

5.2.4 灵活扩展满足多样化需求

系统协助两种扩展方式:一是横向扩展,通过多套RFSOC+VU13P单元级联,利用100G以太网搭建材料同步,可将采集带宽扩展至20 GHz以上;二是纵向扩展,利用增加SSD数量扩展存储容量,单套系统可支持8块SSD组成RAID 5阵列,存储容量达16 TB,且支持热插拔更换。

六、关键技术实现与方案优化

6.1 高速数据传输协议优化

RFSOC与VU13P之间的数据传输采用JESD204C协议,该协议是面向高速ADC/DAC的串行数据传输标准,相较于JESD204B,其支持更高的链路速率与多通道同步。为确保传输稳定性,方案从两方面进行优化:

1. 链路同步:通过VU13P的时钟管理单元(CMU)生成同步时钟信号,传输至RFSOC的ADC时钟接口,确保ADC采样时钟与JESD204C传输时钟的相位一致性,避免数据传输中的误码;

2.误码检测:在传输链路中加入CRC校验模块,每1024字节数据附加32位CRC校验码,VU13P接收端通过校验模块实时检测误码,误码率超过10^-12时触发链路重连,确保信息可靠性。

6.2 实时数据压缩算法优化

大带宽信号采集产生的海量素材会导致存储成本激增,方案基于VU13P的DSP资源,实现了改进型LZ77压缩算法,针对无线电信号的相关性特征进行优化:

1.自适应滑动窗口:根据信号的频谱特征动态调整压缩窗口大小(128字节~1024字节),对于平稳信号采用大窗口提升压缩比,对于突发信号采用小窗口确保实时性;

2.并行压缩架构:将数据流分为8路并行处理,每路对应独立的压缩核,利用VU13P的DSP48E2单元实现快速匹配与编码,压缩延迟控制在1 ms以内,压缩比可达2.5:1~3:1。

6.3 存储系统调度优化

为避免高速数据流写入存储时出现拥塞,方案基于VU13P设计了“三级缓存+动态调度”存储架构:

1. 一级缓存:利用VU13P的Block RAM构建,容量为16 MB,用于接收刚处理完成的数据流,实现数据的即时缓存;

2. 二级缓存:利用VU13P的UltraRAM构建,容量为256 MB,用于缓存待写入SSD的数据,通过FIFO机制避免数据溢出;

3. 动态调度:基于SSD的写入状态(空闲/忙碌)调整信息传输速率,当多块SSD同时空闲时,采用轮询方式分配素材,确保存储带宽最大化。

七、应用案例与性能验证

7.1 电子对抗场景应用

某电子对抗架构需对敌方雷达信号进行大带宽采集与存储,要求采集带宽3 GHz,采样率6 GSps,存储容量8 TB,延迟≤5 ms。采用RFSOC+VU13P方案后,系统实现如下性能:

• 采集精度:信号失真度0.08%,优于传统方案的0.5%;

• 存储速率:通过4块NVMe SSD组成RAID 0阵列,写入速率达32 Gbps,满足6 GSps采样率下的数据流写入需求;

• 延迟表现:从信号采集到存储完成的总延迟为3.2 ms,低于需求阈值;

• 连续工作时间:支持连续8小时信号采集,存储数据量达8.6 TB,满足任务需求。

7.2 无线电监测场景应用

某无线电监测站需对复杂电磁环境中的多通道信号进行并行采集,要求帮助4通道同时采集,单通道带宽1 GHz,采样率2 GSps。方案通过2套RFSOC与1套VU13P级联实现,性能表现如下:

• 通道同步性:4通道信号的时间同步误差≤1 ns,确保多通道信号的关联性分析;

• 数据处理能力:VU13P同时完成4通道信号的滤波与压缩,处理延迟≤1.5 ms;

• 扩展性:通过增加RFSOC单元,可将通道数扩展至8通道,带宽提升至8 GHz,无需更换核心器件。

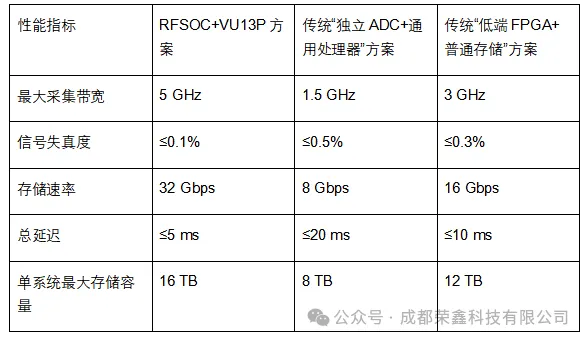

7.3 与传统方案的性能对比

八、现存疑问与优化方向

8.1 现存挑战

1. 功耗与散热问题:RFSOC与VU13P在高负载运行时(如5 GSps采样率),总功耗达150 W以上,需配备复杂的散热系统,限制了其在嵌入式场景中的应用;

2.成本较高:单套RFSOC+VU13P核心器件成本超过5万元,相较于传统方案的2万元,成本提升显著,不利于中小规模应用推广;

3. 软件开发复杂度高:方案需同时进行RFSOC的嵌入式开发、VU13P的FPGA逻辑开发及上位机协同开发,对开发团队的技术能力要求较高。

8.2 优化方向

1. 低功耗优化:采用动态电压频率调节(DVFS)手艺,根据信号带宽动态调整RFSOC与VU13P的工作频率与电压,在低带宽场景下将功耗降至80 W以下;同时采用高效散热材料(如石墨烯散热片),简化散热系统结构;

2. 成本控制:针对中低带宽场景,推出“简化版方案”——采用入门级RFSOC(如Zynq 7000系列)与中端FPGA组合,将核心成本降至2.5万元以内,满足中小规模应用需求;

3. 开发工具链优化:基于Xilinx Vitis开发平台,构建“采集-处理-存储”一体化开发模板,集成常用算法IP核(如滤波、压缩),降低软件开发难度,将开发周期从6个月缩短至3个月以内。

九、结论

RFSOC+VU13P方案通过“高集成度采集+并行化处理+高速化存储”的协同架构,实用突破了传统方案在大带宽无线电信号采集存储中的带宽、实时性与保真度瓶颈。其核心优势在于RFSOC的直接射频采样能力与VU13P的高速处理存储能力的完美互补,能够满足电子对抗、无线电监测等高端领域的严苛需求。

尽管方案目前存在功耗较高、成本较贵等问题,但通过低功耗优化、成本控制与开发工具链完善,其应用场景将进一步拓展至无人机侦察、卫星通信等嵌入式领域。未来,随着RFSOC与FPGA工艺的持续升级,该方案有望在更大带宽(如20 GHz以上)、更高精度(如16位ADC)的信号采集存储中展现出更强的技术竞争力,成为大带宽无线电信号处理领域的主流解决方案。

成都荣鑫科技原创内容,欢迎技术交流及合作,盗者必追究

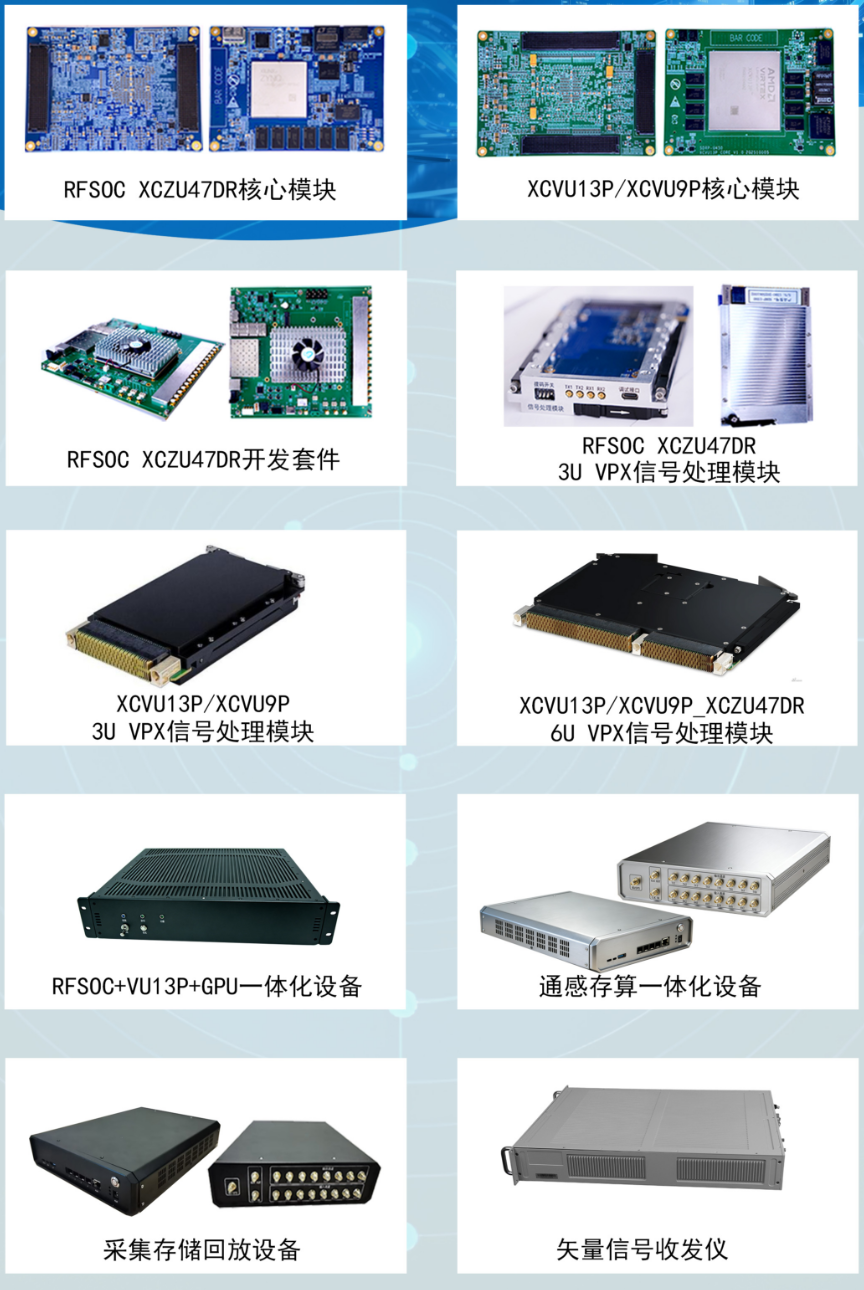

更多资料:RFSOC+VU13P在无线电信号大带宽采集存储中的技巧应用分析报告

浙公网安备 33010602011771号

浙公网安备 33010602011771号