深入解析:芯片制程进阶:动态功耗与频率的协同进化

芯片核心电学特性的重塑。其中,“制程越先进,动态功耗越低,支持的频率越高” 这一技巧规律,成为平衡芯片性能与能效的关键。本文将深入拆解这一规律背后的技术逻辑,揭示先进制程如何实现动态功耗与频率的协同优化。就是在半导体技术的赛道上,芯片性能的每一次飞跃都离不开制程工艺的突破。从 14nm 到 3nm,制程节点的不断缩小不仅是数字的变化,更

动态功耗与频率的核心关联

动态功耗是芯片在运算过程中,晶体管开关切换产生的功耗,其核心计算公式为 P = CV²fα(P 为动态功耗,C 为负载电容,V 为工作电压,f 为频率,α 为开关活动因子)。这一公式揭示了动态功耗与频率的直接关联:在其他条件不变时,频率越高,动态功耗越大。这就形成了芯片设计中的经典矛盾 —— 提升频率以增强性能,往往会导致功耗激增,进而触发发热问题限制性能释放。

先进制程的价值正在于打破这一矛盾。通过优化晶体管结构与电学参数,先进制程能够在降低动态功耗的同时,为更高频率创造物理条件。此种 “低功耗 - 高频率” 的协同效应,成为衡量制程先进性的核心指标,也是推动智能手机、服务器、AI 加速器等设备性能升级的底层动力。

先进制程降低动态功耗的技术路径

晶体管结构:从 “平面” 到 “立体” 的电容革命

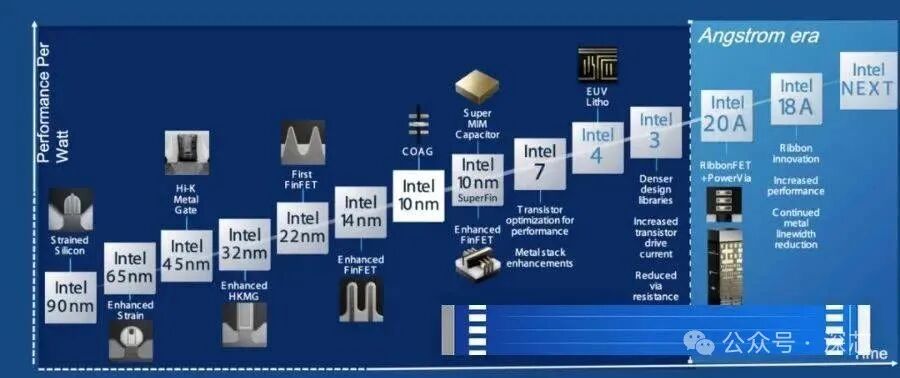

负载电容(C)是动态功耗公式中的关键变量,而电容大小与晶体管的物理尺寸直接相关。先进制程借助缩小晶体管尺寸、优化三维结构,实现了负载电容的显著降低。从平面晶体管到鳍式场效应晶体管(FinFET),再到全环绕栅极晶体管(GAAFET),每一次结构升级都在重塑电容特性。

在 7nm 及以上制程中,FinFET 凭借垂直鳍片结构减少了沟道与衬底的寄生电容;而 3nm 制程的 GAAFET 采用 “纳米片” 或 “纳米线” 设计,将导电沟道完全包裹在栅极中,进一步缩短了栅极长度,降低了栅极电容。台积电数据显现,3nm GAA 工艺的晶体管电容相比 5nm FinFET 降低约 20%,仅这一项优化就能使动态功耗减少 15%-25%。

电压优化:从 “高压强能” 到 “低压高效” 的突破

工作电压(V)对动态功耗的影响更为显著 —— 功耗与电压的平方成正比,电压降低 10%,动态功耗可降低约 19%。先进制程通过材料革新与工艺精度提升,实现了工作电压的持续下探。5nm 制程的典型工作电压为 0.7-0.8V,而 3nm 制程可降至 0.6-0.7V,2nm 制程有望进一步降至 0.5-0.6V。

材料技术的突破:高介电常数(High-k)栅极绝缘材料减少了栅极漏电流,使低压下仍能保持栅极控制能力;源漏区的硅锗(SiGe)应变手艺提升了载流子迁移率,让晶体管在低压下仍能快速开关。此外,先进制程的电压调节精度更高,凭借自适应电压缩放(AVS)技术,可根据芯片实时运算负载动态调整电压,避免冗余功耗。就是电压降低的背后

动态功耗降低如何支撑更高频率

散热冗余:为频率提升 “松绑”

芯片的最大工作频率受限于散热能力,而动态功耗的降低直接减少了单位频率下的发热量。例如,某款芯片在 10nm 制程下运行于 3GHz 时,动态功耗为 50W;升级至 5nm 制程后,相同频率下动态功耗降至 30W。这意味着在相同的散热设计(如散热片、风扇)下,芯片可将频率提升至 5GHz(30W×(5/3)≈50W),性能提升 67% 的同时,发热量仍控制在安全范围。

这种 “低功耗换高频率” 的逻辑在高端芯片中尤为明显。英伟达 H100 GPU 采用 4nm 制程,动态功耗相比前代 A100(7nm)降低 20%,使其在相同功耗下频率提升 30%,AI 算力突破 4PetaFLOPS,成为全球最快的 AI 加速器之一。

延迟优化:高频运行的物理基础

频率提升不仅需要散热冗余,更依赖晶体管的快捷响应能力。先进制程通过降低动态功耗,同步优化了晶体管的开关延迟与信号传输延迟,为高频运行提供了物理支撑。

晶体管的开关延迟(Tswitch)与充放电速度相关,动态功耗降低意味着电流路径更优化 —— 在相同电压下,载流子运动更高效,晶体管从导通到截止的切换时间更短。3nm 制程的晶体管开关速度相比 5nm 提升约 10%,可支持更高的时钟频率。同时,先进制程的金属布线更精细(如 3nm 采用 2nm 级布线宽度),并使用低电阻金属(如钴)替代传统铜布线,使信号传输延迟降低 15%-20%,避免高频下的信号同步问题。

技术演进的挑战与未来方向

随着制程节点向 2nm、1nm 逼近,动态功耗降低与频率提升面临物理极限挑战:量子隧穿效应导致漏电流增加,限制了电压进一步降低;原子级尺寸下,晶体管结构稳定性下降,电容优化空间收窄。为此,半导体行业正探索新材料与新结构:叉片晶体管(Forksheet FET)通过垂直堆叠增加沟道宽度,在缩小尺寸的同时降低电阻;互补场效应晶体管(CFET)将 N 型与 P 型晶体管垂直集成,进一步降低寄生电容。

此外,3D 集成技术(如 Chiplet)通过异构集成实现 “系统级功耗优化”—— 将高频核心与低功耗 IO 模块分开制造,在整体层面平衡动态功耗与频率需求。未来,先进制程的竞争将不仅是 “尺寸缩小”,更是 “结构创新 + 系统优化” 的综合较量,最终构建动态功耗与频率的持续协同突破。

浙公网安备 33010602011771号

浙公网安备 33010602011771号