深入解析:【车载以太网】以太网硬件

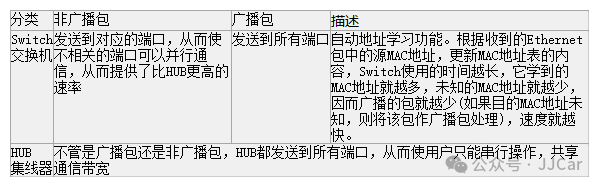

Switch

MAC地址与端口号。当Switch从某一端口收到一个包时(不讨论广播包),它要对地址表执行两个动作:就是Switch中有一个地址表,表中的每一项主要

否已在地址表中,如果没有,则将该MAC地址加到地址表中,这样以后就知道该MAC地址在哪一个端口;就是1、一是检查该包的源MAC地址

2、二是检查该包的目的MAC地址是否已在地址表中,如果该MAC地址已在地址表中,则将该包发送到对应的端口即可,如果该MAC地址不在地址表中,则将该包发送到所有其它端口(源端口除外),相当于该包是一个广播包。

每台计算机打开后,其上面的NIC(networkinterface controlle, 网络接口控制器,网卡)会定期发出空闲包或信号,交换机可据此得知其存在及MAC地址,所谓自动地址学习就此意。

Auto-aging指的是:若一定时间内未见已出现的MAC地址发出包,则将此MAC地址从“MAC—端口号表”中清除,此MAC地址重新出现时将会被当作新地址处理。

Switch与HUB

最大差别是:Switch会记忆哪些MAC地址挂在哪个端口上,也就是说Switch中有一个地址表,而HUB没有。

HUB

集线器是物理层(OSI第一层)设备,核心作用是将信号进行“接收-恢复放大-发送”。

双绞线、光纤在传输信号的时候,随着距离的增大,信号会减弱造成失真,借助集线器能够让信号传播更远的距离;同时集线器上有很多接口,能够扩大LAN的规模。

同一集线器上的所有设备共享带宽,如果设备数量过多的话,会造成链路拥堵,严重的会产生广播风暴。

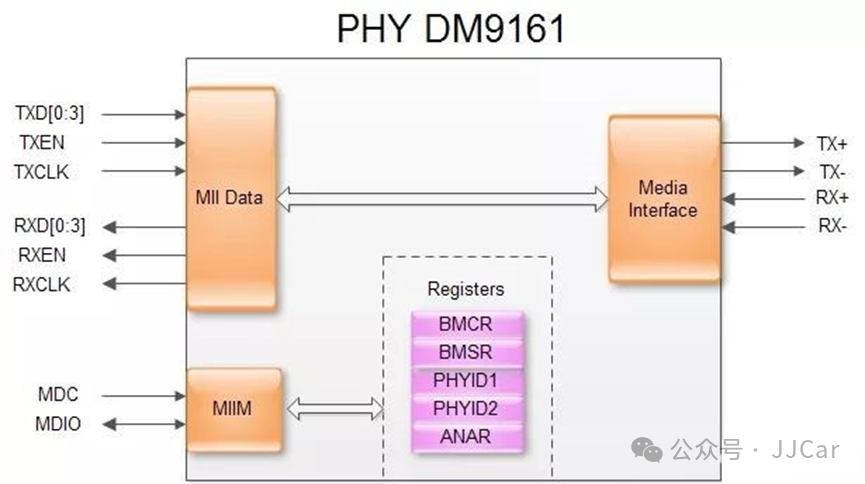

PHY

PHY(PhysicalLayer,物理层)是IEEE802.3定义的一个标准模块,STA(stationmanagement entity,管理实体,一般为MAC或CPU)通过SMI(SerialManage Interface)对PHY的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。一个PHY的核心结构如下图:

PHY是物理接口收发器,它实现OSI模型的物理层。IEEE-802.3标准定义了以太网PHY包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说都是数据,而不管什么地址、材料还是CRC),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把资料送出去。收资料时的流程反之。

通过PHY还有个重要的机制就是实现CSMA/CD的部分功能。它允许检测到网络上是否有资料在传送,要是有素材在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送材料出去。假如两个碰巧同时送出了信息,那样必将造成冲突。这时候,冲突检测机构能够检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付,两台主机之间出现第二次冲突概率很低。

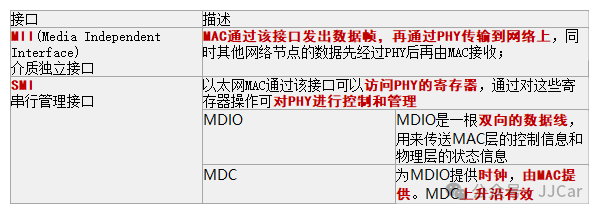

MAC与PHY的连接

MAC与PHY之间通过两个接口连接,分别为SMI接口和MII接口。

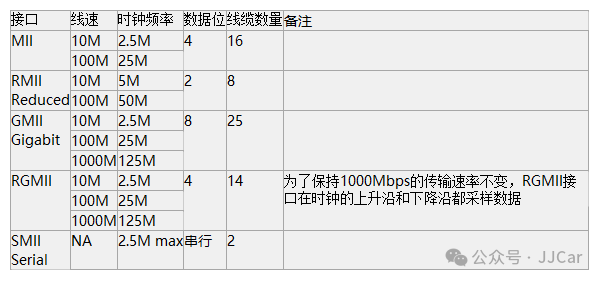

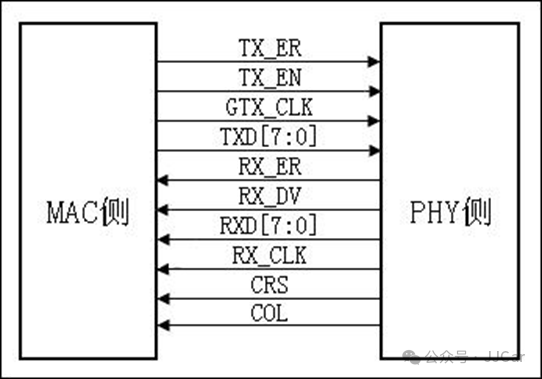

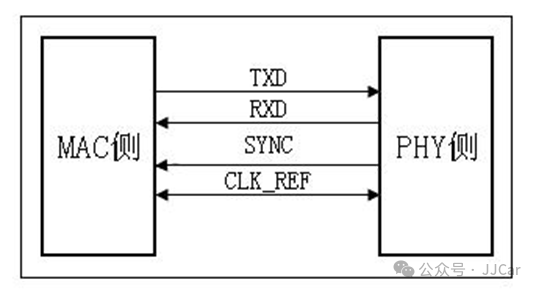

MII接口有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII等。这里简要介绍其中的MII和RMII,如下图所示。

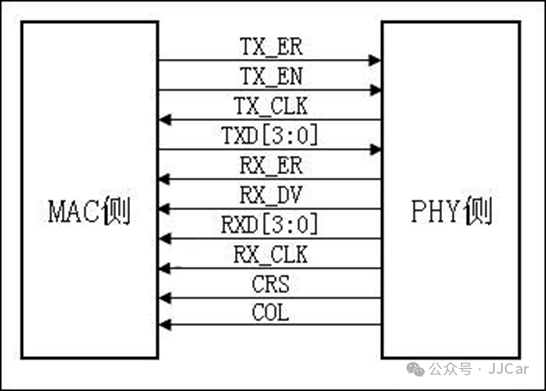

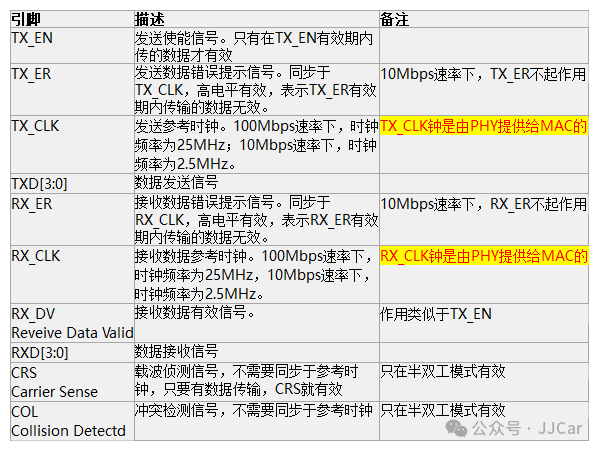

MII

MII支持2种速率10M和100M,利用16根线。其中CRS与COL只在半双工模式高效,而车载以太网固定工作在全双工模式下,故应该14根线。

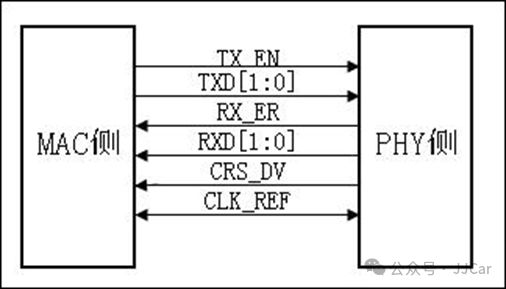

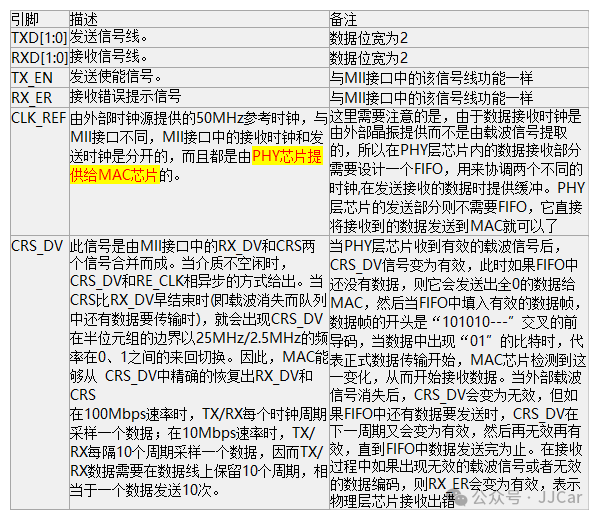

RMII

RMII(Reduced MII,精简MII)支持2种速率10M和100M,只有8根线。

GMII

RGMII

RGMII(ReducedGigabit Media Independent Interface)是ReducedGMII(吉比特介质独立接口)。同时兼容MII所规定的10/100Mbps工作方式,协助传输速率:10M/100M/1000Mb/s,其对应clk信号分别为:2.5MHz/25MHz/125MHz。RGMII数据结构符合IEEE以太网标准,接口定义见IEEE802.3-2000。

RGMII均采用4位素材接口,工作时钟125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。采用RGMII的目的是降低电路成本,使构建这种接口的器件的引脚数从25个减少到14个。

SMII

SMII(Serial MII,串行MII),只有4根线。

引脚 | 描述 |

TXD | 发送数据信号 |

RXD | 接收数据信号 |

SYNC | 收发数据同步信号,每10个时钟周期置1次高电平,指示同步。 |

CLK_REF | 所有端口共用的一个参考时钟,频率为125MHz。 为什么100Mbps速率要用125MHz时钟?因为在每8位素材中会插入2位控制信号,请看下面介绍。 |

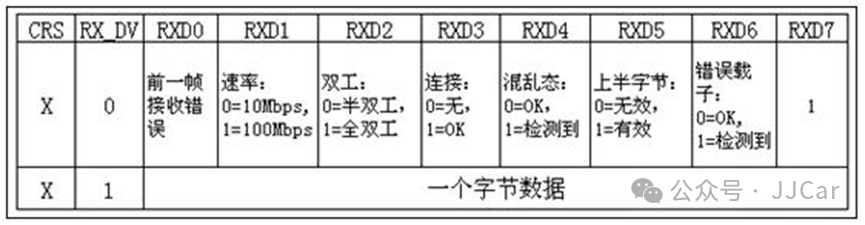

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的内容是:TXD[7:0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。当RX_DV为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。见下表:

当速率为10Mbps时,每一组数据要重复10次,MAC/PHY芯片每10个周期采样一次。MAC/PHY芯片在接收到素材后会进行串/并转换。

PHY的电源模式

为了进一步降低环境功耗,一些PHY都支持多种电源模式,主导包括正常模式、待机模式和睡眠模式。

以太网要正常建立连接,PHY必须处于正常模式,在PHY上电后,一般不会马上就工作在正常模式,而是待机模式。在待机模式下,PHY的ECU主电源被激活,功耗相对睡眠模式略高,睡眠模式是PHY工作功耗最低的模式,要是网络中暂时不得节点的特性,可使节点工作在睡眠模式,在睡眠模式下,此时节点可断电整个ECU,除了唤醒检测外,关闭所有内部能力。

SMI

SMI:串行管理接口(Serial Management Interface),也被称作MII管理接口(MII Management Interface),包括MDC和MDIO两条信号线。

MDIO是一个PHY的管理接口,用来读/写PHY的寄存器,控制PHY的行为或获取PHY的状态;MDC为MDIO献出时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns(2.5MHz max),最小正电平时间和负电平时间为160ns,最大的正负电平时间无限制。它与TX_CLK和RX_CLK无任何关系,典型周期是2.5M。

为MII总线接口定义的,MII用于连接MAC和PHY,囊括两种信号接口:就是MDIO原本

1. 一个数据接口用于MAC和PHY之间接收和发送以太网帧数据。

2. 一个PHY管理接口,即SMI,用于读写每个PHY的控制寄存器和状态寄存器,以达到控制PHY行为和监控PHY状态的目的。

MDIO是双向的,支持一个MAC连接最多32个PHY的连接方式,且MAC作为master,PHY作为slave。在写PHY寄存器的时候,由MAC驱动MDIO向PHY写入数据;在读PHY寄存器时,前半段由MAC驱动发送寄存器地址,后半段由PHY驱动回复寄存器的值。

MDC由MAC输出,对于PHY芯片则作为输入,以在上升沿触发MDIO的读写。MDC的时钟频率允许是DC-2.5MHz,即最小的时钟周期为400ns。

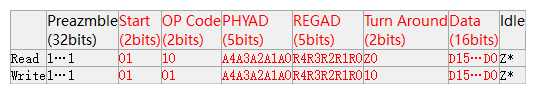

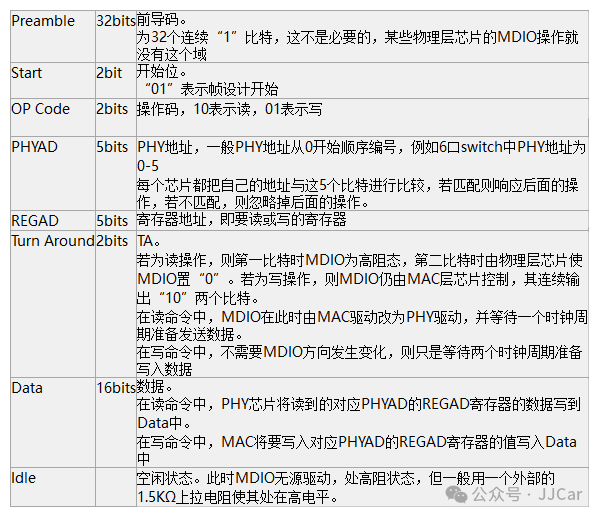

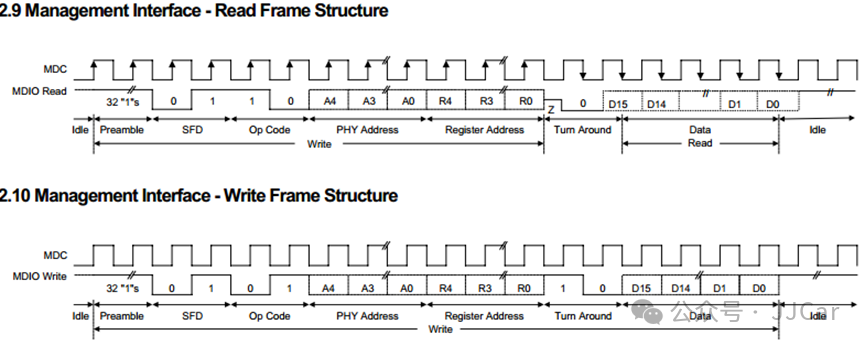

MDIO数据格式定义在IEEE802.3以太网标准中,如下图所示(数据传输顺序为从左至右):

上图中*表示高阻态。

为了保证PHY能准确采样,MAC写数据时,要求在MDC的上升沿之前把数据写到MDIO上,等待10ns以上再发出一个MDC的上升沿。而为了保证MAC能准确采样,当PHY向MDIO写资料时,该clock-to-data的delay时间范围可以是0-300ns(小于上面提到的400ns)。这个规定使接口的完成变得简单,但一定程度上限制了总线带宽。

MDI

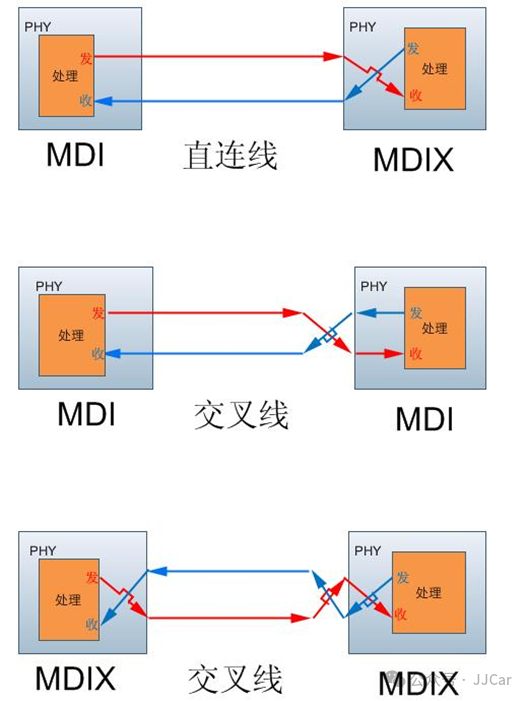

PHY与PHY之间的通信接口称为MDI(Medium Dependent Interface,媒介专用接口)。

MDI和MDIX 是两种接口,MDI和MDI,MDI-X和MDI-X用交叉线连接。MDI和MDI-X用直连线连接。相同端口用交叉线连接,不同端口用直连线连接。

现在的交换机等网络设备都有智能MDI/MDIX识别技术,也叫端口自动翻转(AutoMDI/MDIX),行自动识别连接的网线类型。用户不管采用直连线或者交叉网线,均允许正确连接设备。

浙公网安备 33010602011771号

浙公网安备 33010602011771号