一、微处理器系统原理及应用开发

一、数值与运算(熟悉即可)

1、数值的表示方法

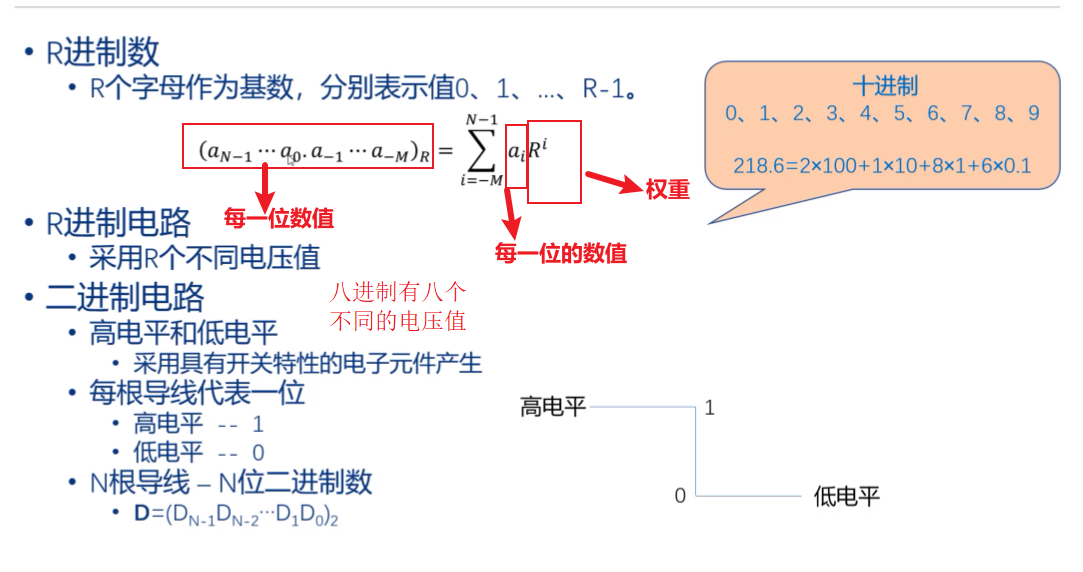

1.1 、所有数值的表示

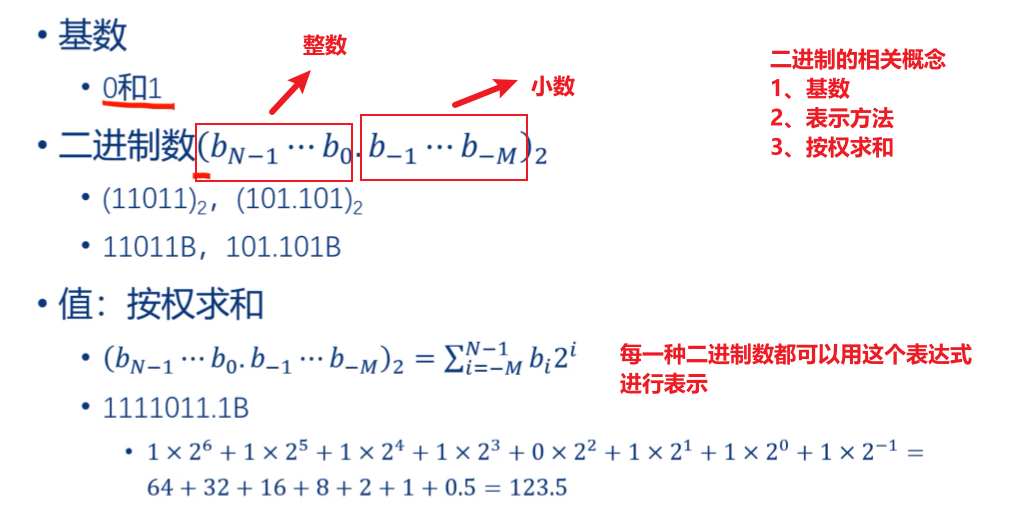

1.2 、二进制数的表示方法

2、数制之间的转换

2.1 、十进制转换二进制

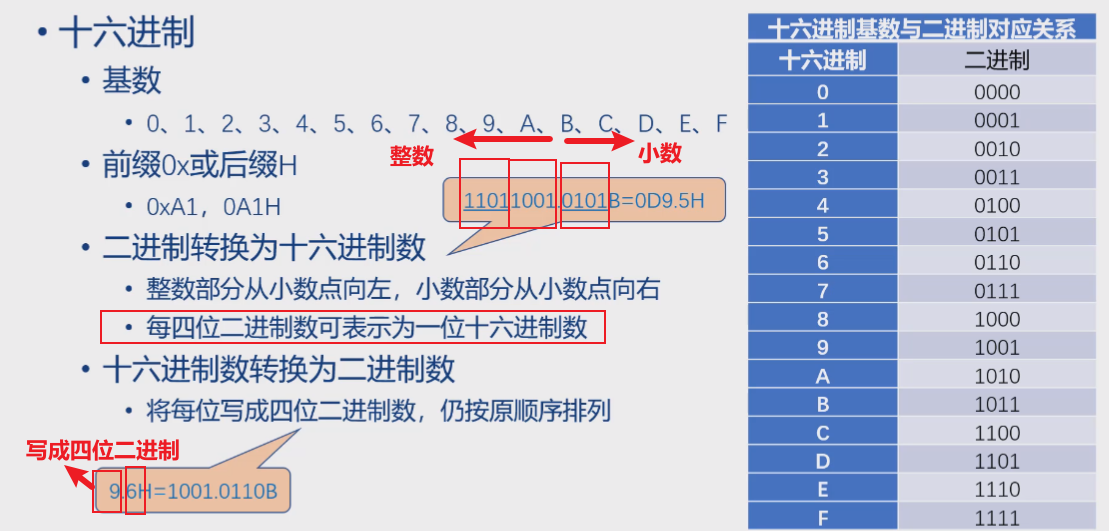

2.2 、二进制与十六进制之间的转换

3、算数运算

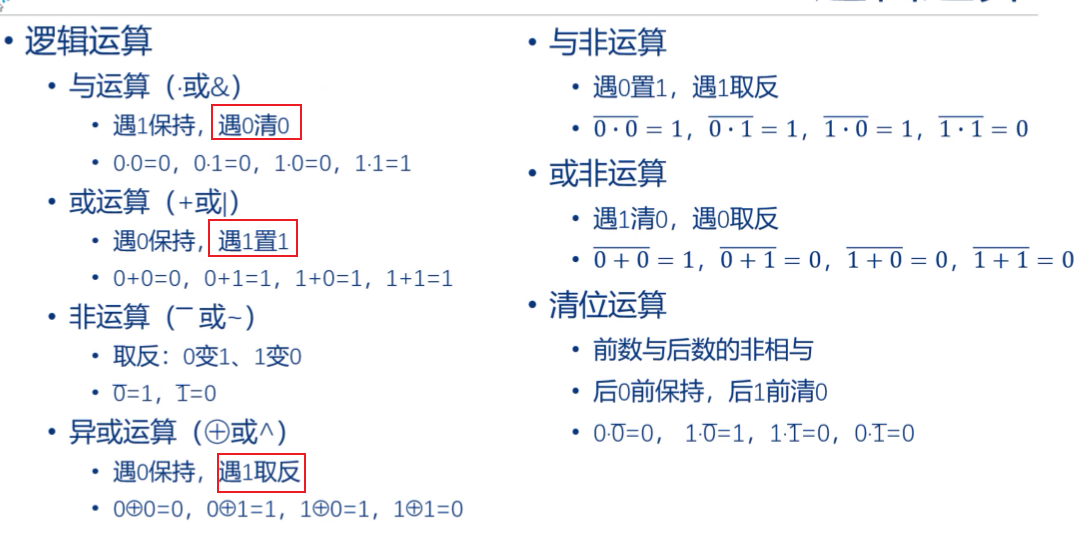

4、逻辑运算

二、二进制数字处理系统

三、 Cortex-M4内核

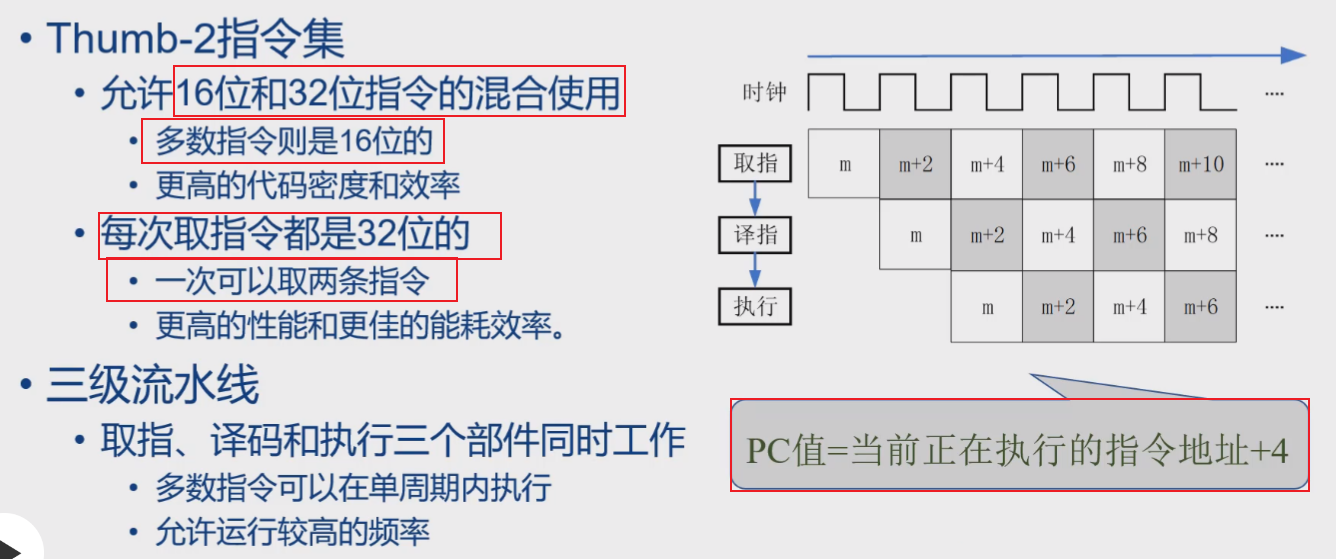

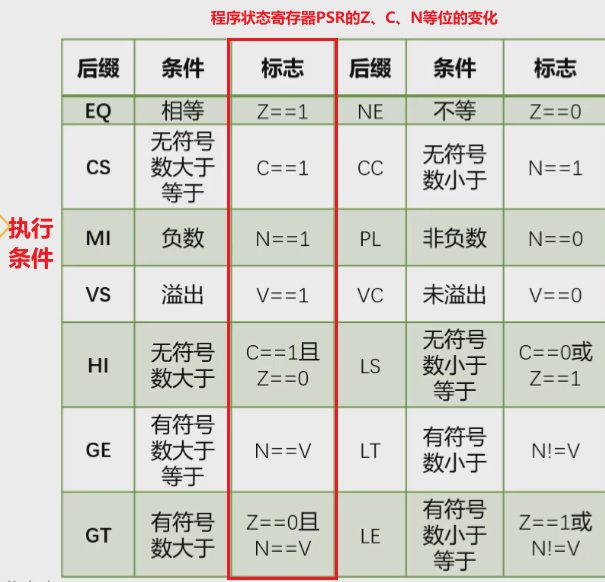

3.1 、指令集

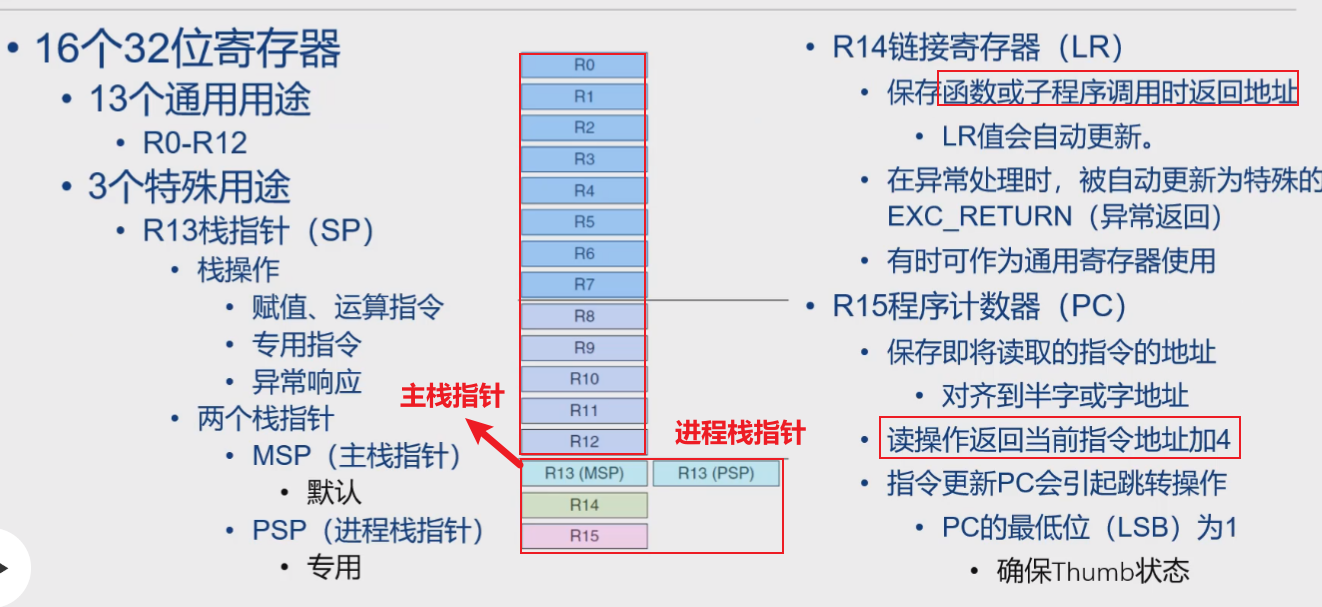

3.2 、寄存器组

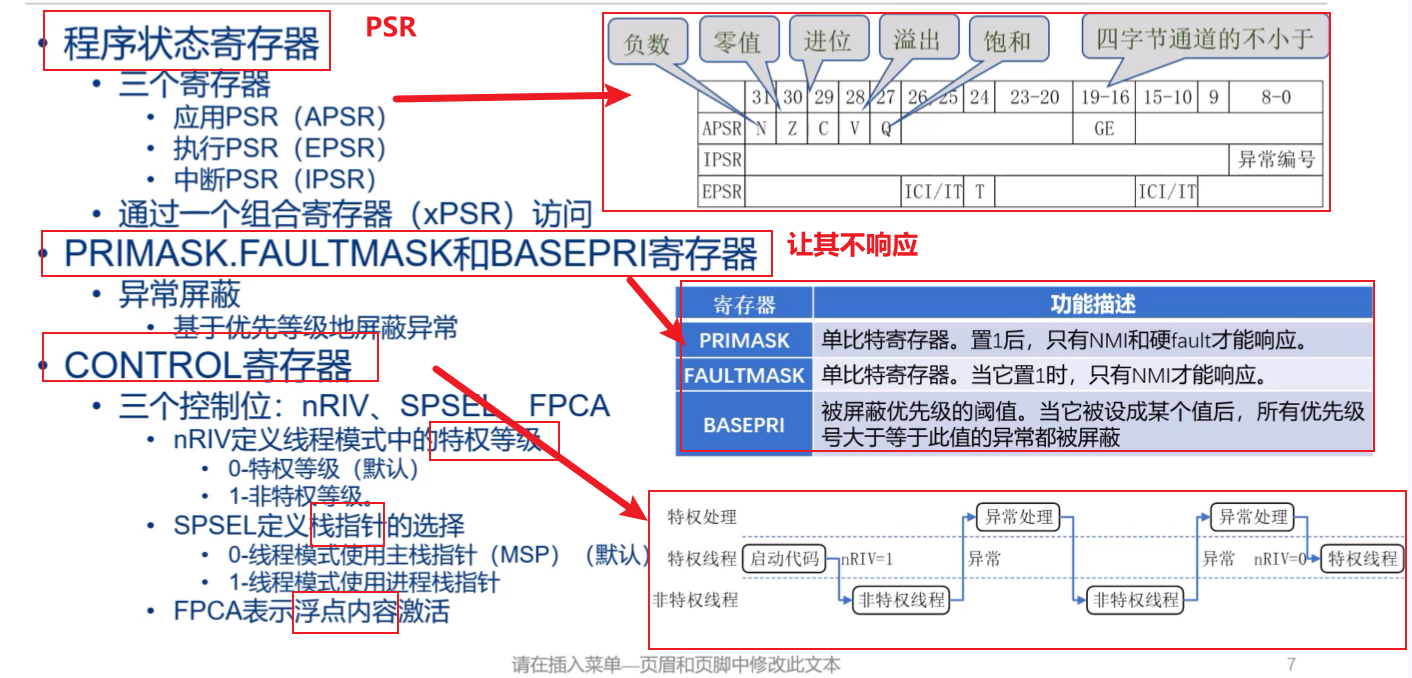

3.2.1 、特殊寄存器

3.3 、指令流水线

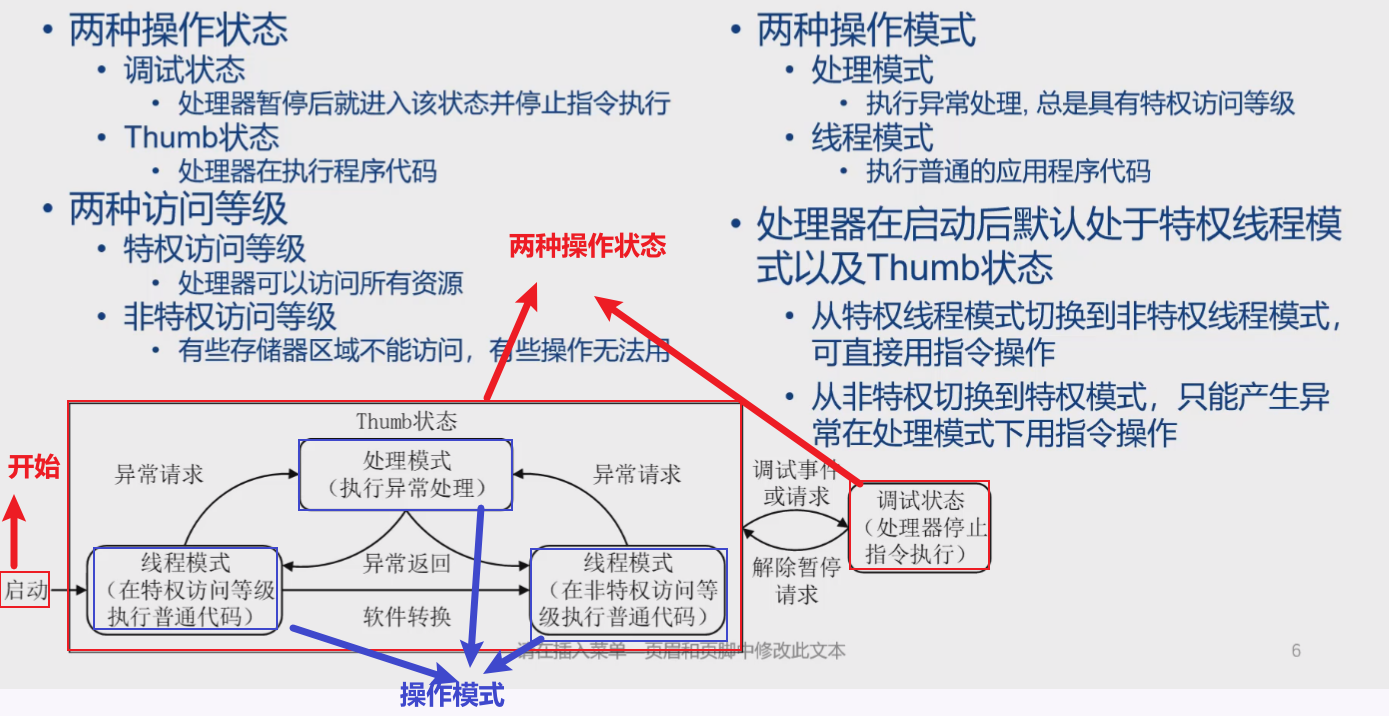

3.4 、内核的运行

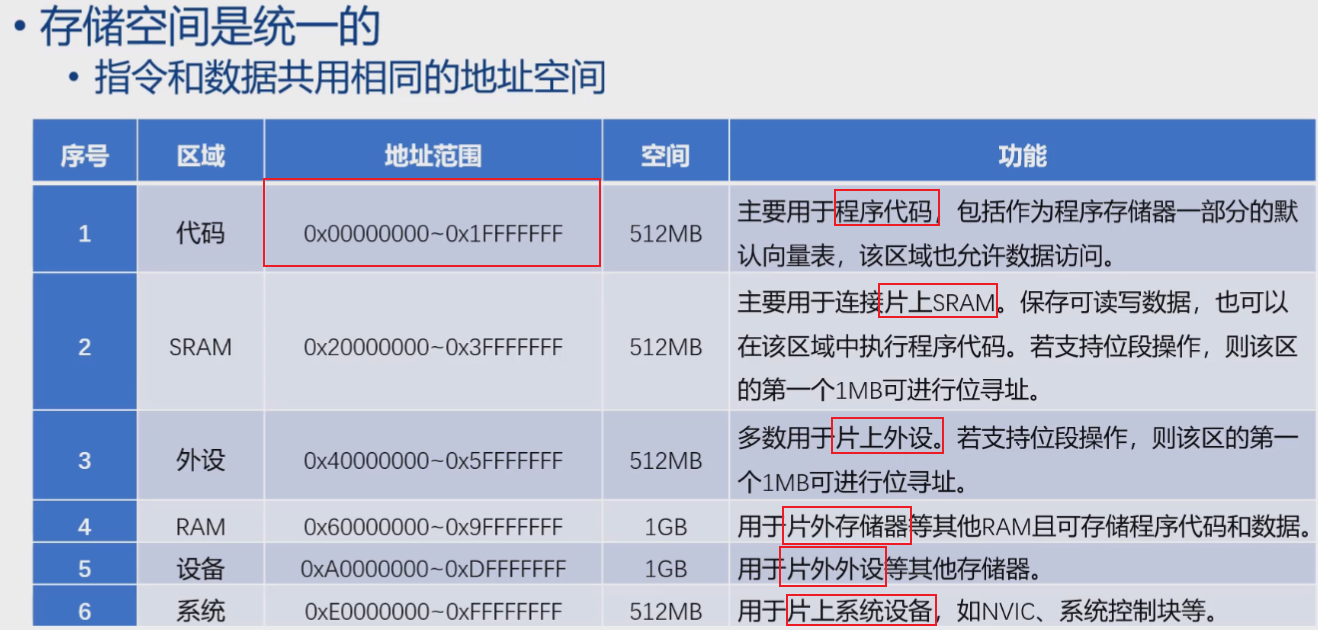

四、 Cortex-M4的存储系统

4.1 、存储空间

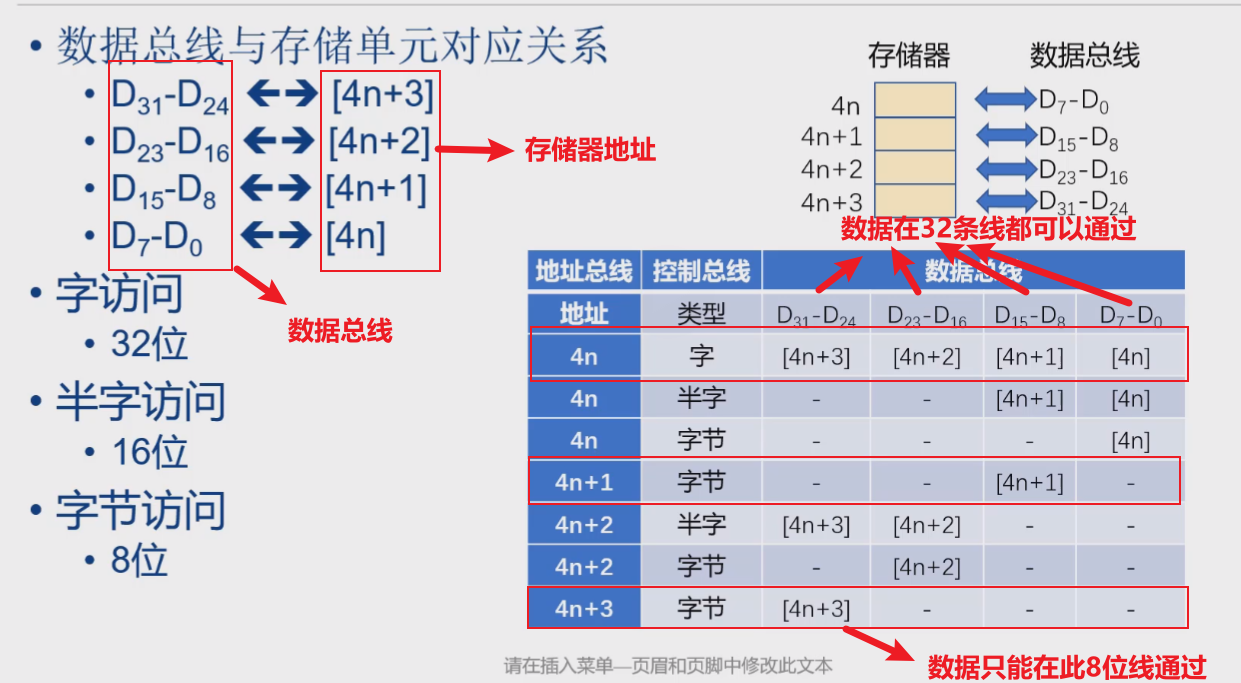

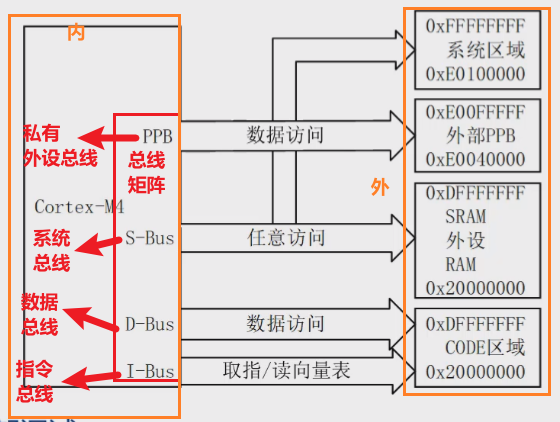

4.2 、总线访问

数据总线即是通向存储数据、程序的通道,数据总线通存储单元(存储地址)有对应关系,例如:4n+3的地址只能通过24-31的8位数据线传输。4n+2的地址只能通过16-23的8位数据线传输。

在数据总线中的数据,与CPU中存放的数据是不一样的。

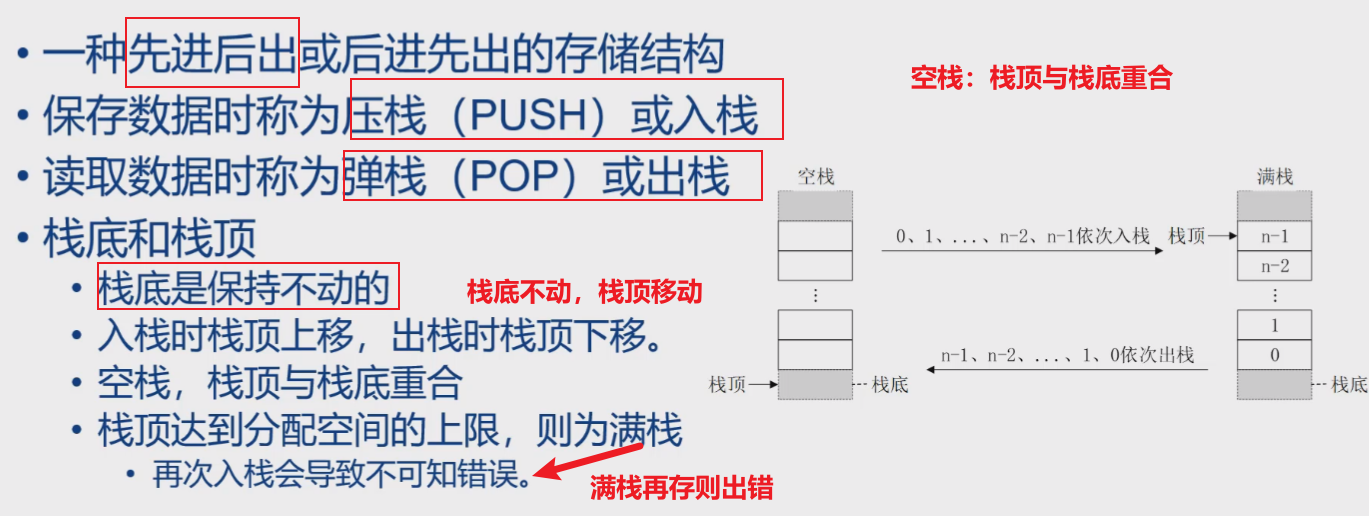

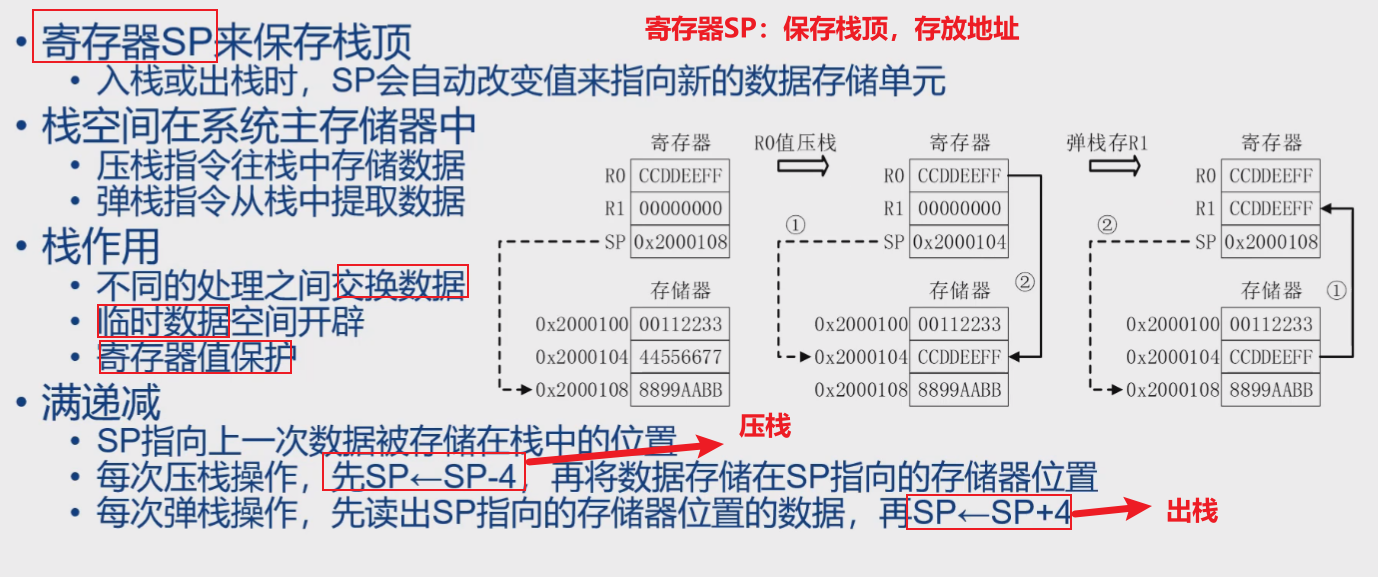

4.3 、栈存储结构

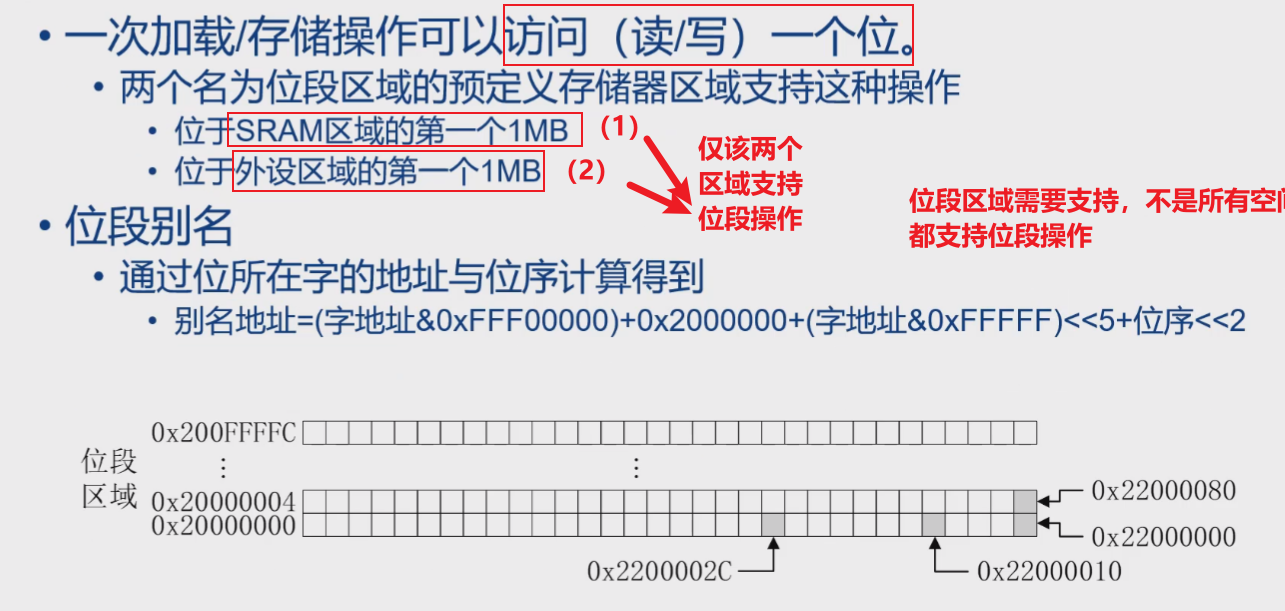

4.4 、位段操作

五、 Cortex-M4异常处理

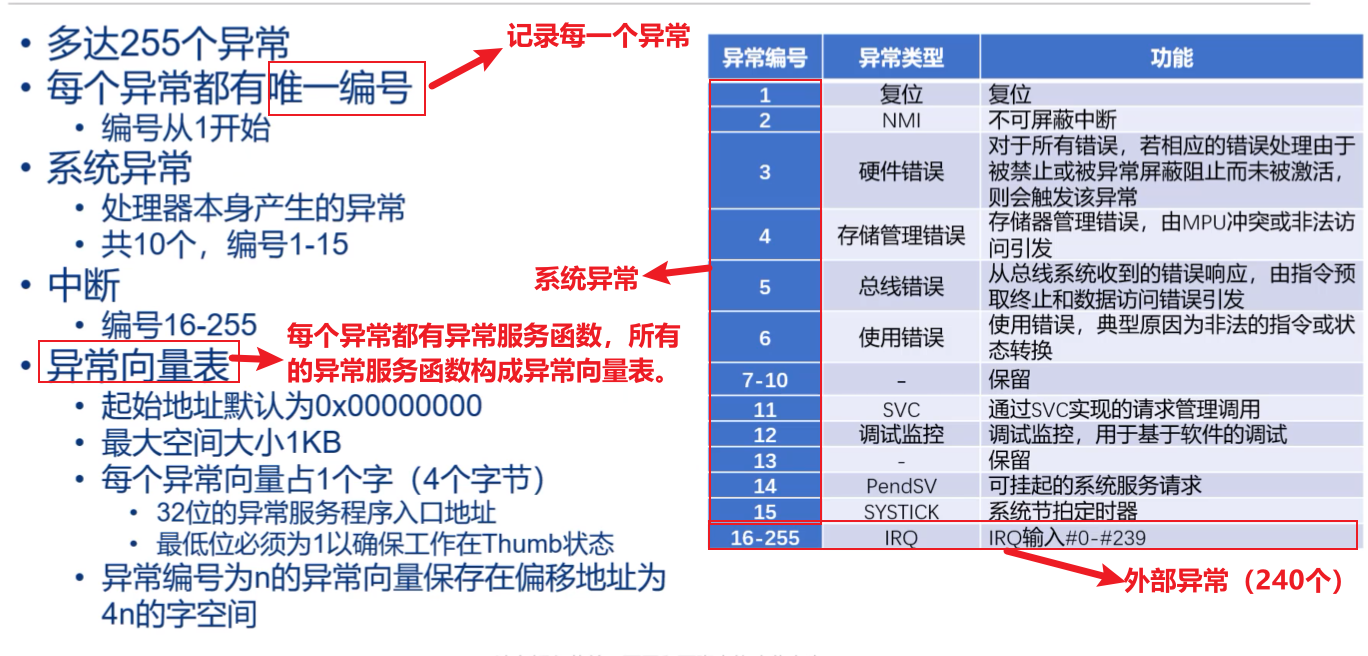

5.1 、异常类型

5.2 、异常响应

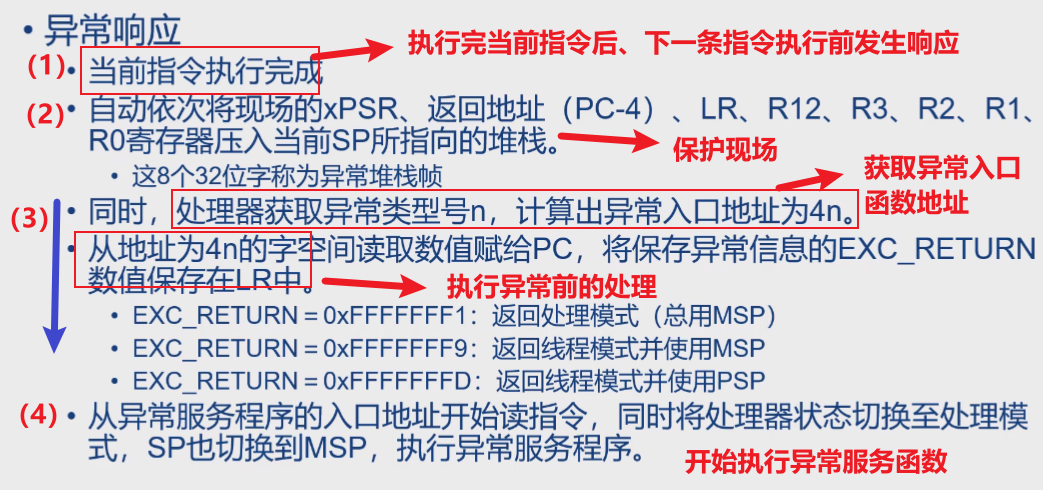

5.2.1 、如何响应

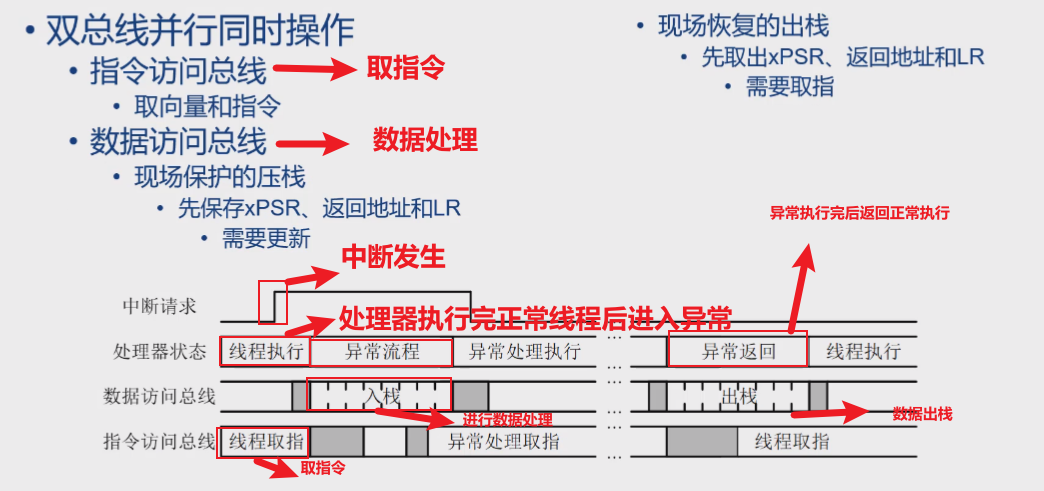

5.2.2 、异常响应时数据总线及指令总线的操作

5.3 、异常处理示例

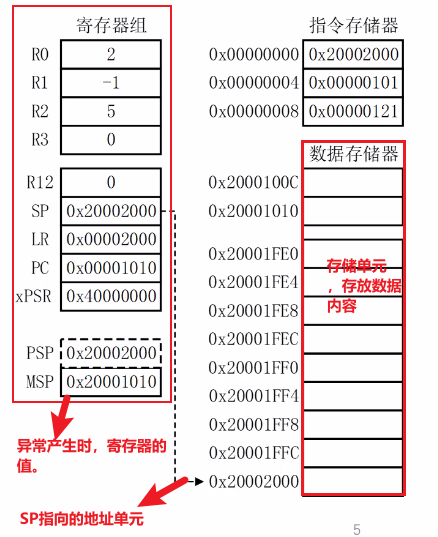

5.3.1 、异常开始产生

上图中的SP与PSP的一样的

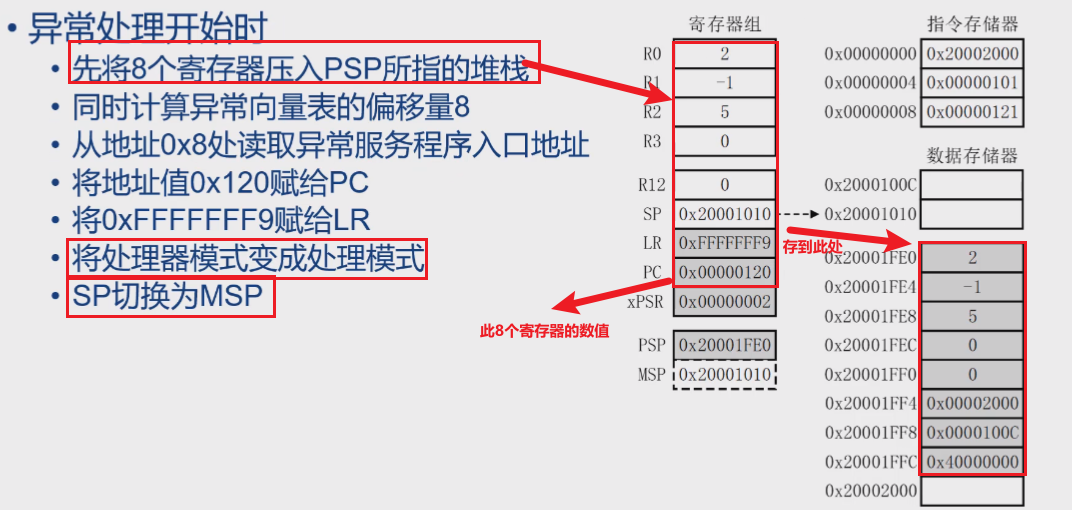

5.3.2 、保护现场

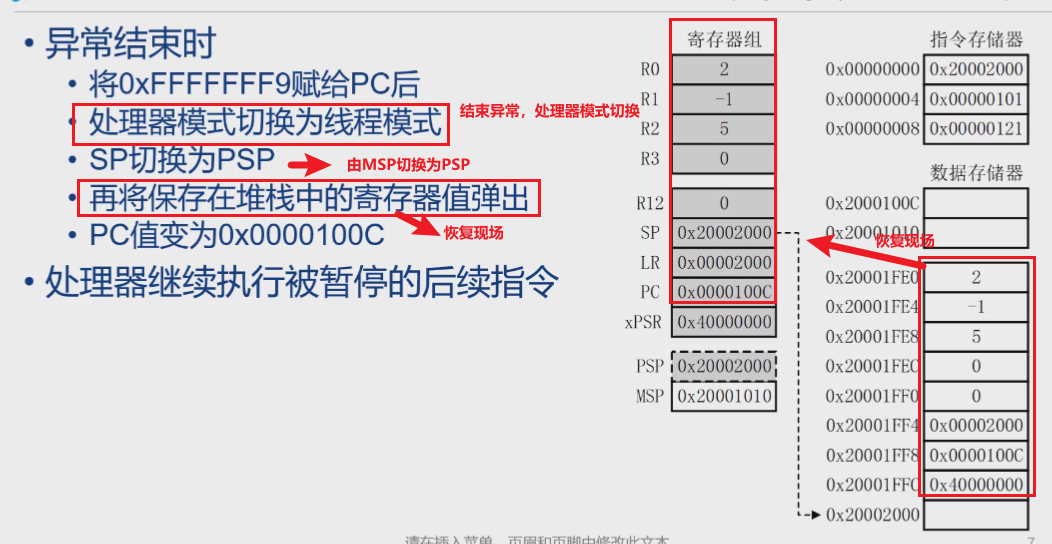

5.3.3 、恢复现场

六、指令体系

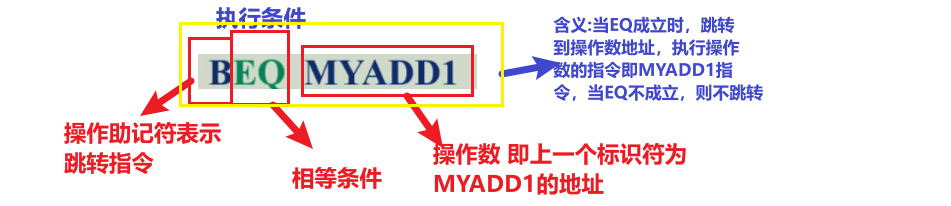

6.1 、指令格式

示例如下:

- MYADD1指令

- B指令:

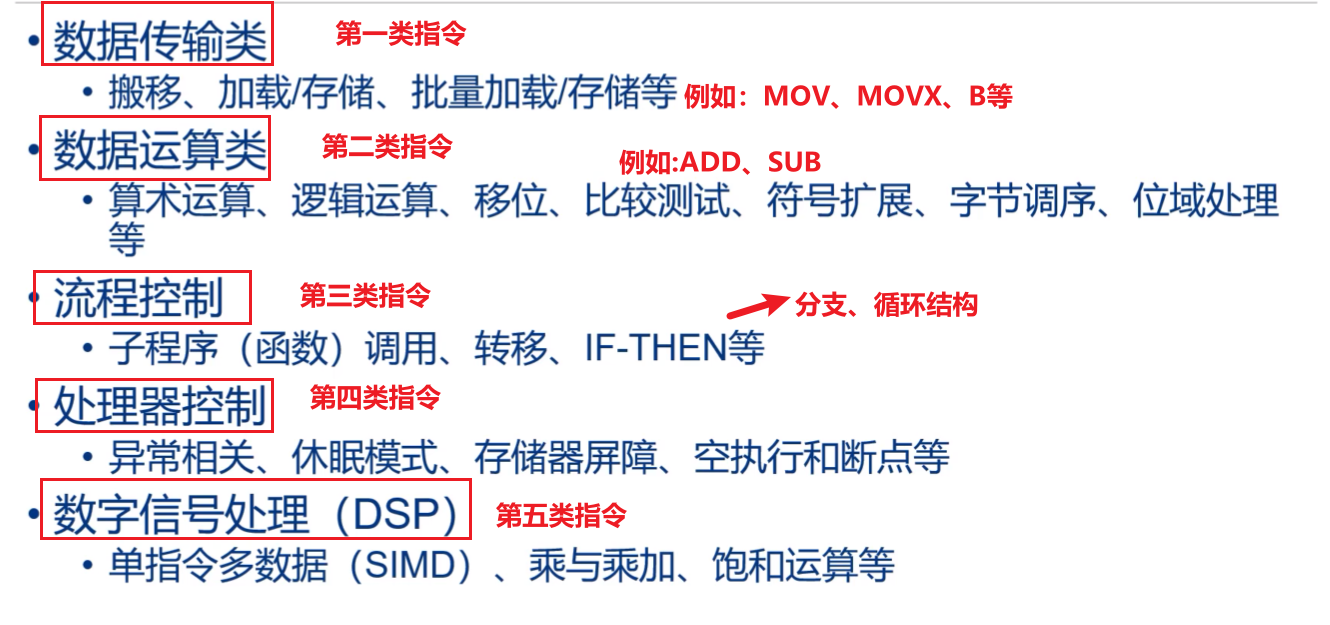

6.2 、指令类型

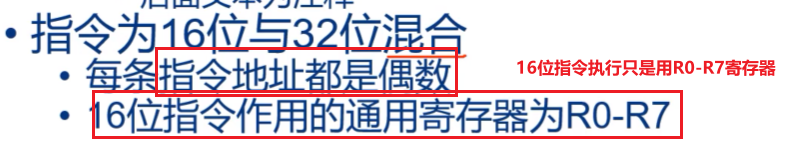

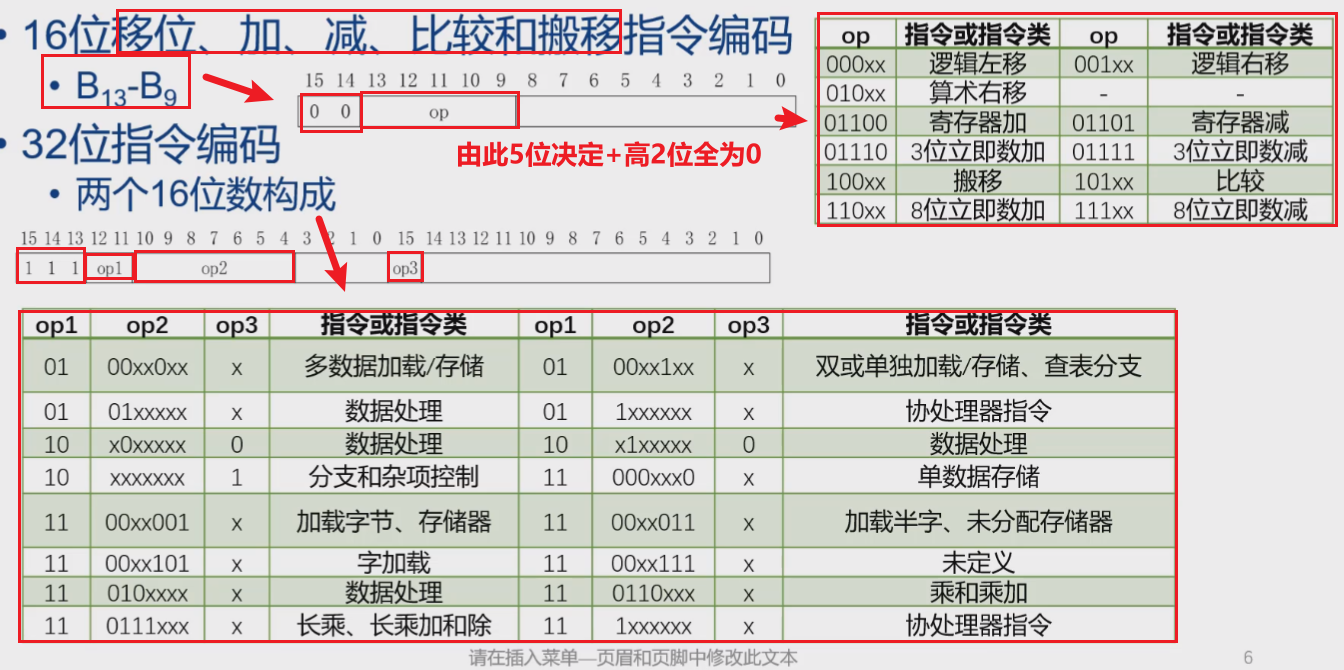

6.3 、指令编码

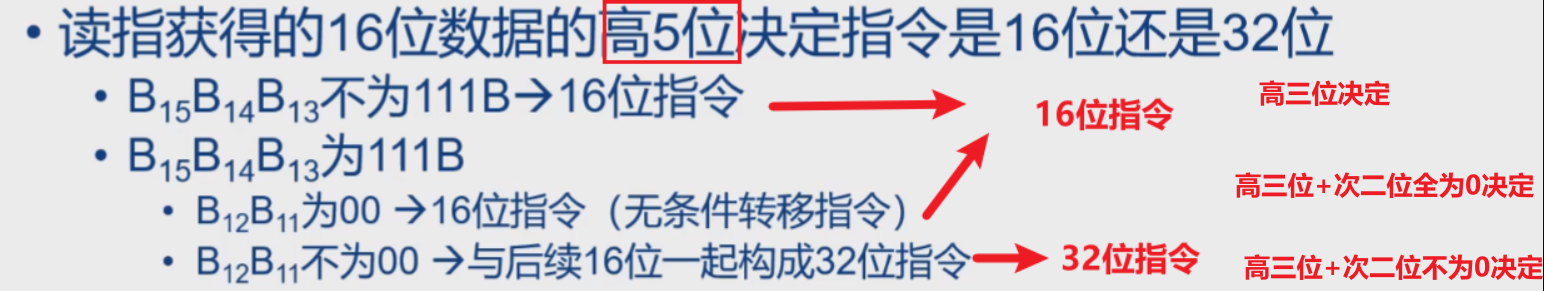

6.3.1 、指令长度(高5位决定)

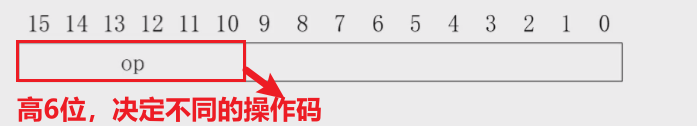

6.3.1 、16位指令类别编码(高6位决定)

如下图所示,不同op的二进制数的对应指令

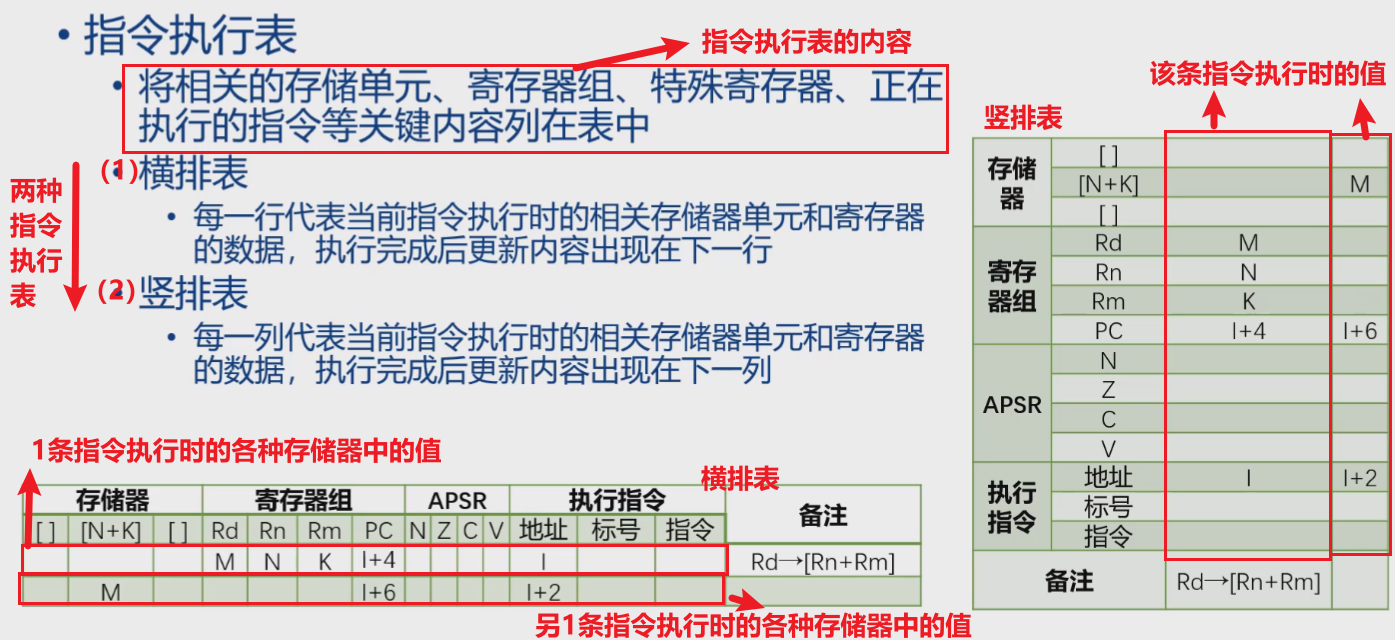

6.4 、指令执行表

七、单条指令数据获取

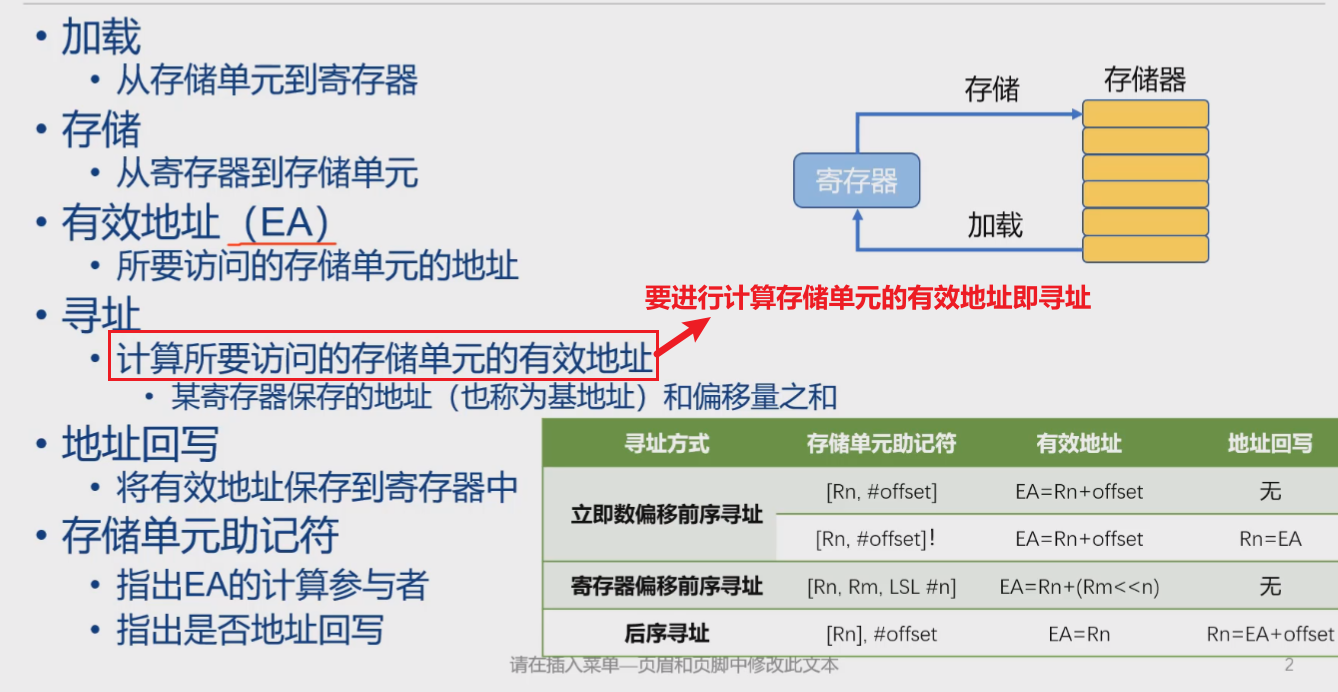

7.1 、数据在寄存器与存储器之间的操作

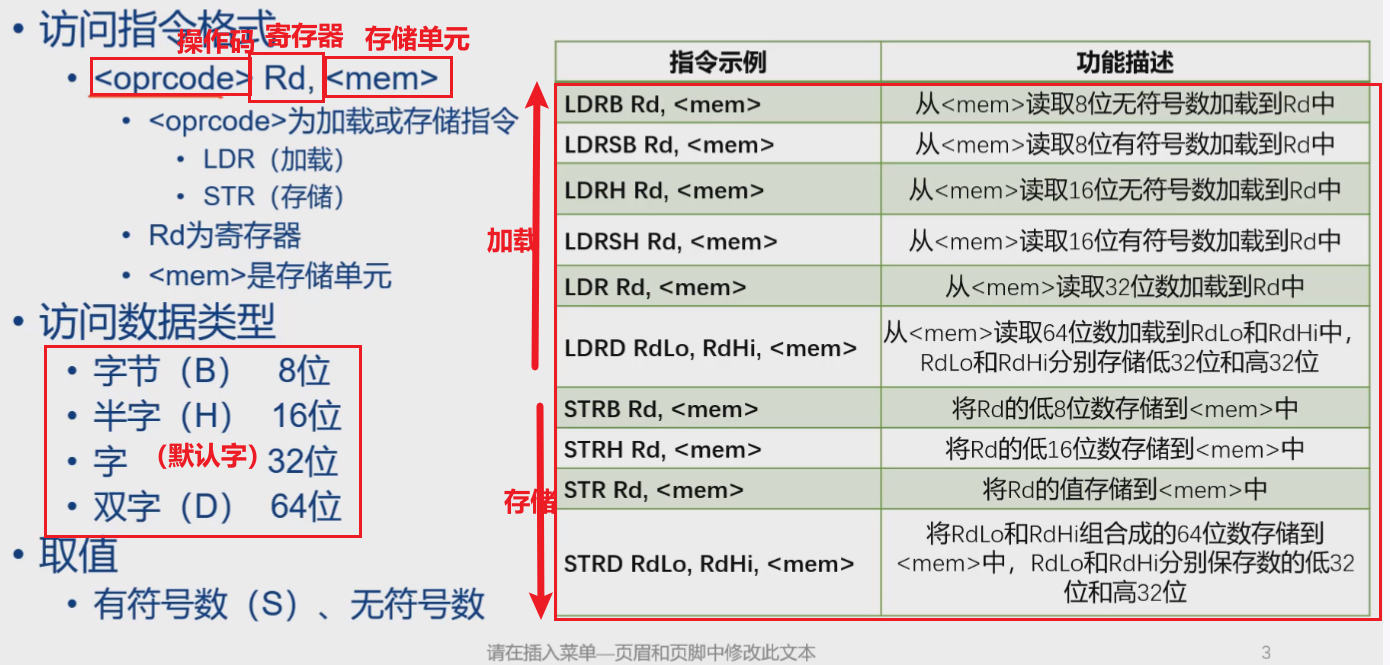

7.2 、指令访问格式

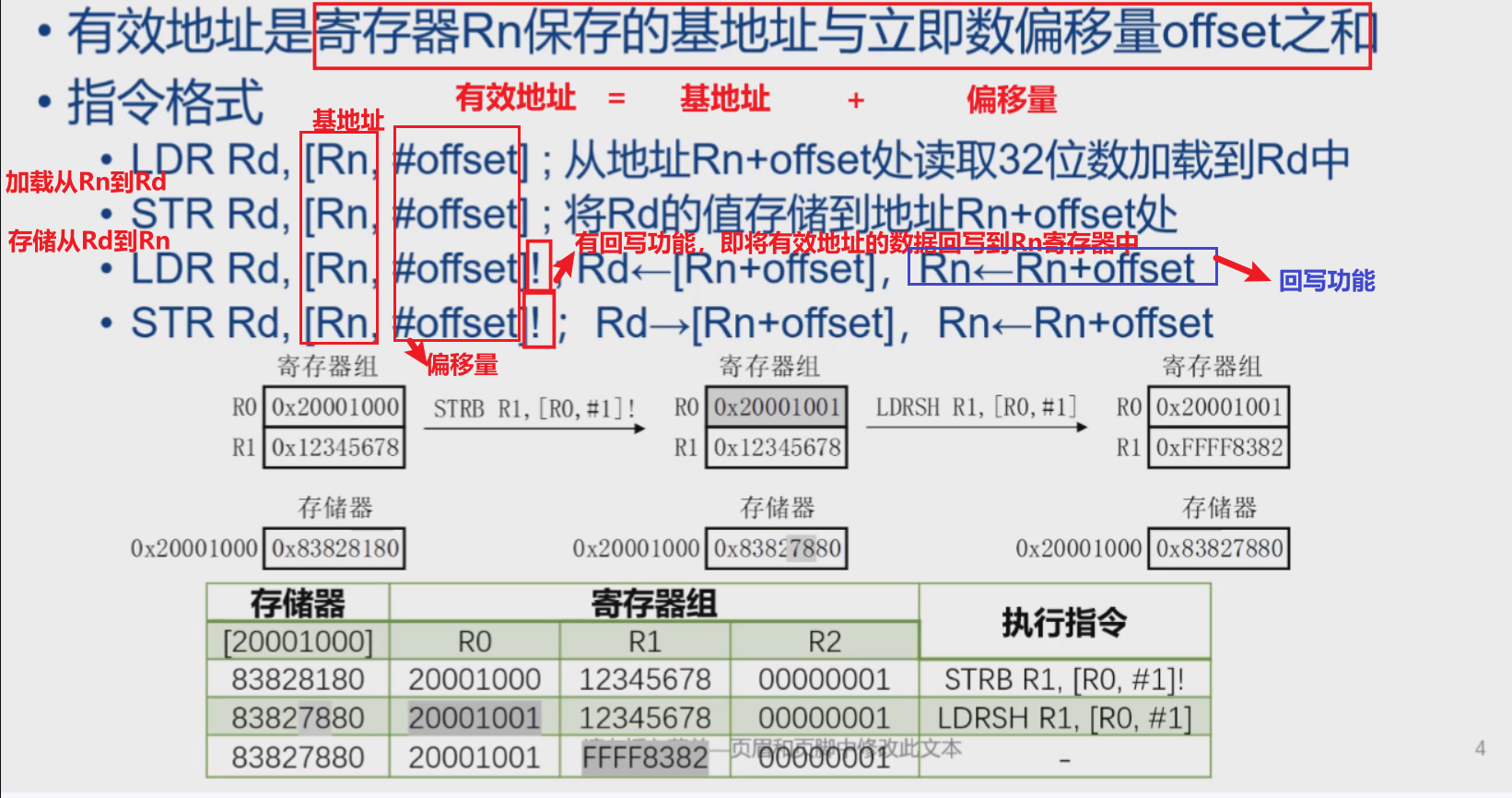

7.3 、立即数偏移前序寻址

示例中S:有符号 H:半字复制(16位) B:1个字节复制(8位)

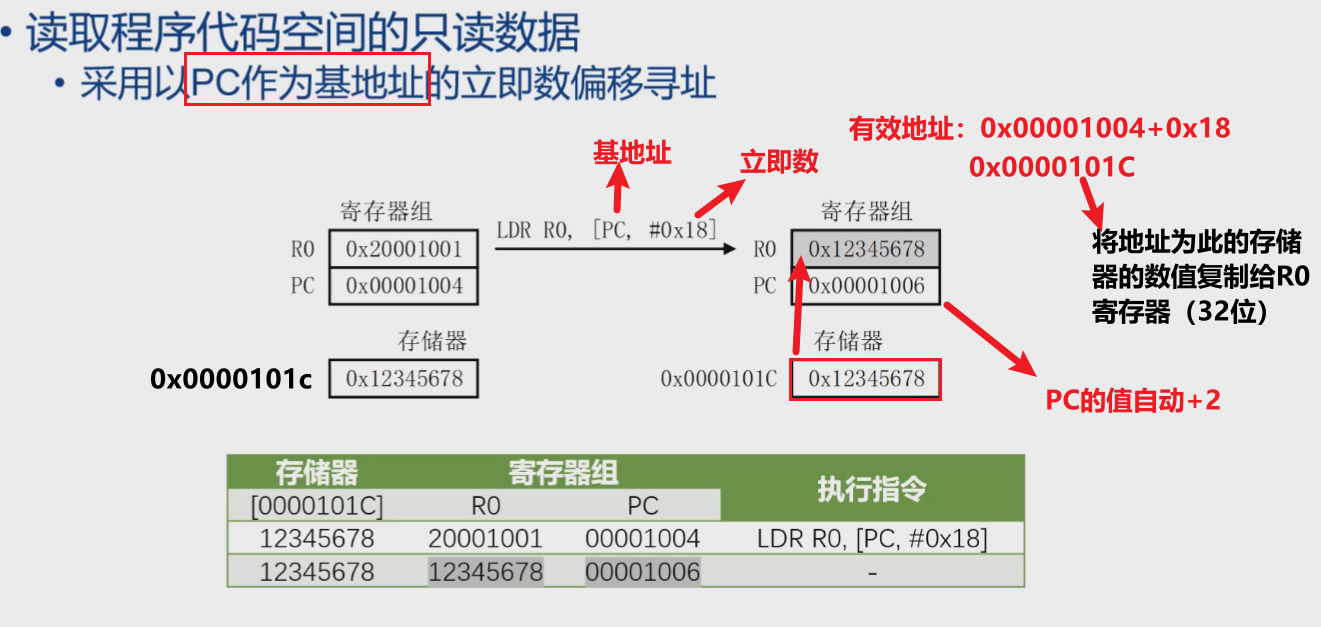

7.3 、文本池访问(PC作为基地址)

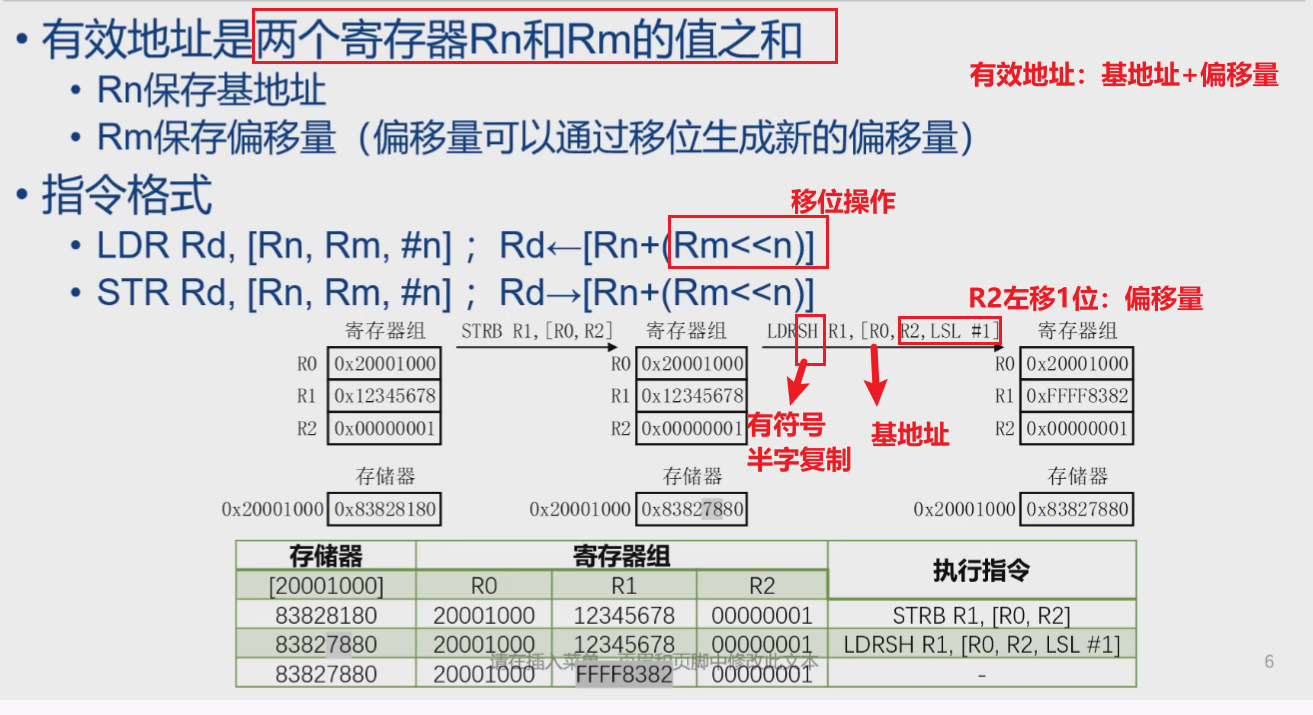

7.3 、寄存器偏移前序寻址

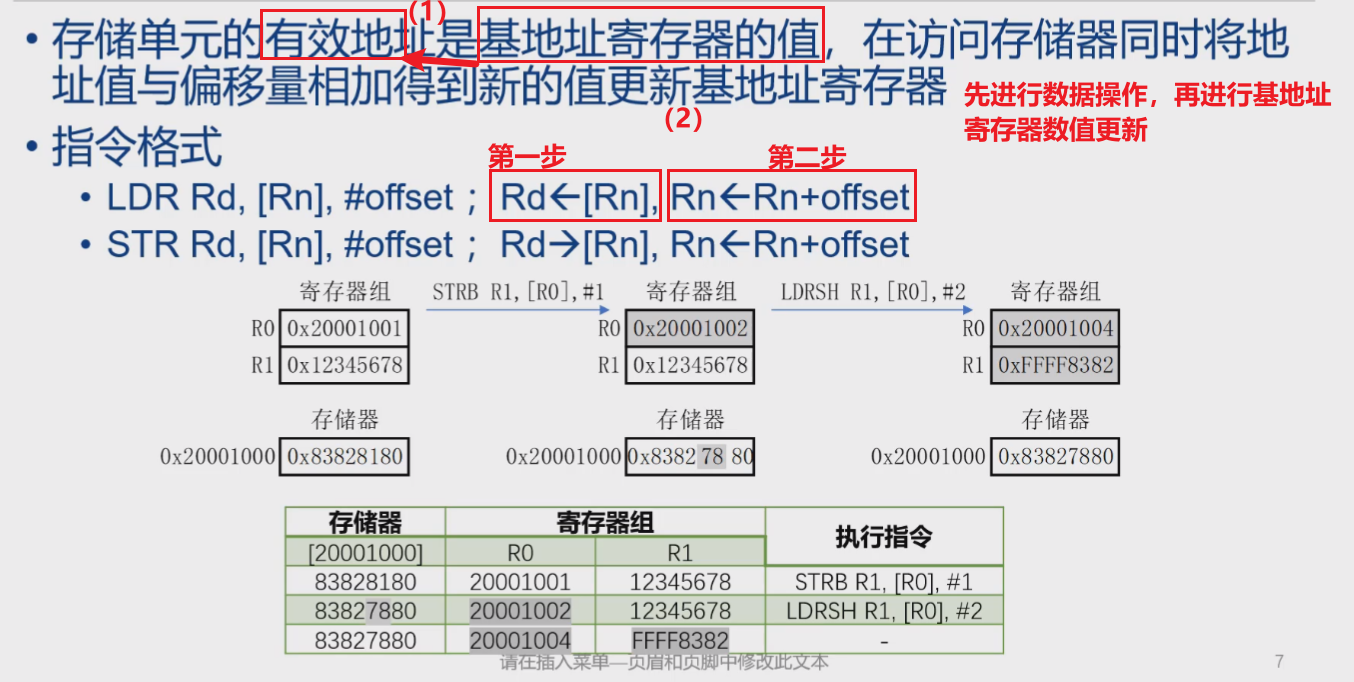

7.4 、后序寻址

八、多寄存器多条指令数据获取

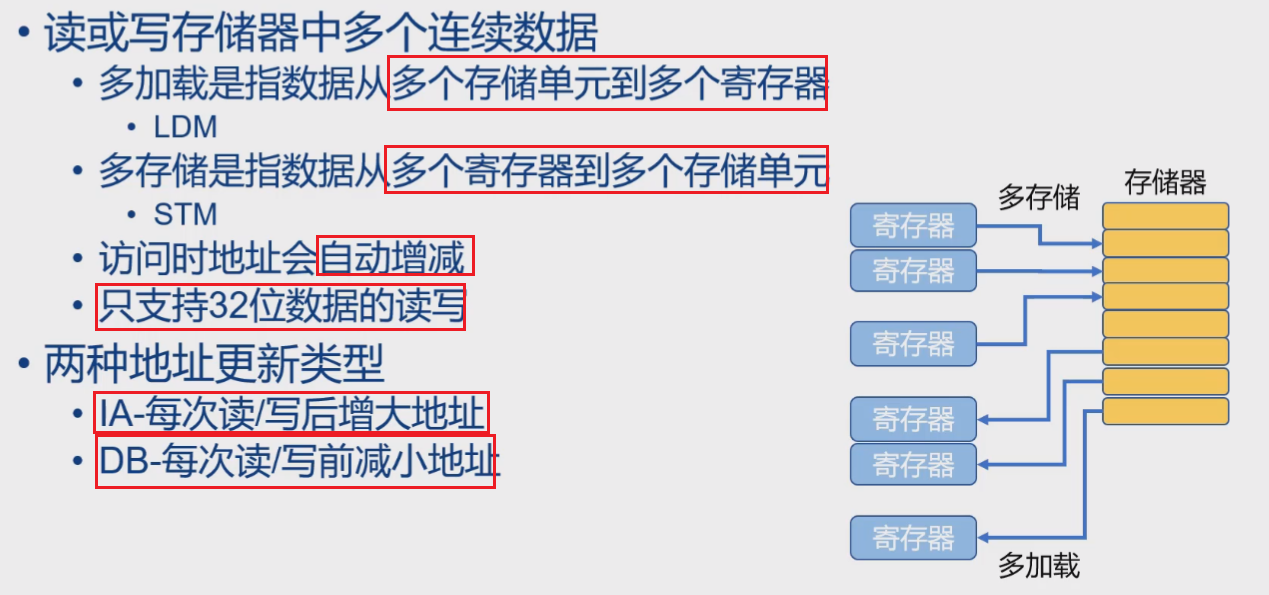

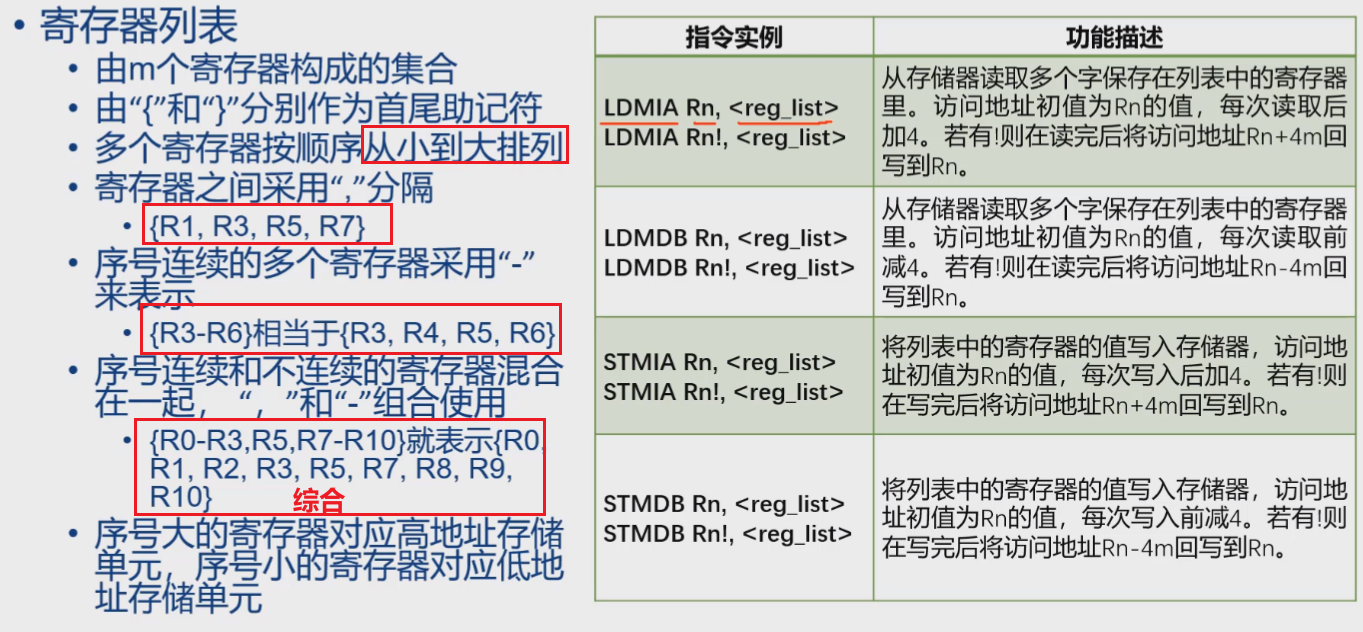

8.1 、多加载多存储指令

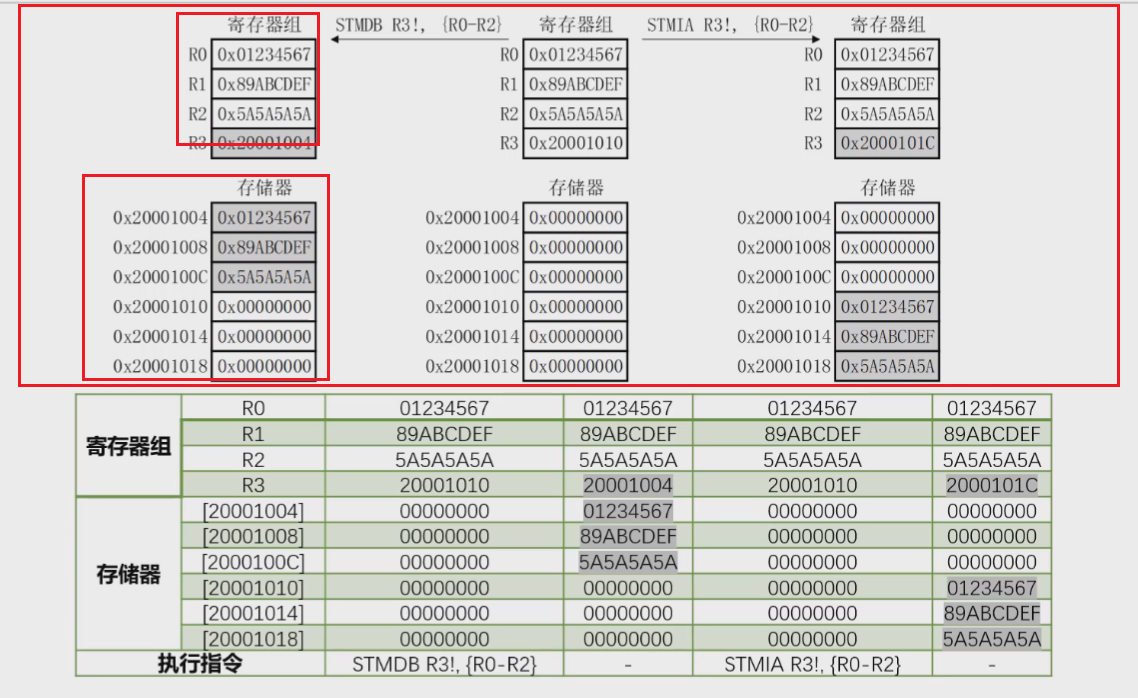

8.2 、多数据存储

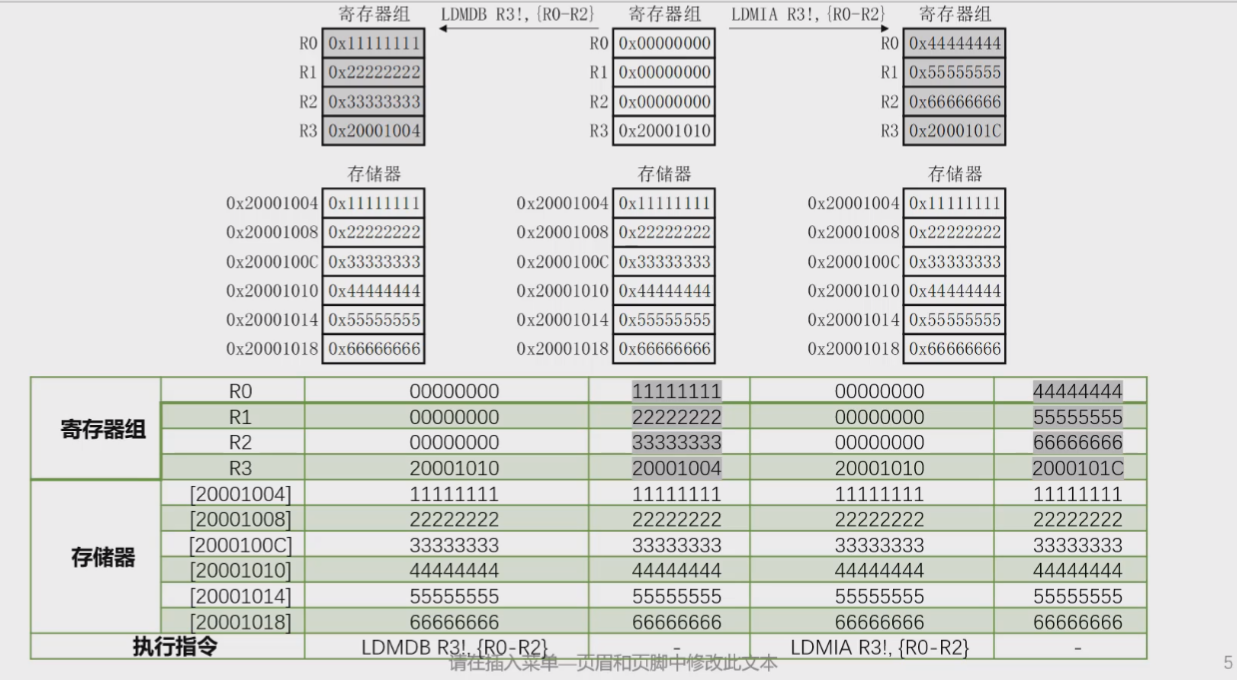

8.3 、多数据加载

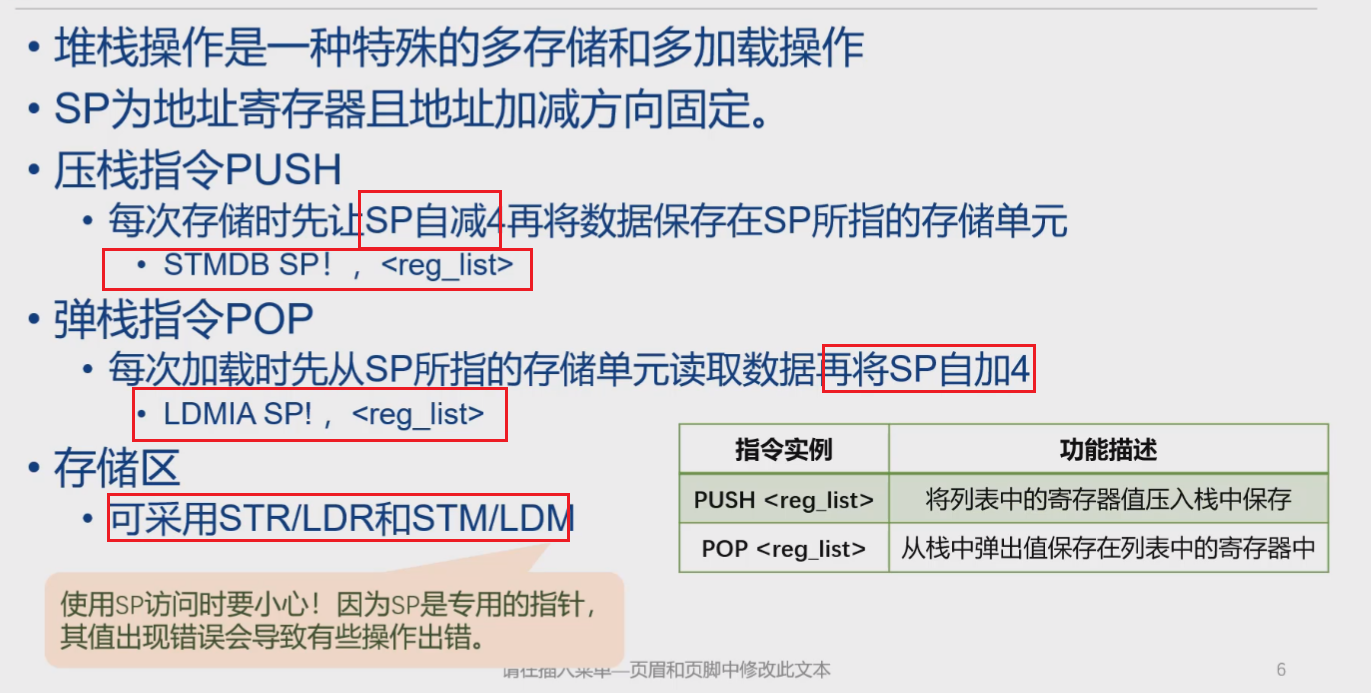

8.4 、多数据的堆栈操作

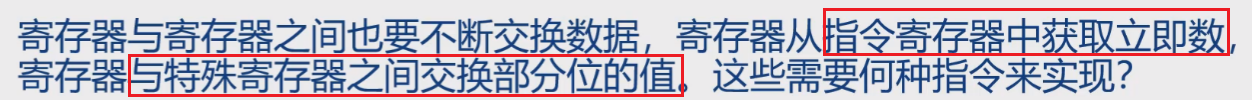

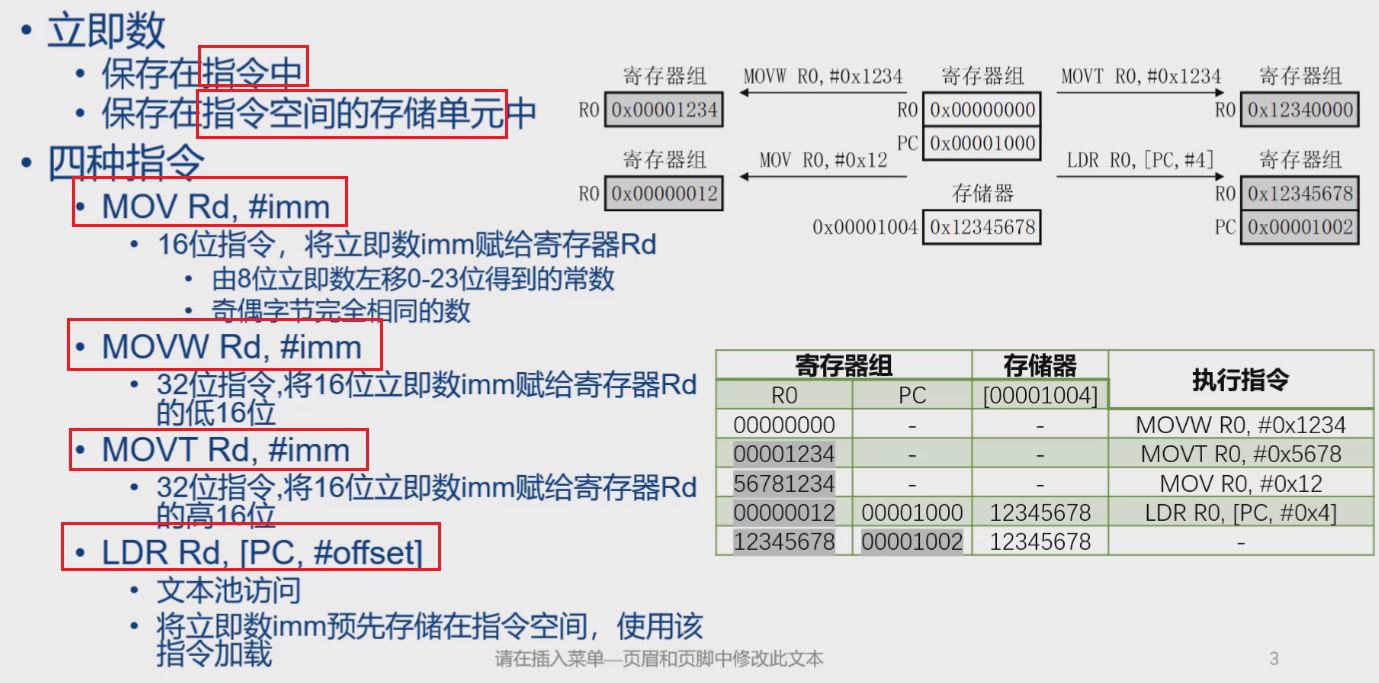

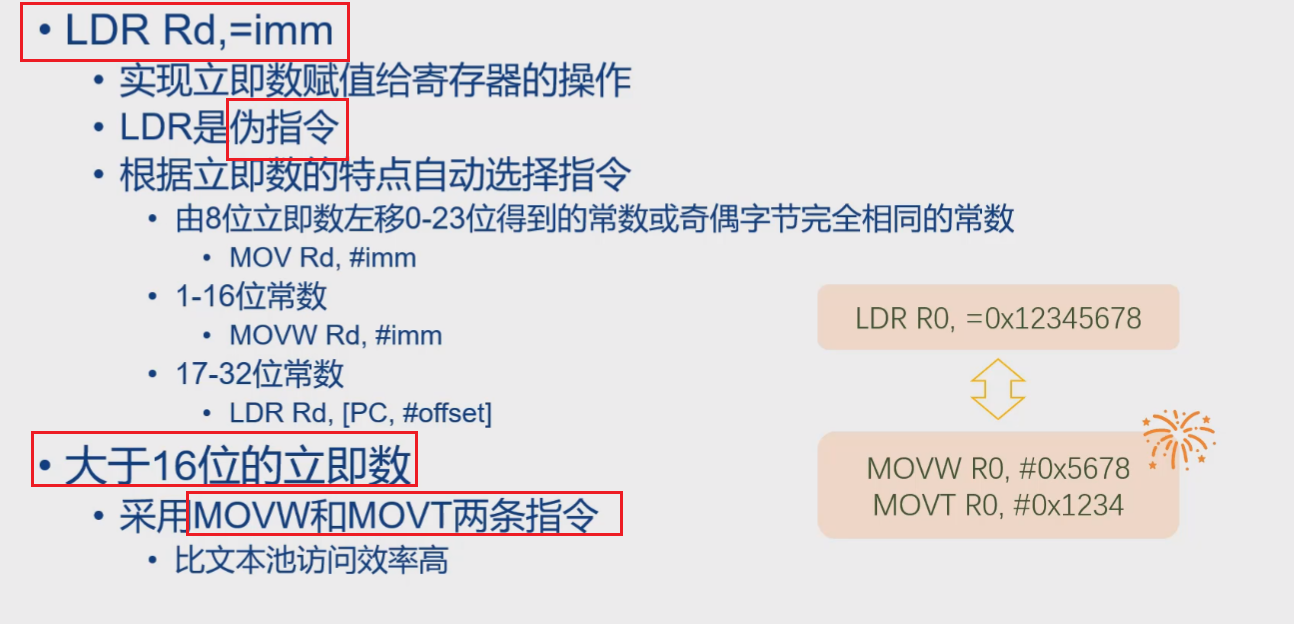

九、寄存器间数据传输

9.1 、两条指令

9.2 、立即数加载

9.3 、寄存器与特殊寄存器之间

十、程序编程之程序设计(***)

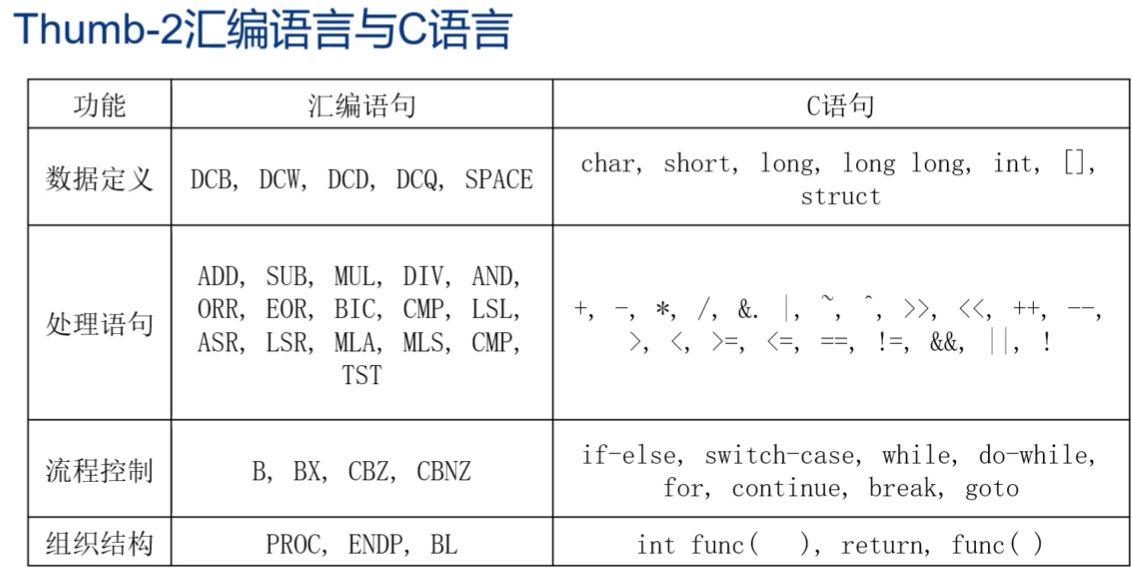

10.1 、Thumb-2汇编语言与C语言的对照

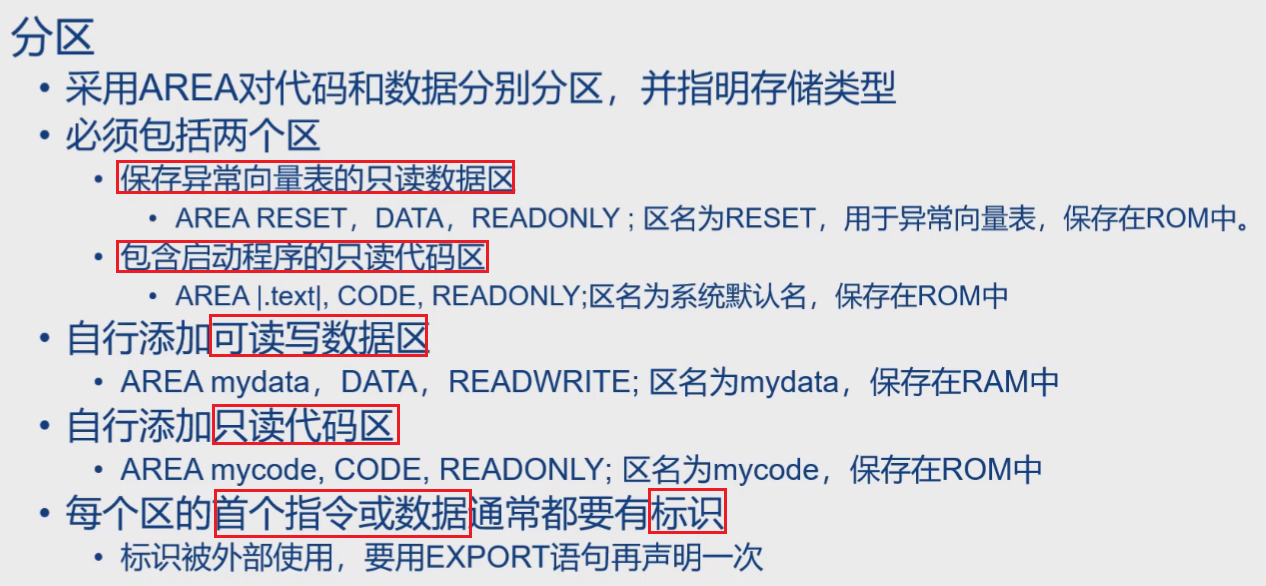

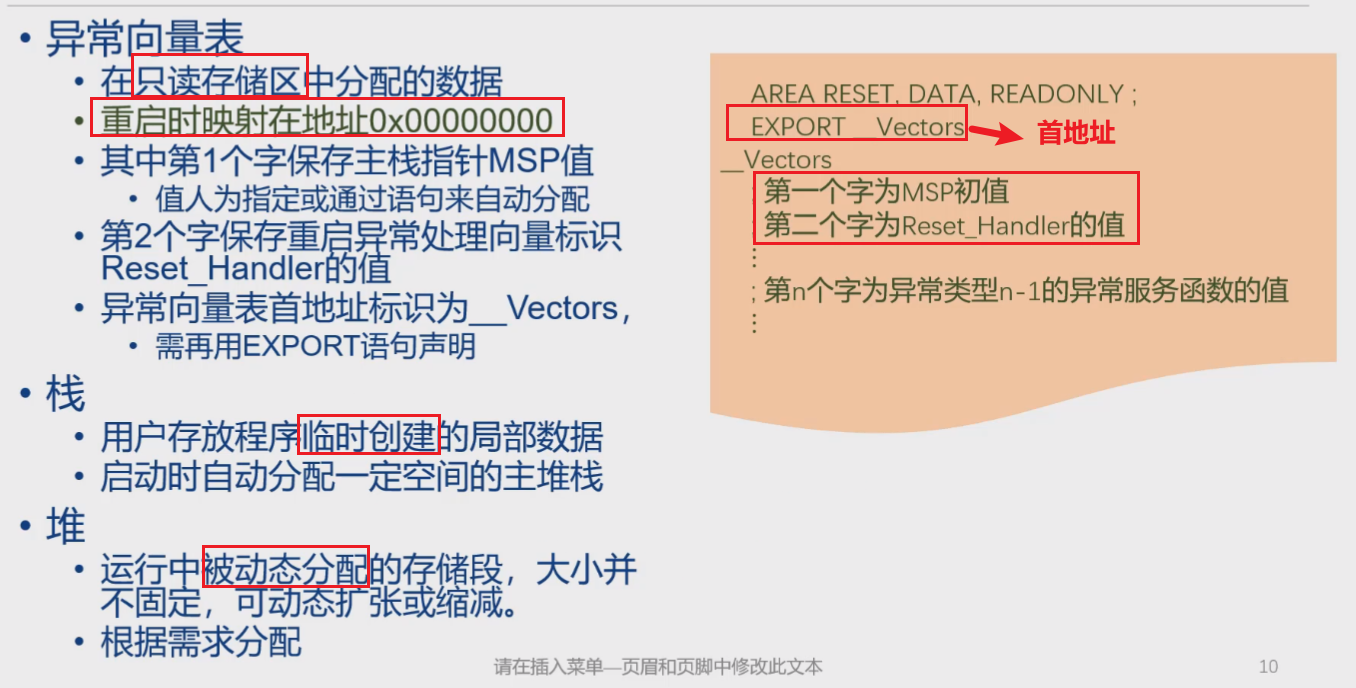

10.2 、汇编语言结构

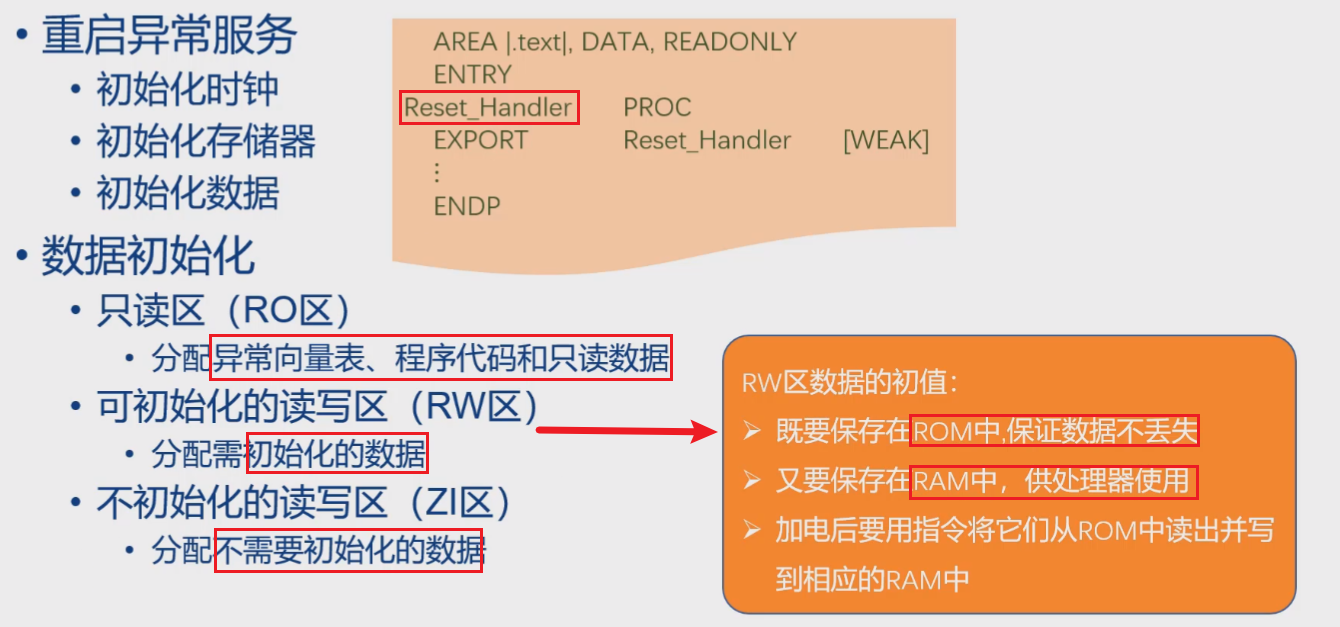

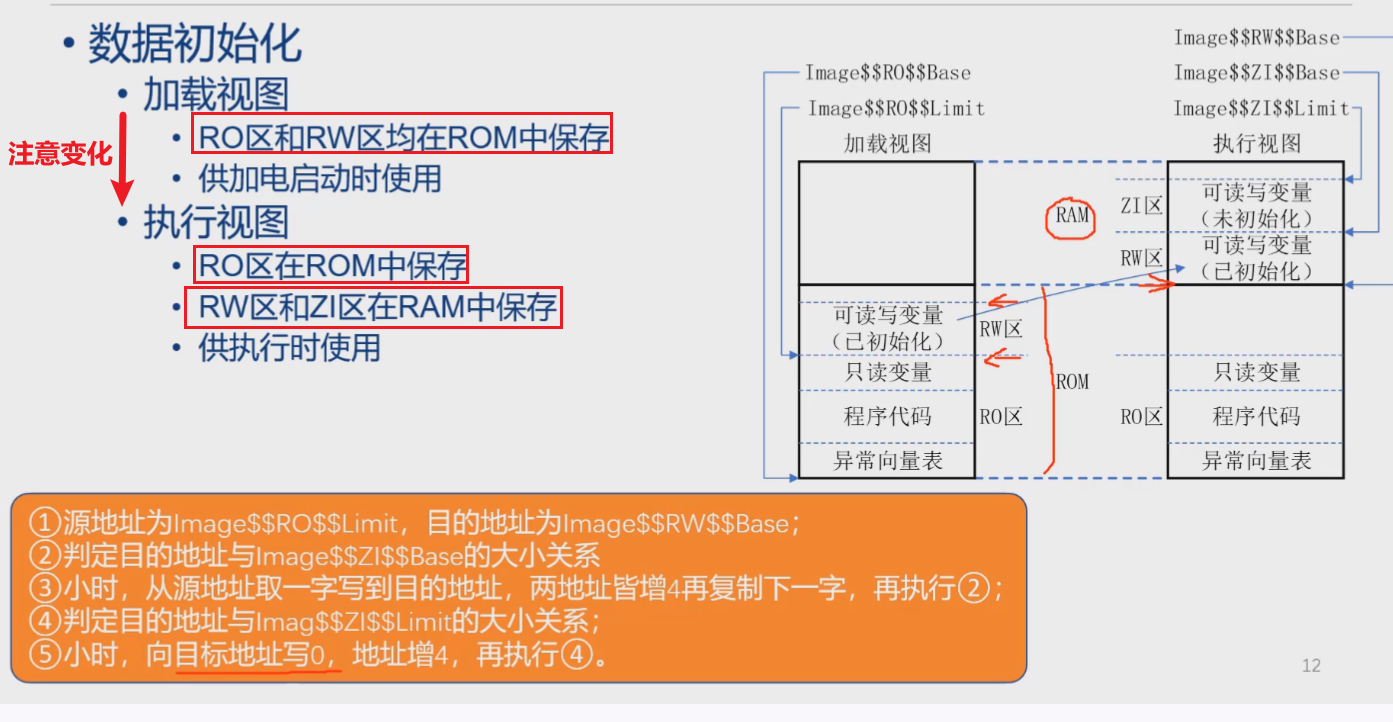

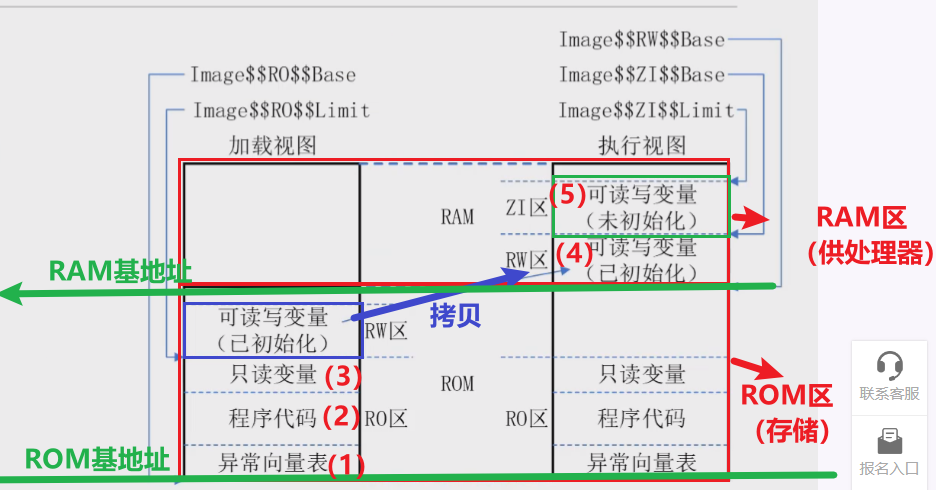

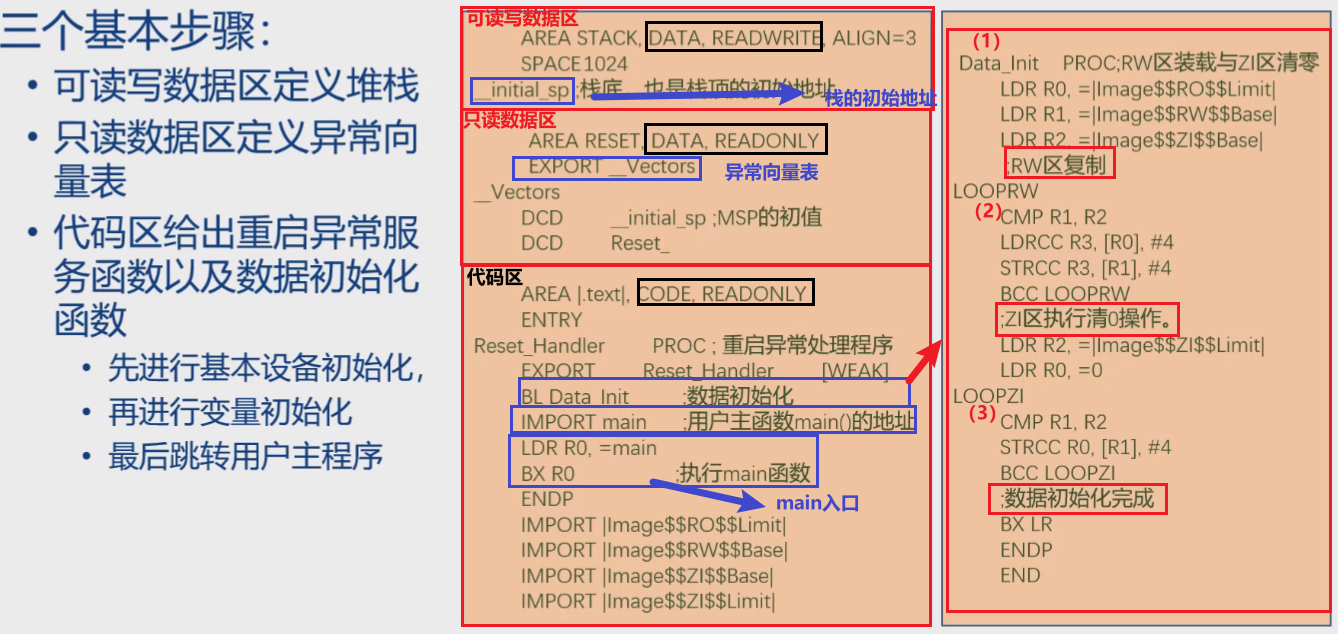

10.2.1 、数据初始化

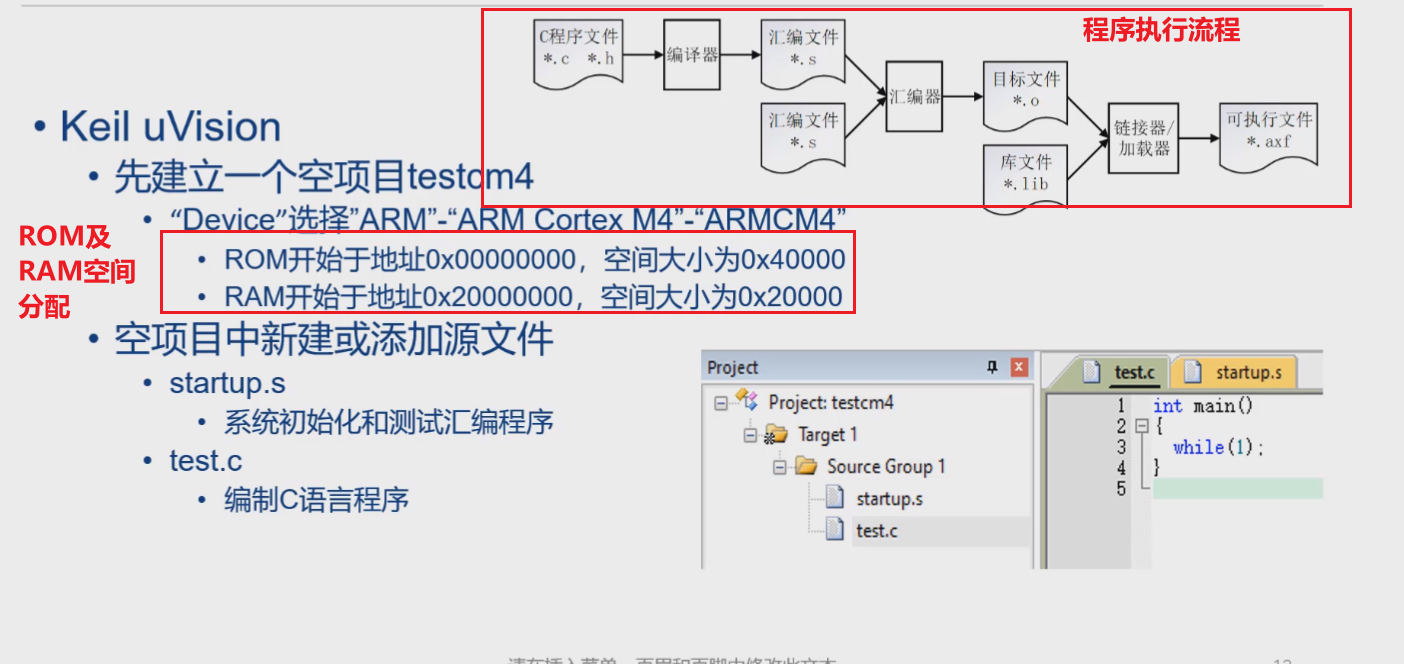

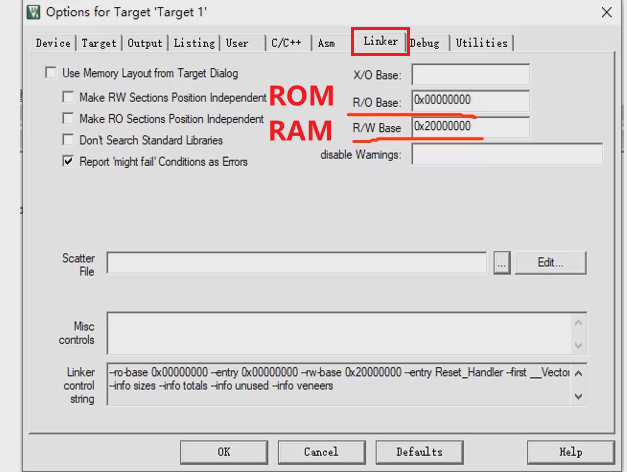

10.3 、keil工程

10.4 、启动文件

十一、汇编语言

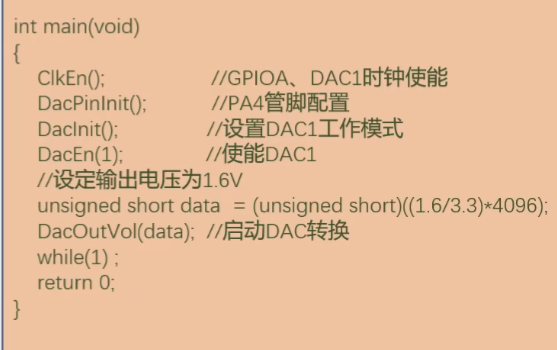

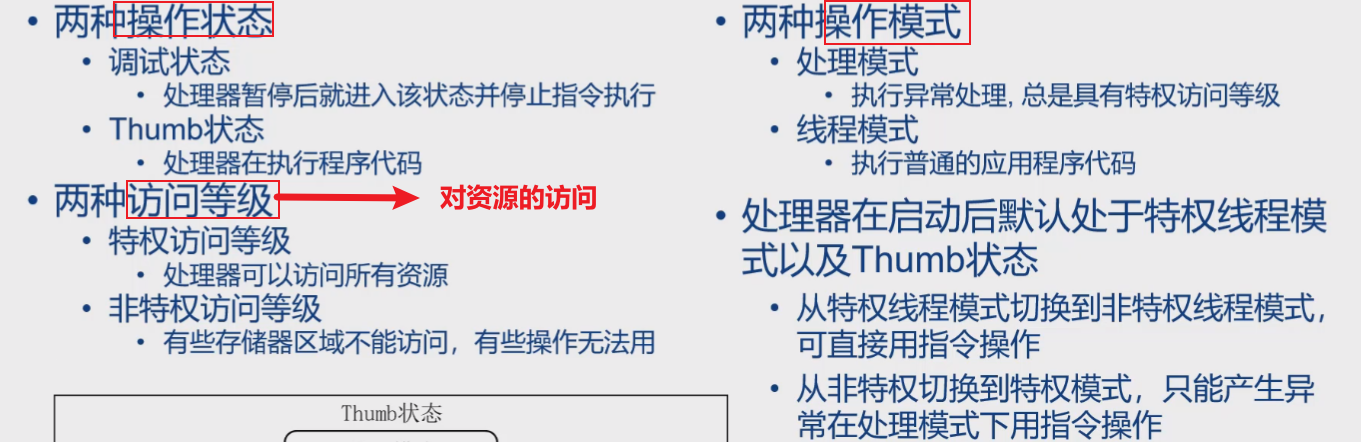

十一、Cortex-M4处理器

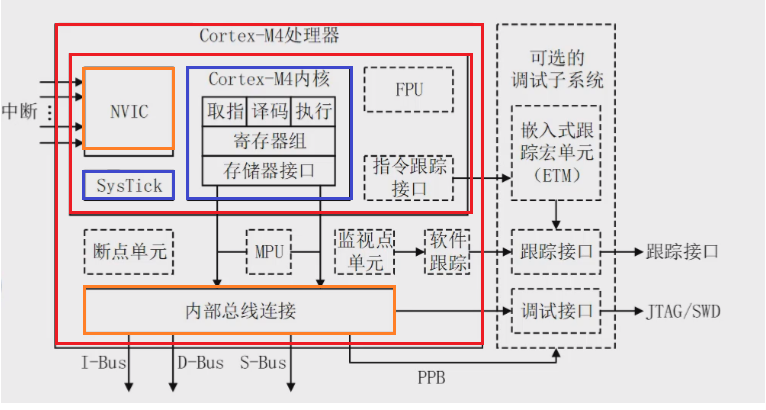

11.1 、Cortex-M4处理器结构

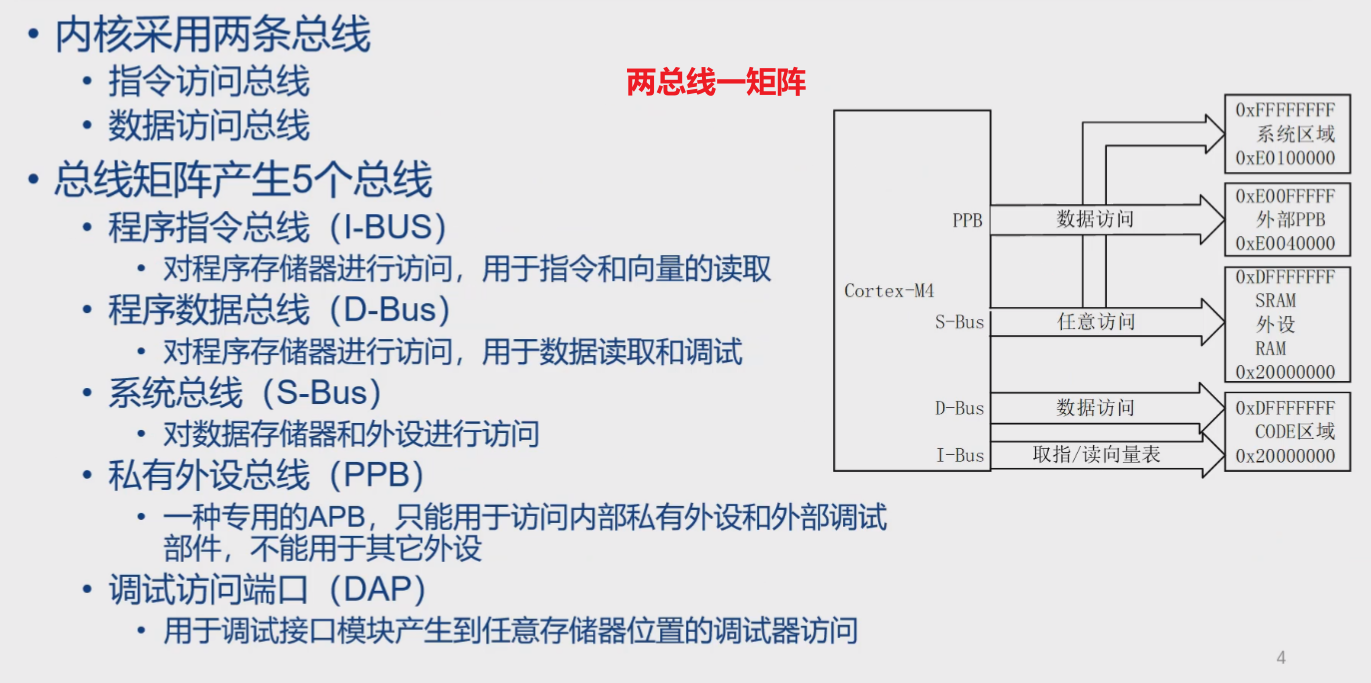

11.2 、Cortex-M4处理器总线

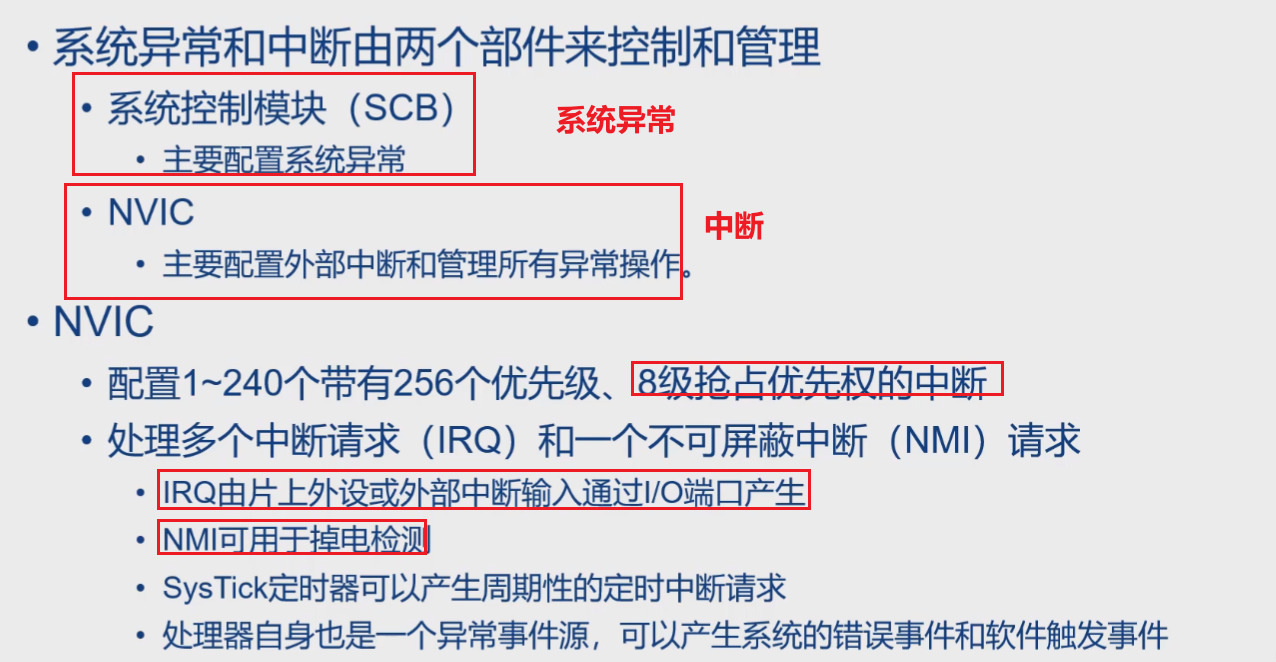

11.3 、系统异常与中断

11.4 、中断优先级

十二、片上微处理器系统结构

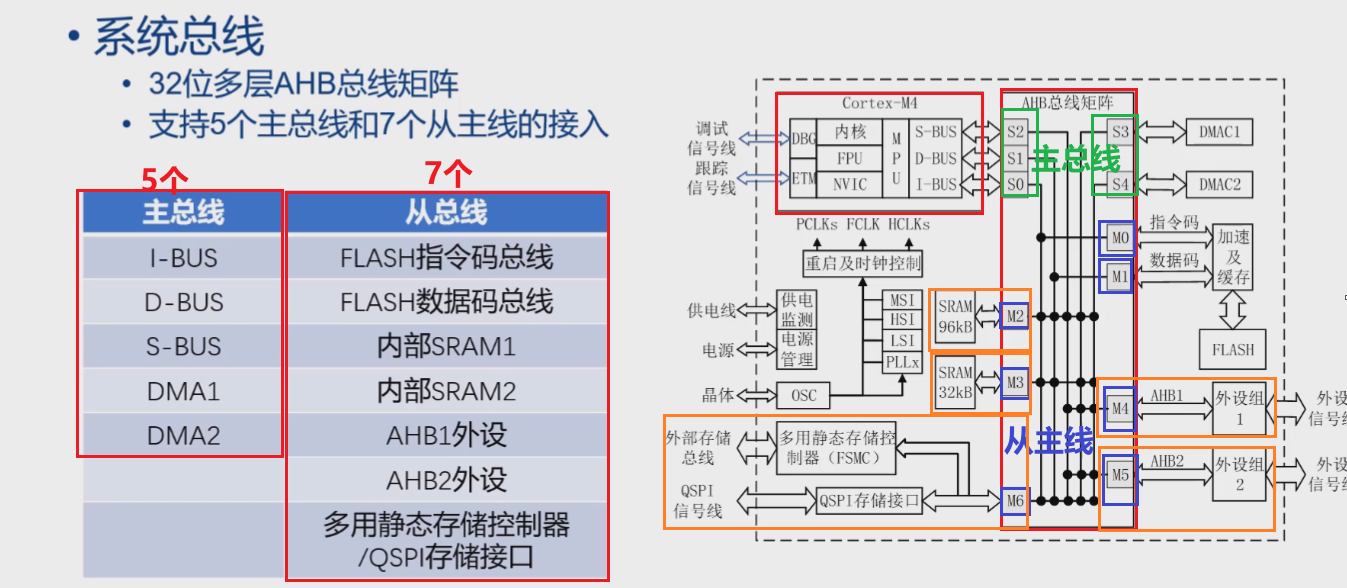

12.1 、系统总线

12.2 、外设总线

12.3 、系统时钟

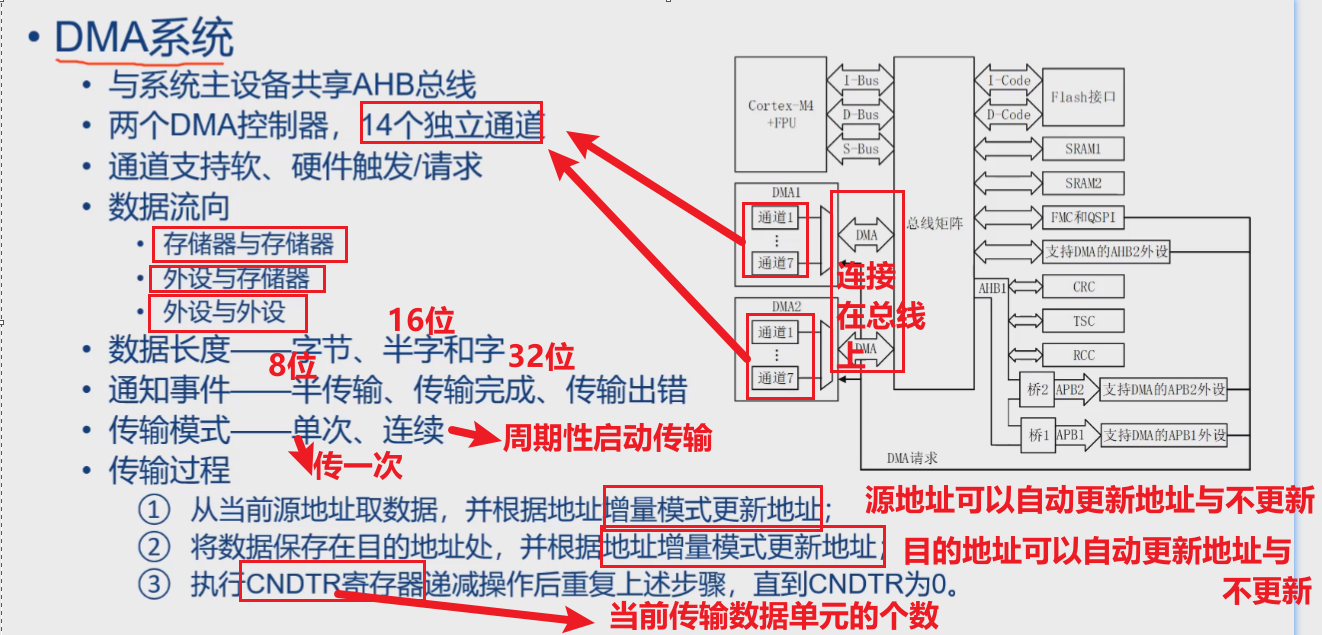

12.4 、DMA系统

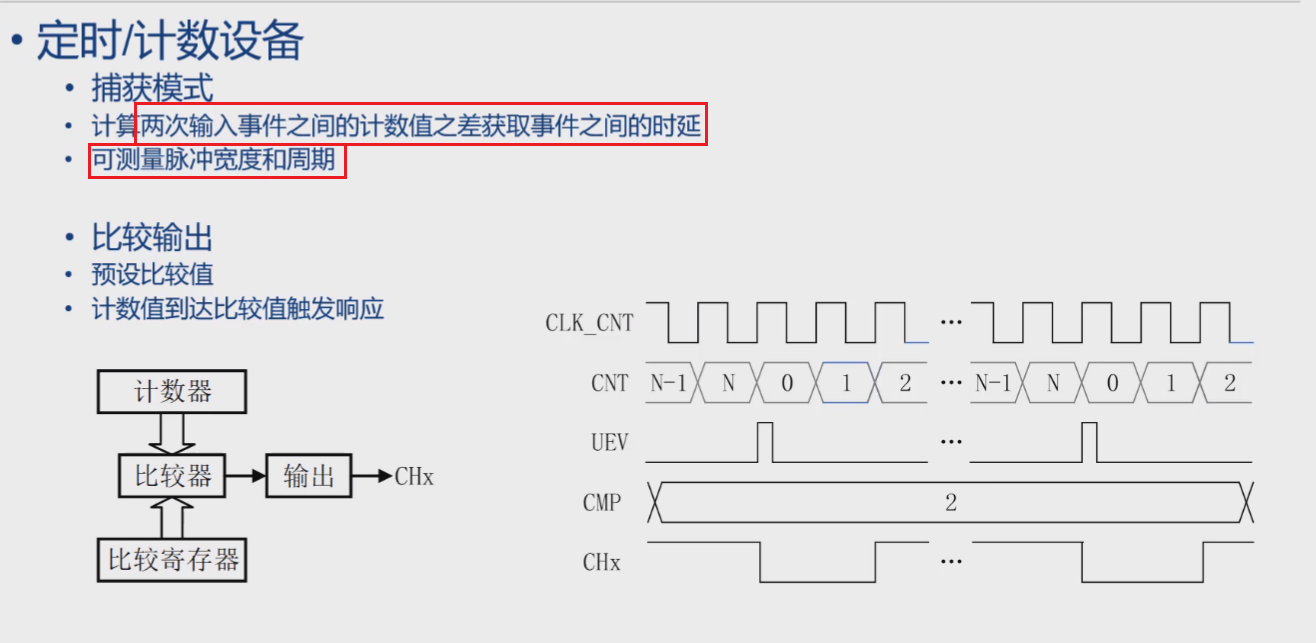

12.5 、定时/计数器设备

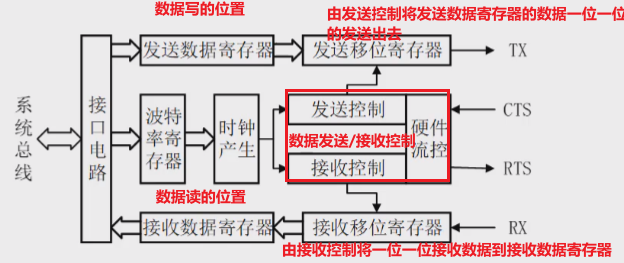

12.5 、通信设备

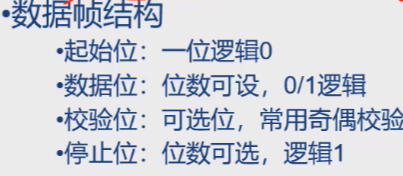

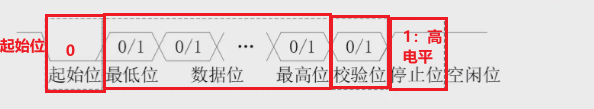

12.5.1 、数据帧格式

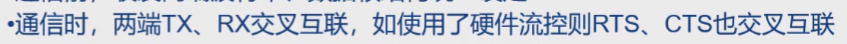

12.6 、SPI

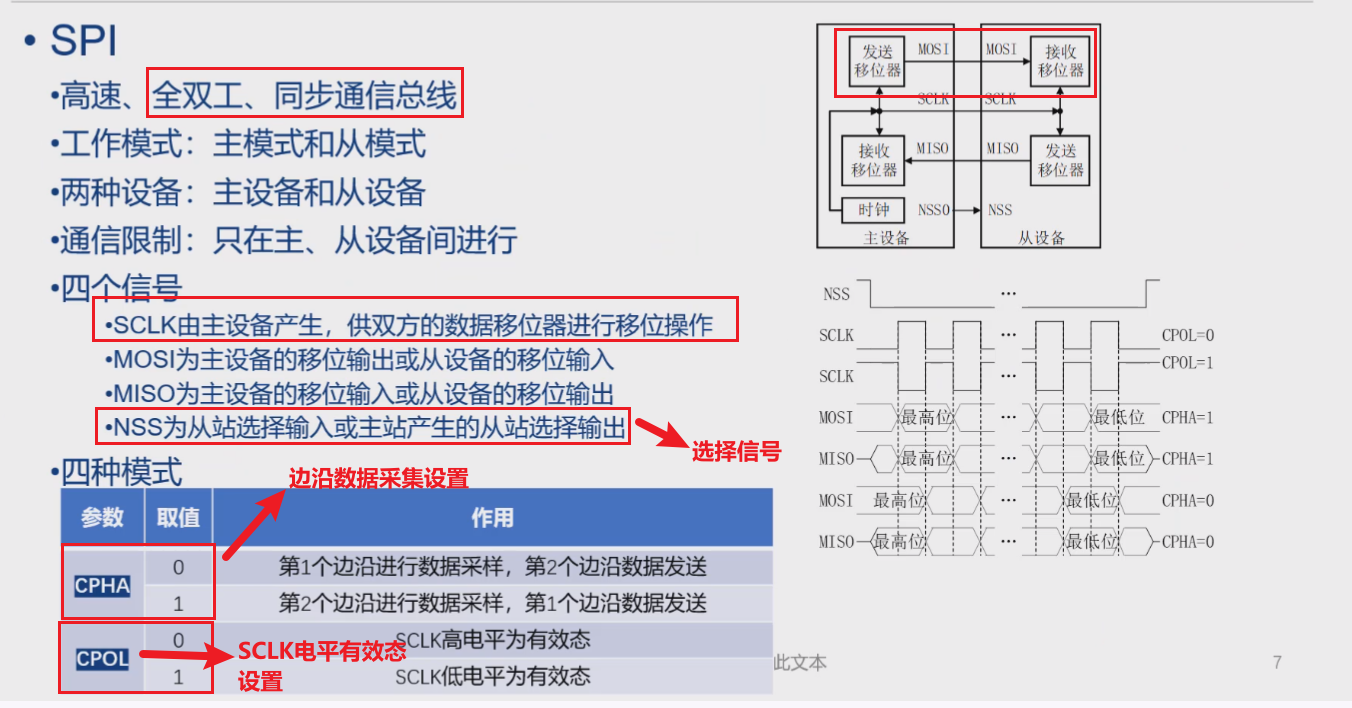

12.7 、IIC

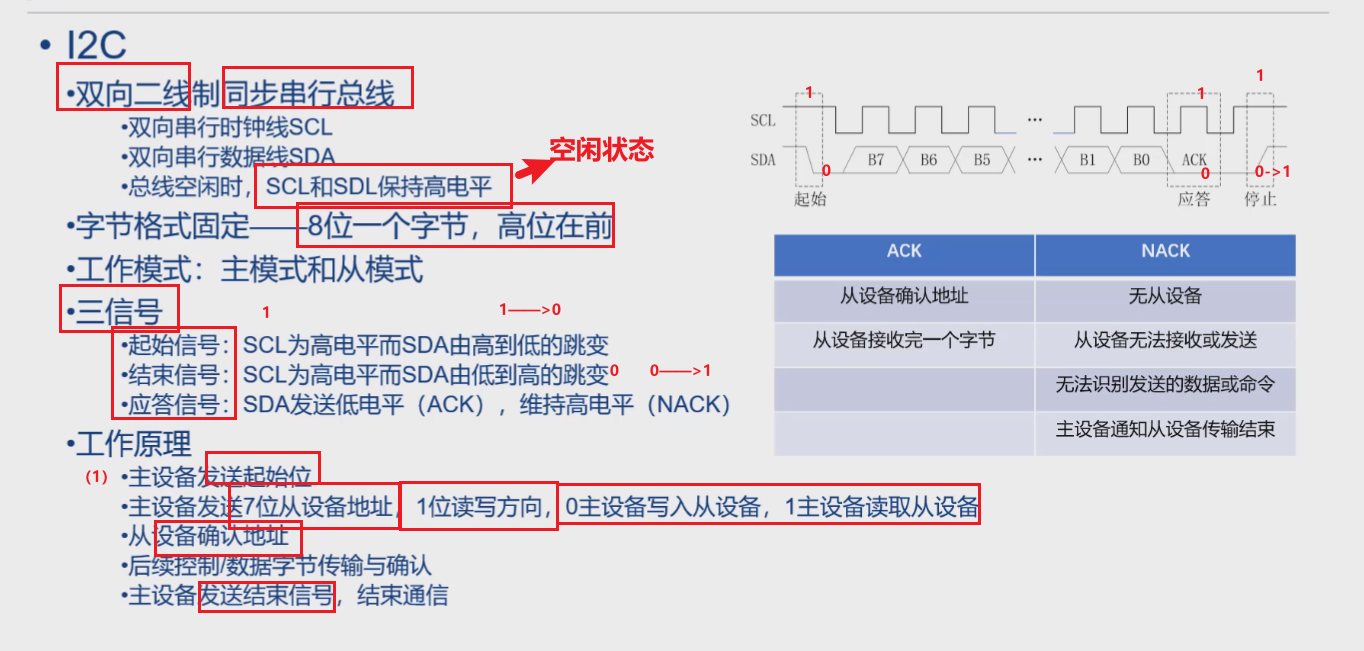

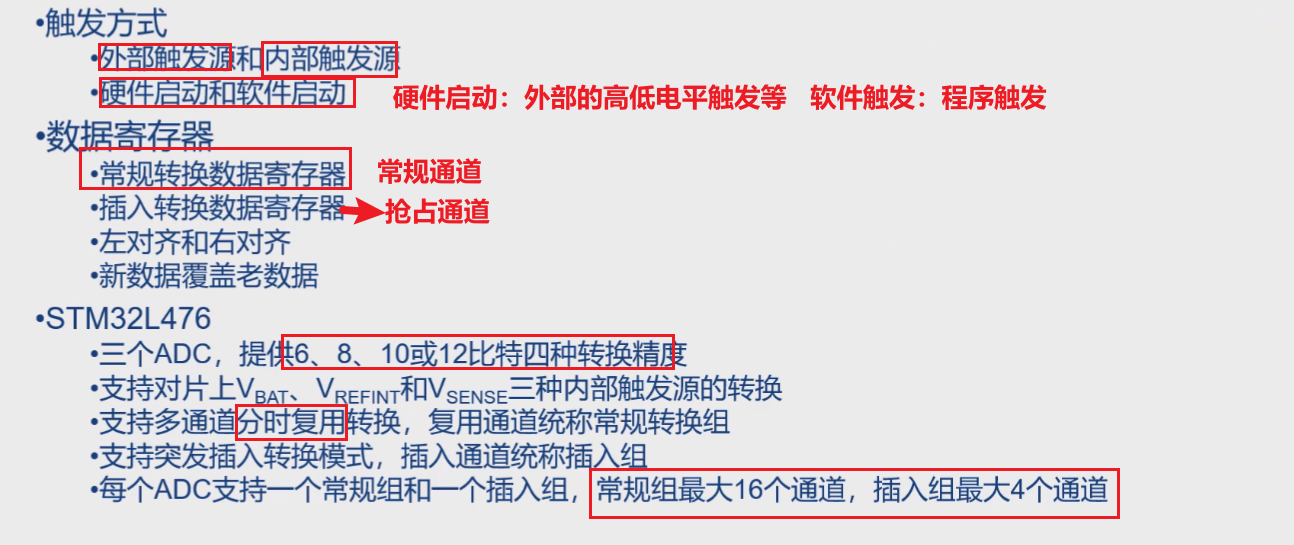

12.8 、ADC

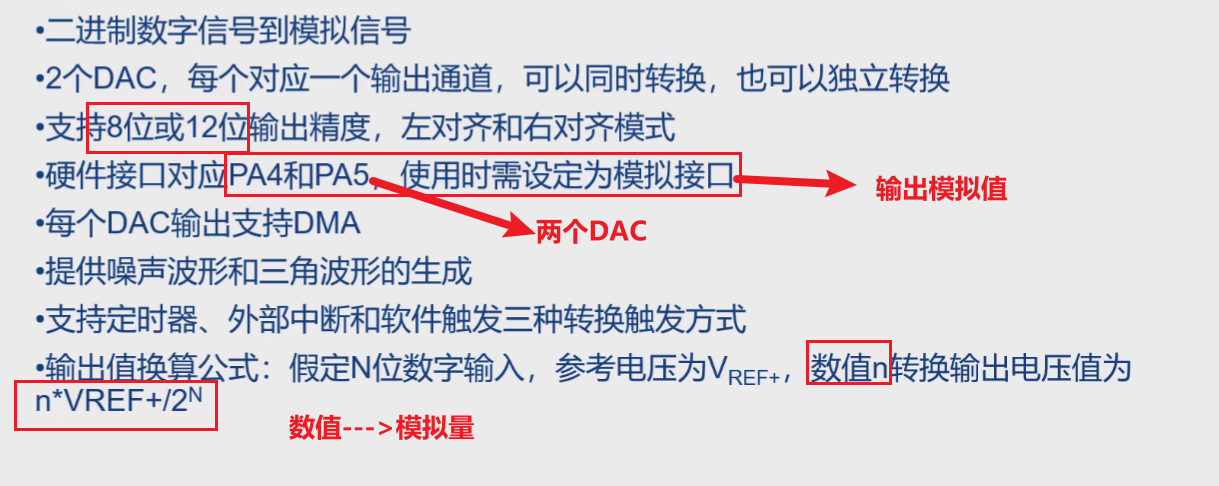

12.9 、DAC

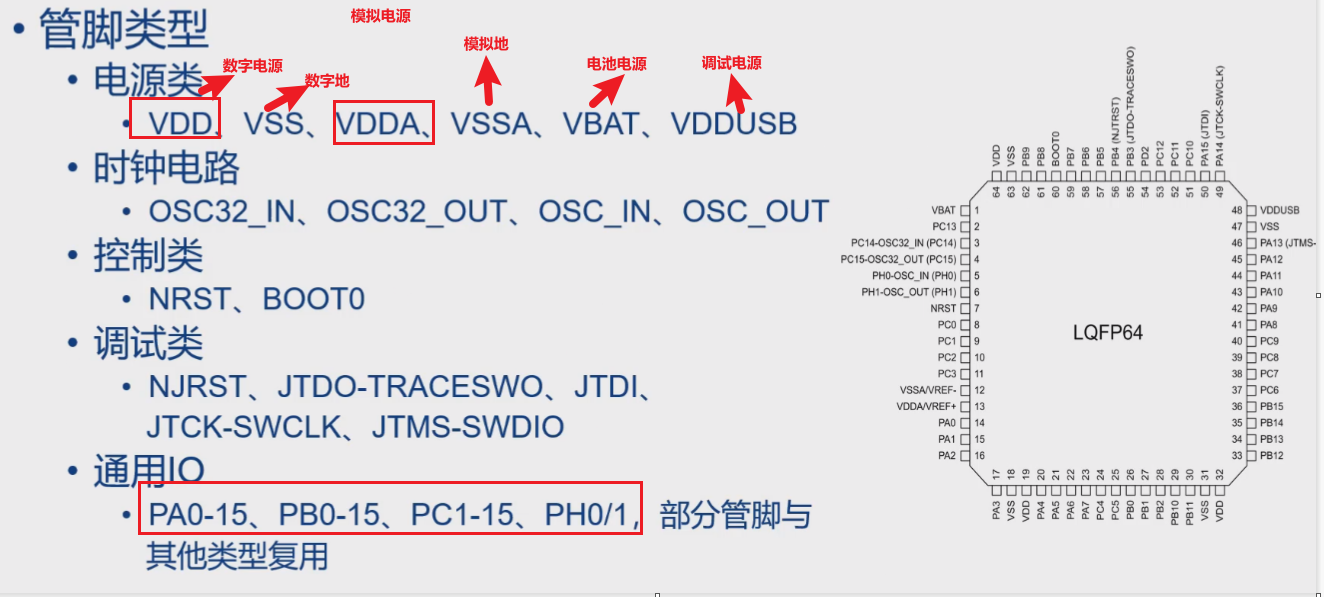

12.10 、引脚

12.10.1 、引脚说明

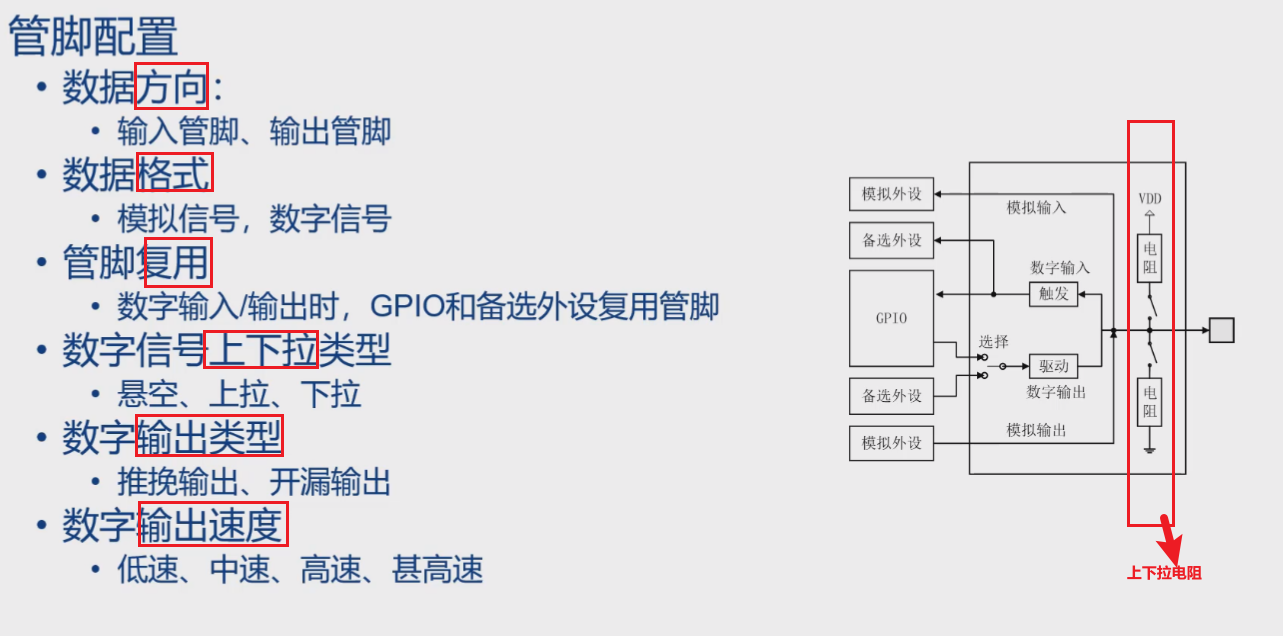

12.10.2 、引脚配置

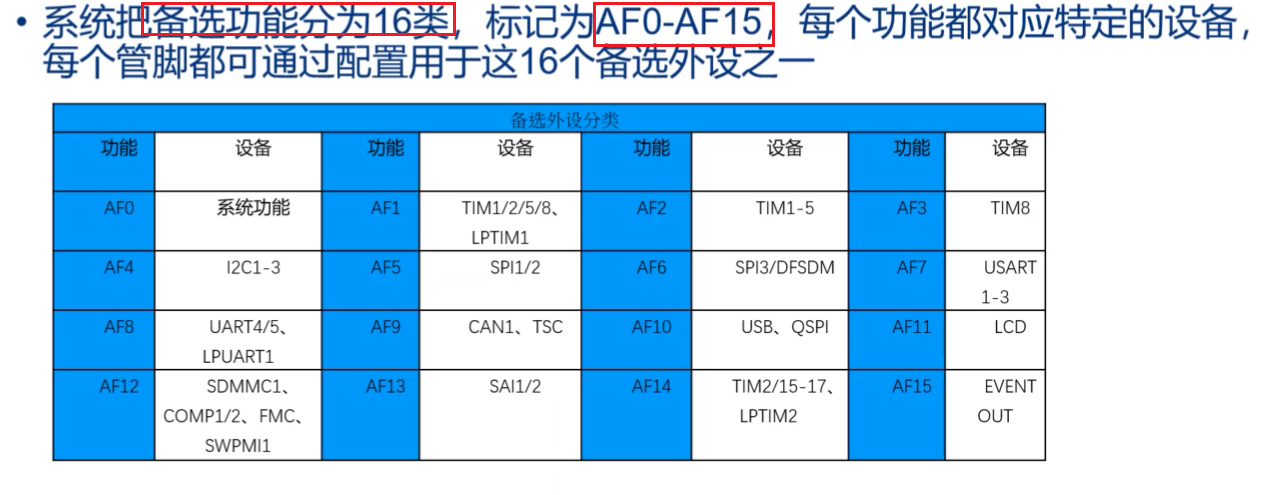

12.10.3 、管脚复用及重映射

举例:

12.10.4 、启动引脚

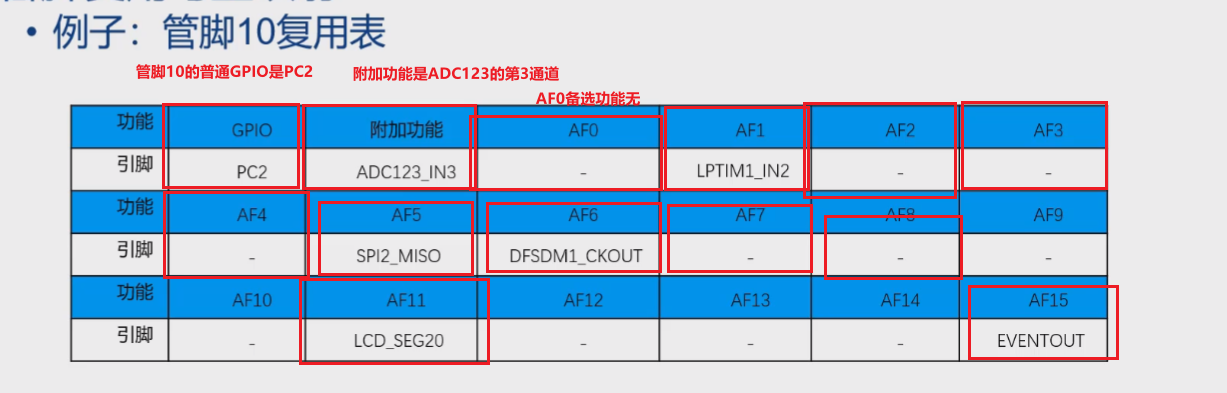

12.11 、中断

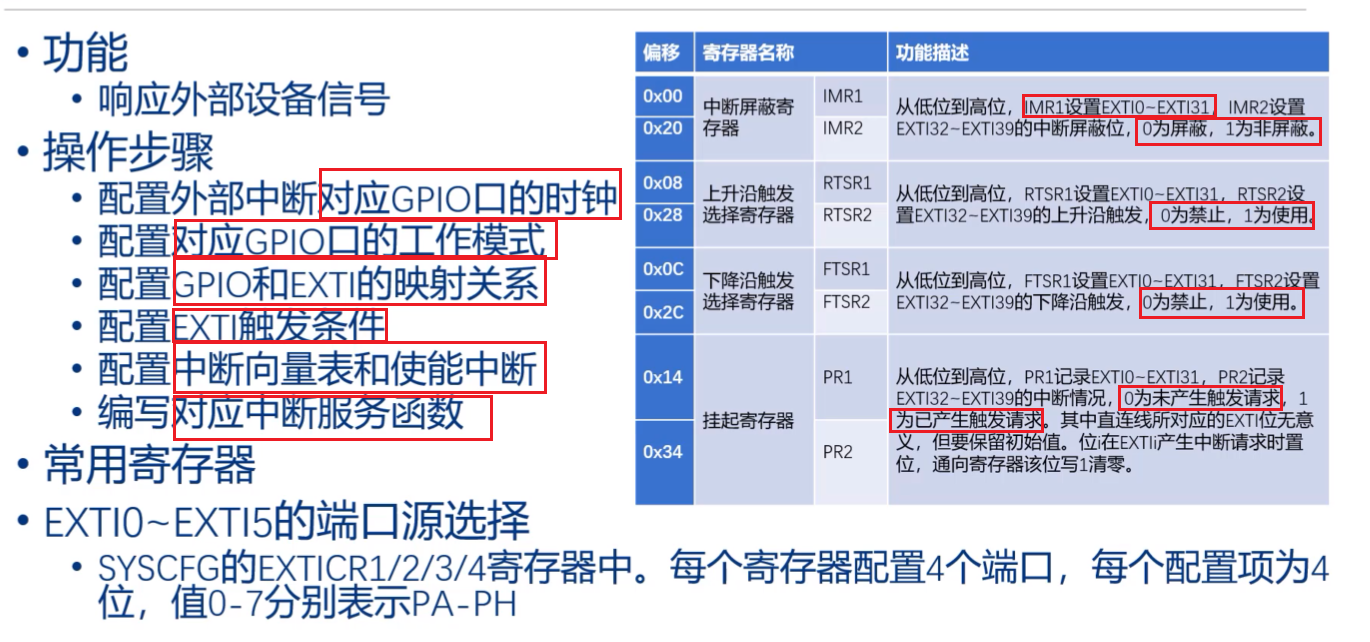

12.11.1 、中断源

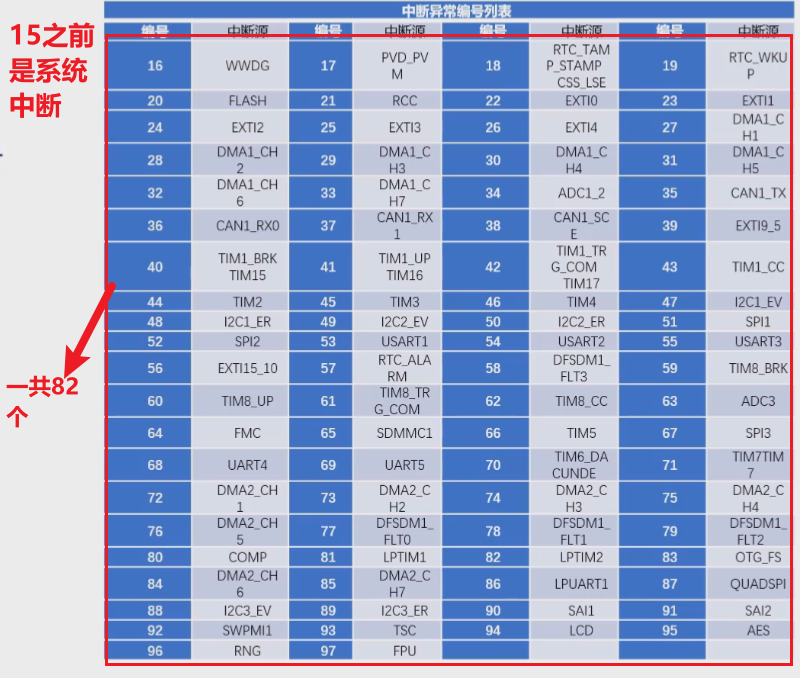

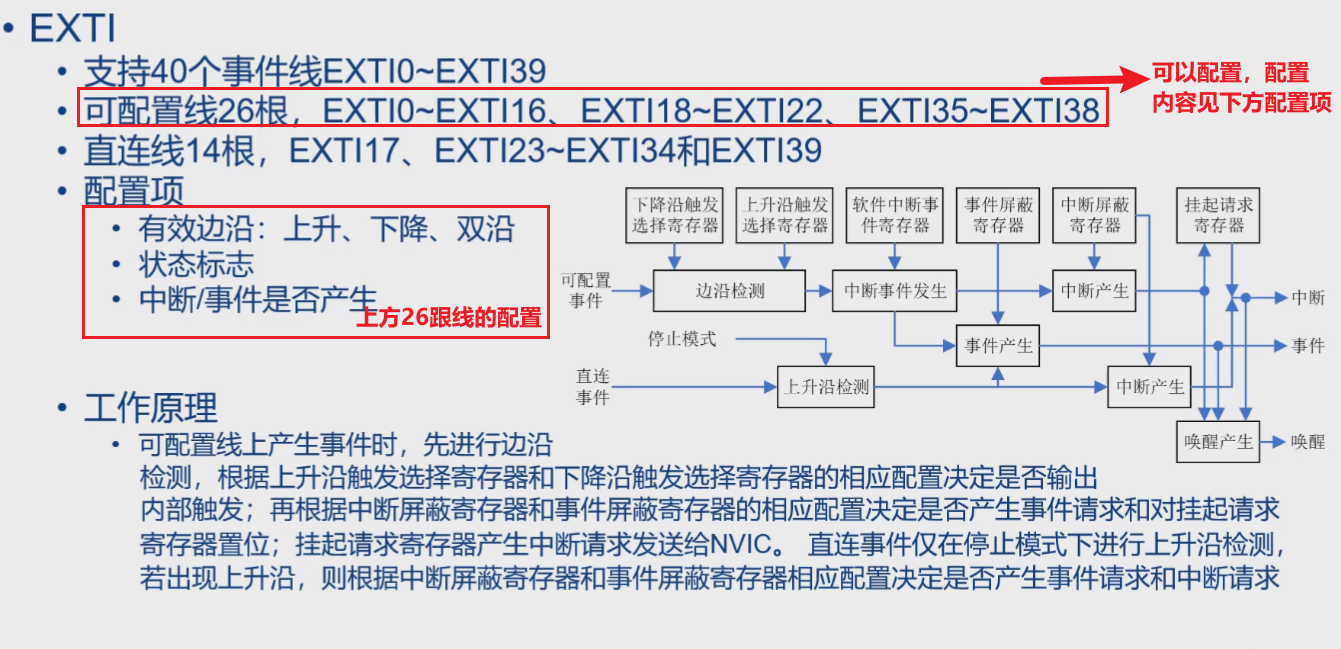

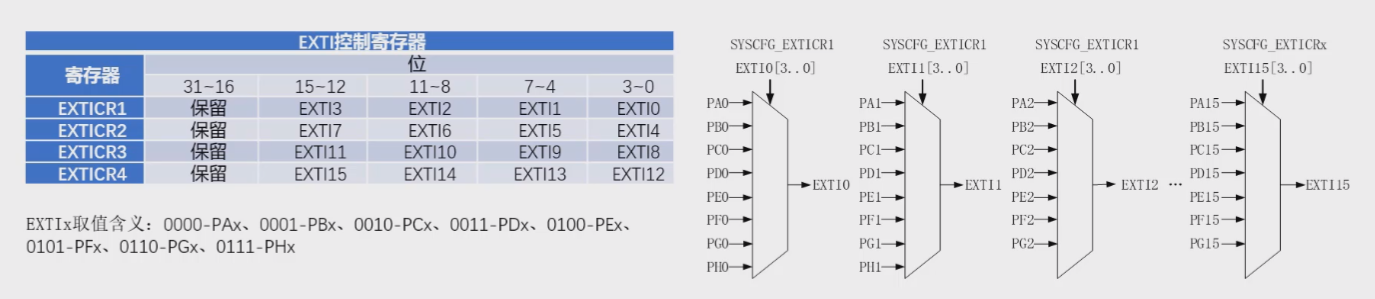

12.11.2 、外部中断线

12.11.3 、外部中断线选择

12.11 、GPIO

12.11.1 、GPIO寄存器类别

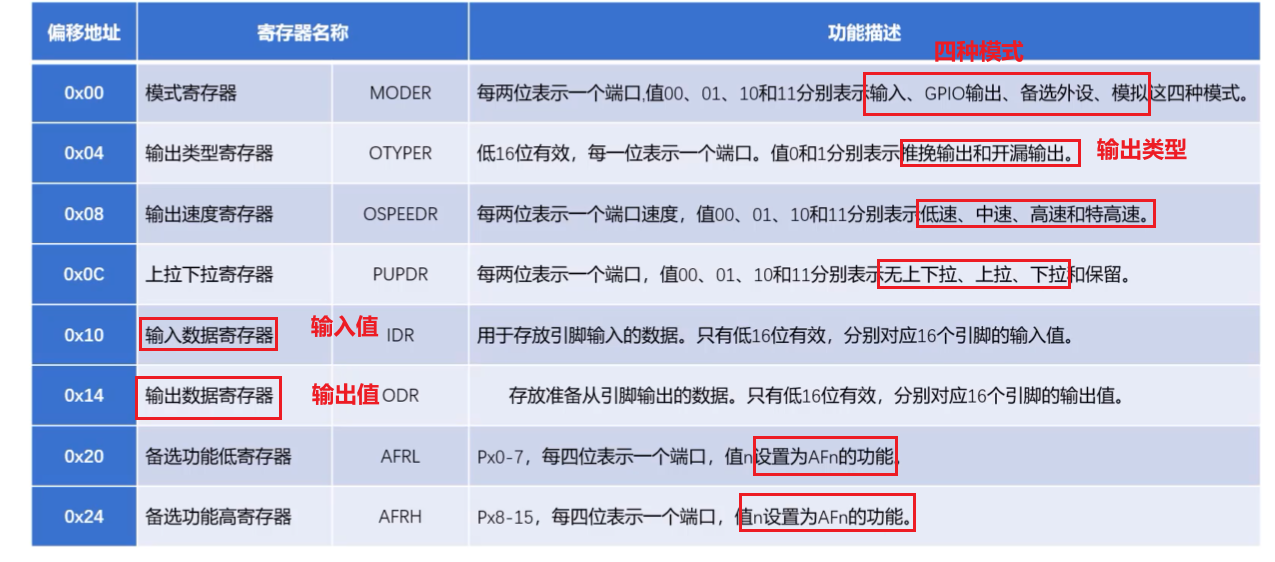

12.11.2 、常用寄存器

- 推挽输出:

能真正的输出高电平和低电平,在两种电平下都具有驱动能力。

优点:

驱动能力,就是指输出电流的能力。对于驱动大负载(即负载内阻越小,负载越大)时,例如IO输出为5V,驱动的负载内阻为10ohm,于是根据欧姆定律可以正常情况下负载上的电流为0.5A(推算出功率为2.5W)。显然一般的IO不可能有这么大的驱动能力,也就是没有办法输出这么大的电流。于是造成的结果就是输出电压会被拉下来,达不到标称的5V。当然如果只是数字信号的传递,下一级的输入阻抗理论上最好是高阻,也就是只需要传电压,基本没有电流,也就没有功率,于是就不需要很大的驱动能力。

缺点:

缺点是: 如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS闭合时;同时另一个输出低电平,即上面的MOS闭合,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。

- 开漏输出(Open Drain Output):

开漏输出无法真正输出高电平,即高电平时没有驱动能力,需要借助外部上拉电阻完成对外驱动

优势一:

开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

优势二:

开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

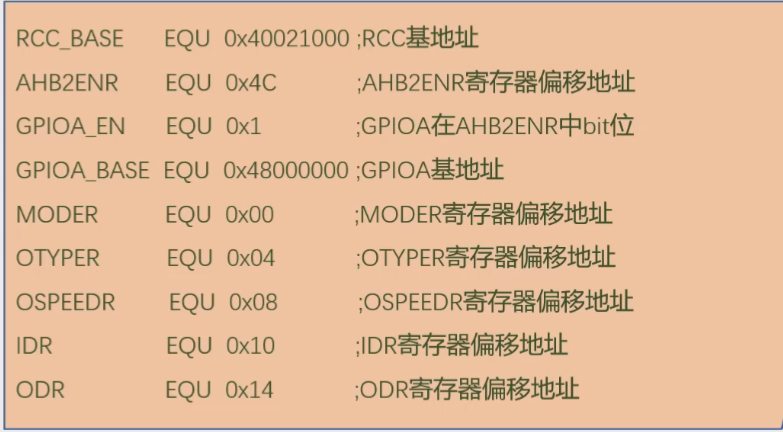

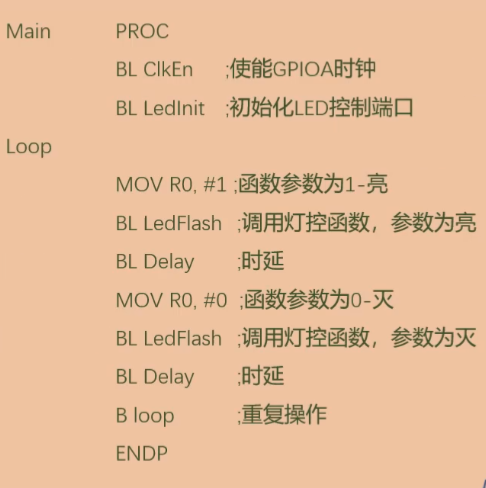

12.11.3 、GPIO的程序设计

(1)定义寄存器

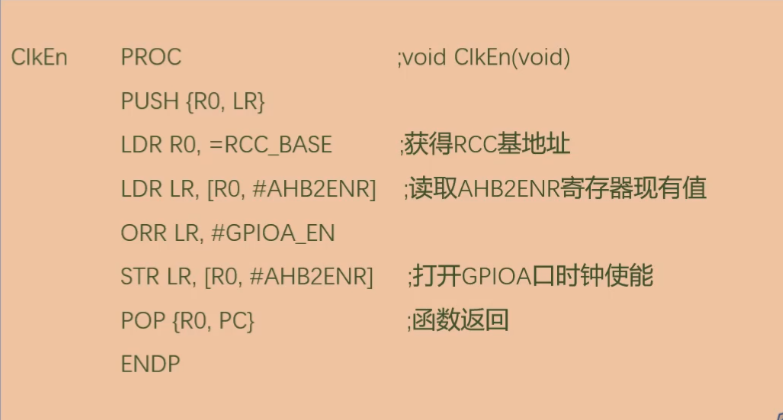

(2)时钟使能

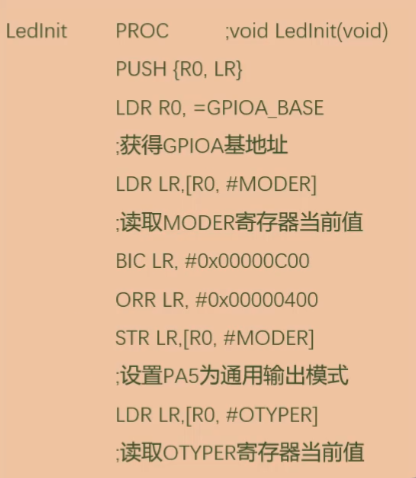

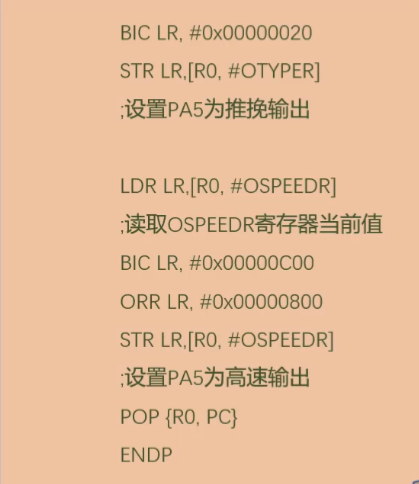

(3)GPIO配置

(4)GPIO高低电平输出

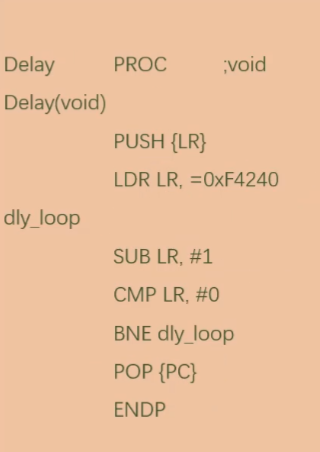

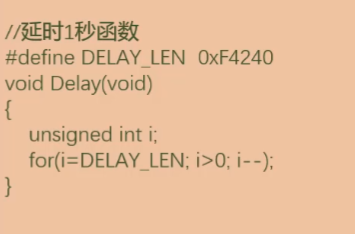

(5)延时1S函数

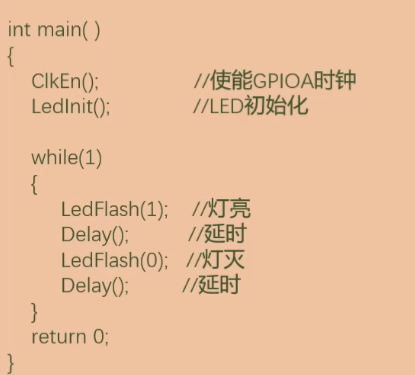

(6)main程序函数

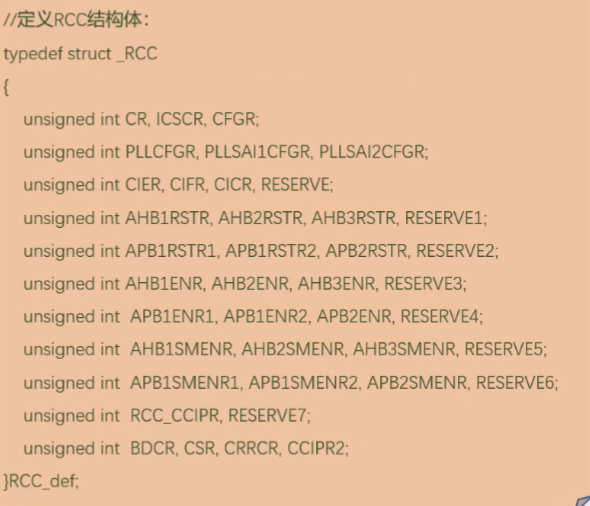

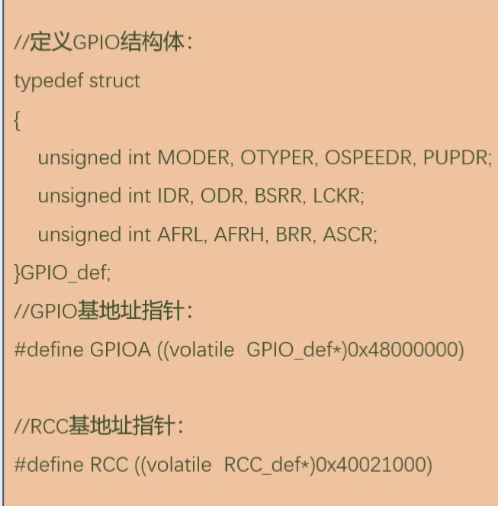

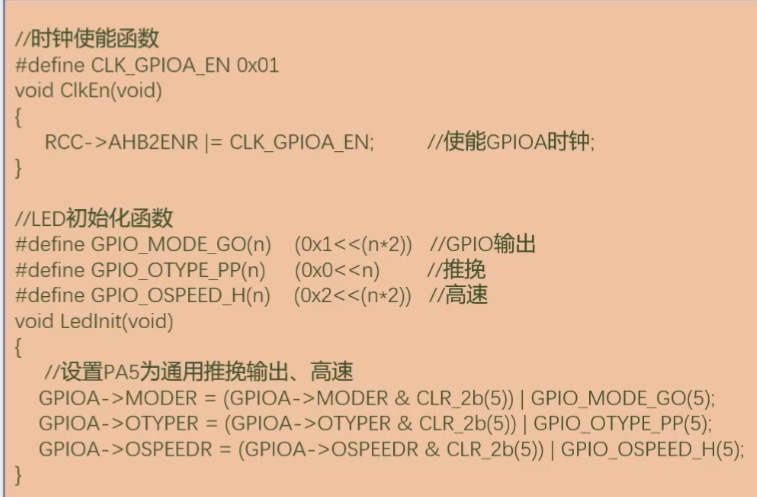

12.11.4 、C程序实现GPIO的配置

RCC结构体

GPIO结构体

时钟使能、GPIO配置

GPIO高低电平输出

延时1S函数

main程序函数

12.12 、EXTI

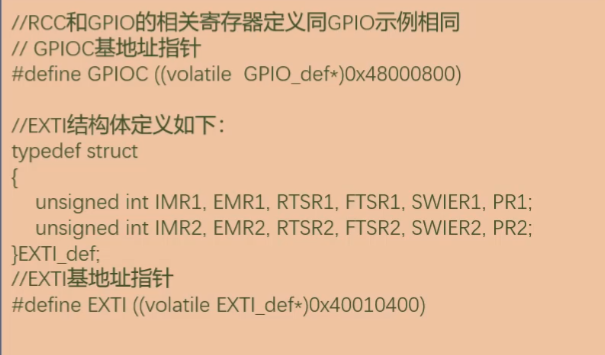

12.12.1 、EXTIEXTI结构体定义

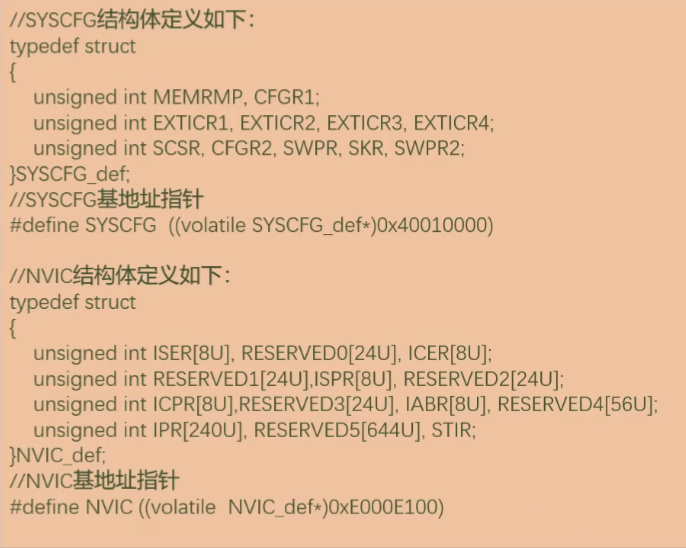

12.12.2 、SYSCFG、NVIC结构体定义

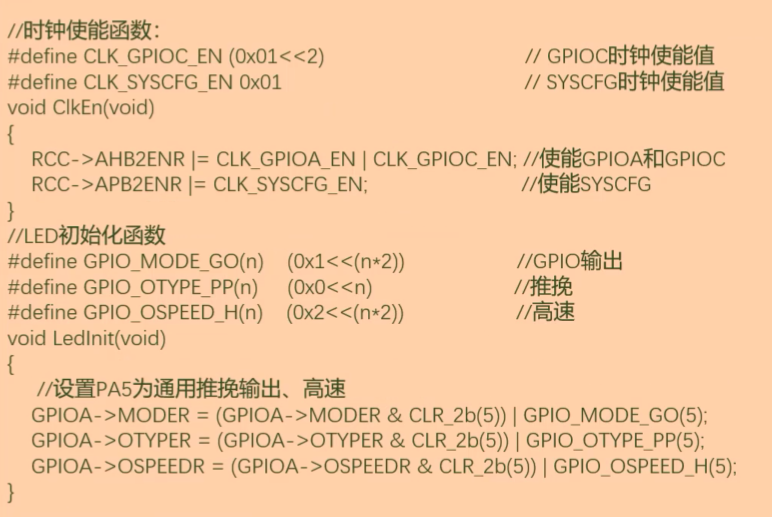

12.12.3 、GPIO时钟使能、GPIO配置

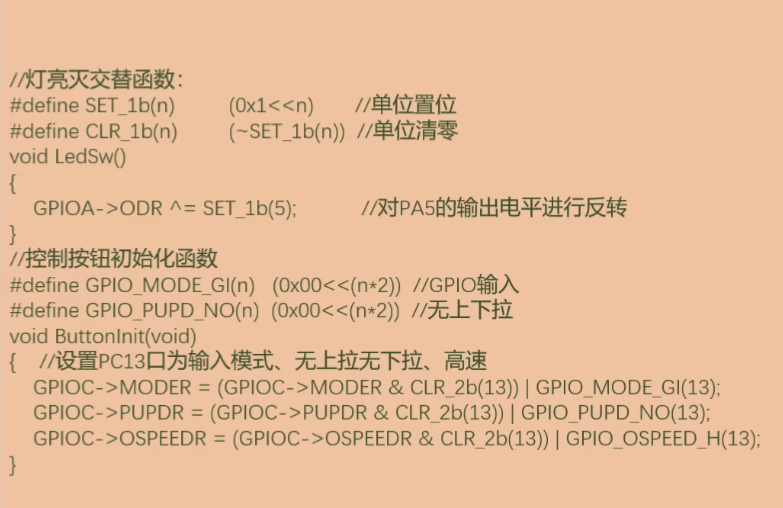

12.12.4 、KEY配置

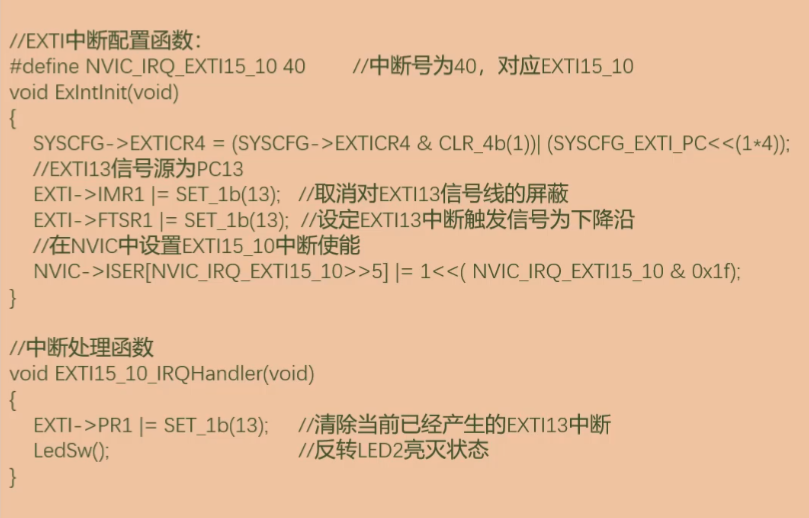

12.12.5 、中断配置函数、中断处理函数

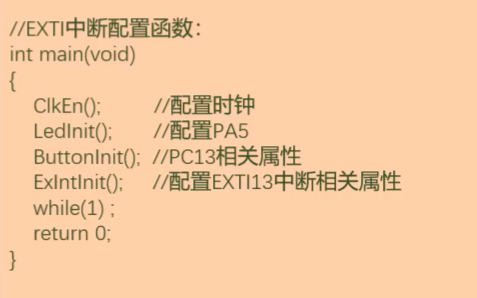

12.12.6 、主函数

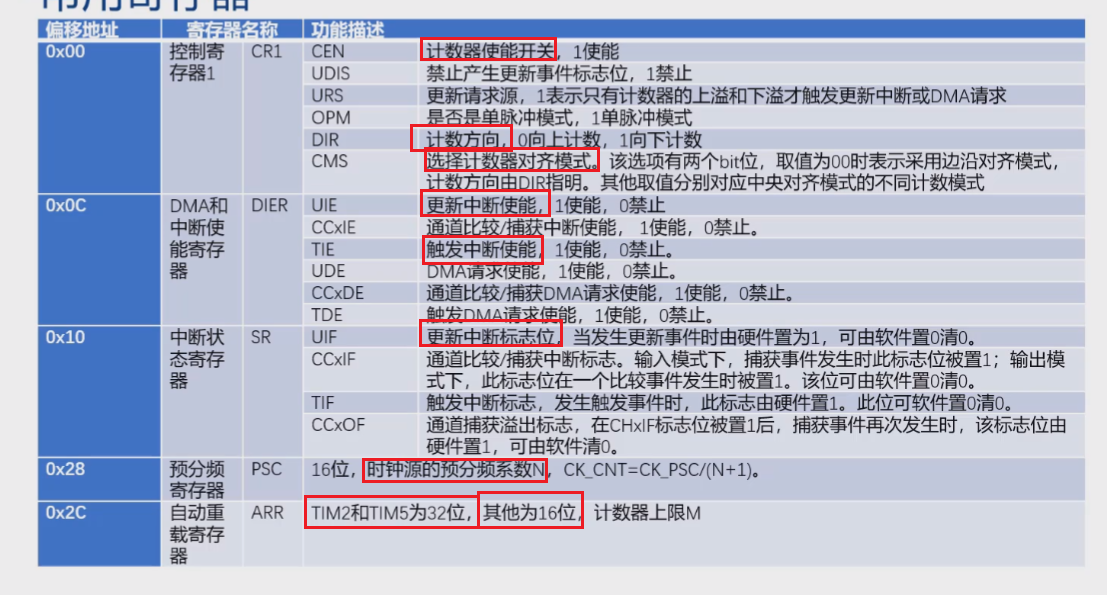

12.13 、通用定时器

12.13.1 、操作步骤

12.13.2 、常用寄存器

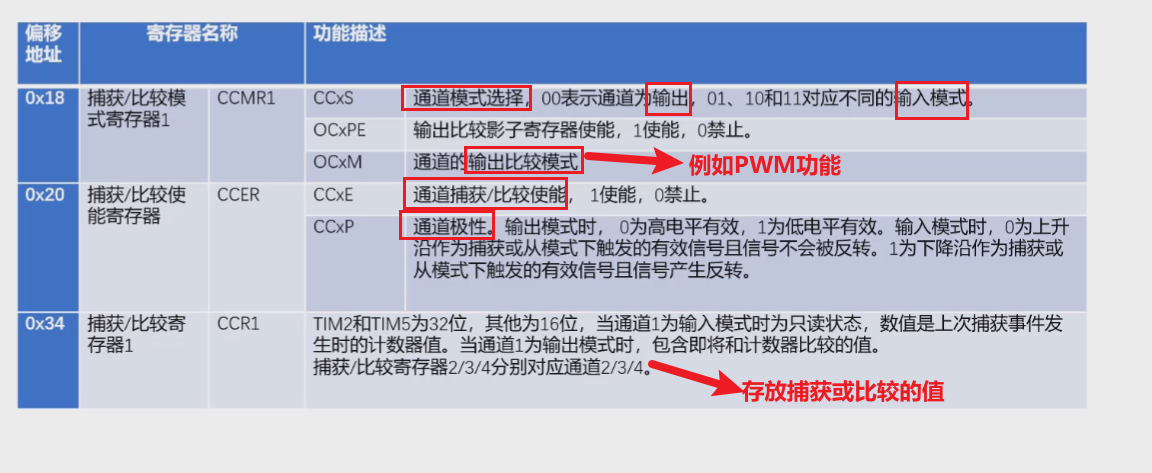

12.13.3 、捕获/比较寄存器

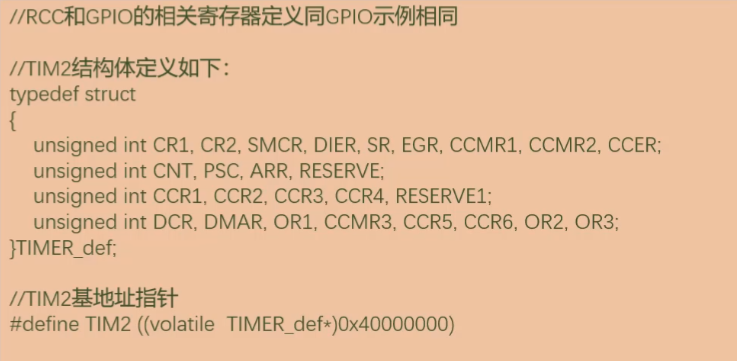

定时器结构体定义

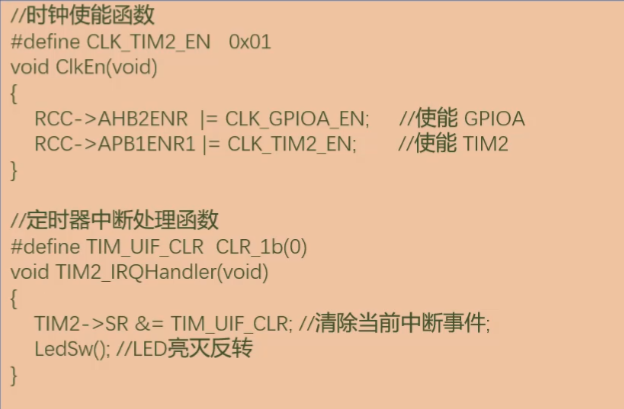

定时器使能、定时器中断处理函数

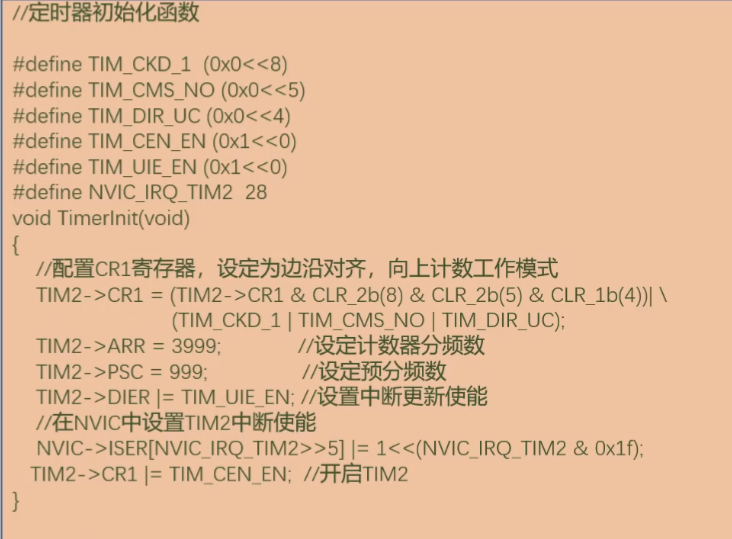

定时器初始化

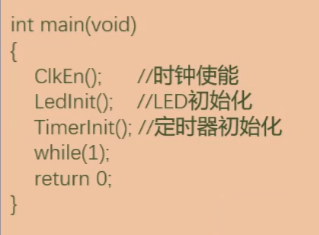

主函数

GPIO输出复用

PWM配置

12.13 、USART

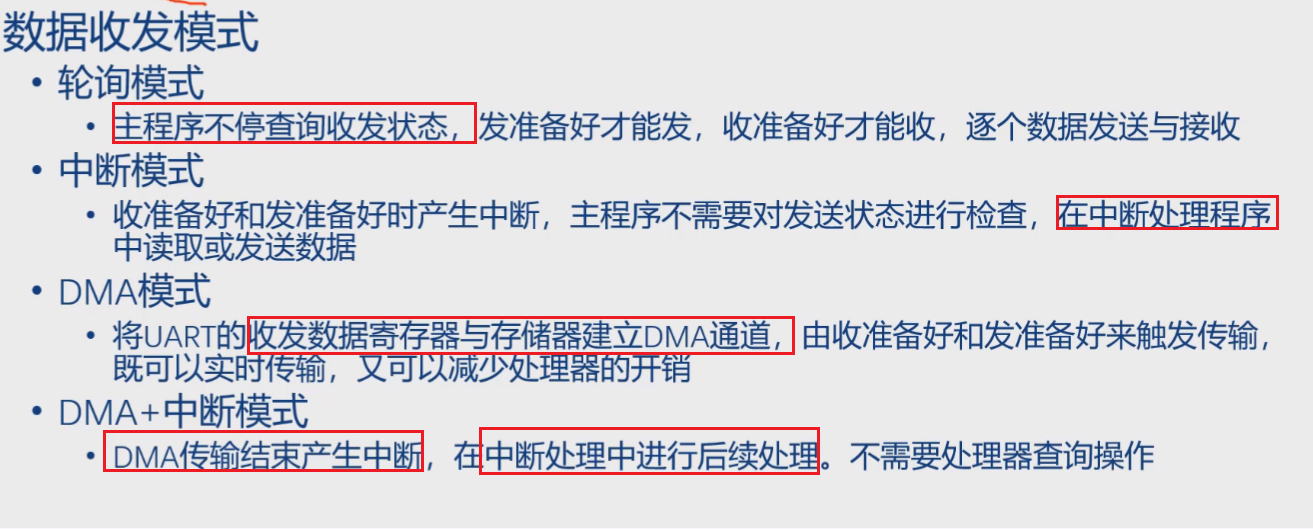

12.13.1 、USART数据收发模式

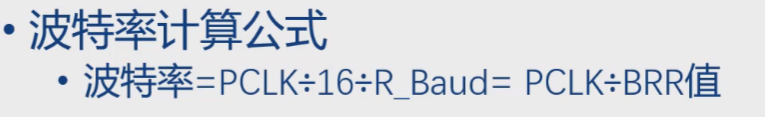

12.13.2 、波特率计算

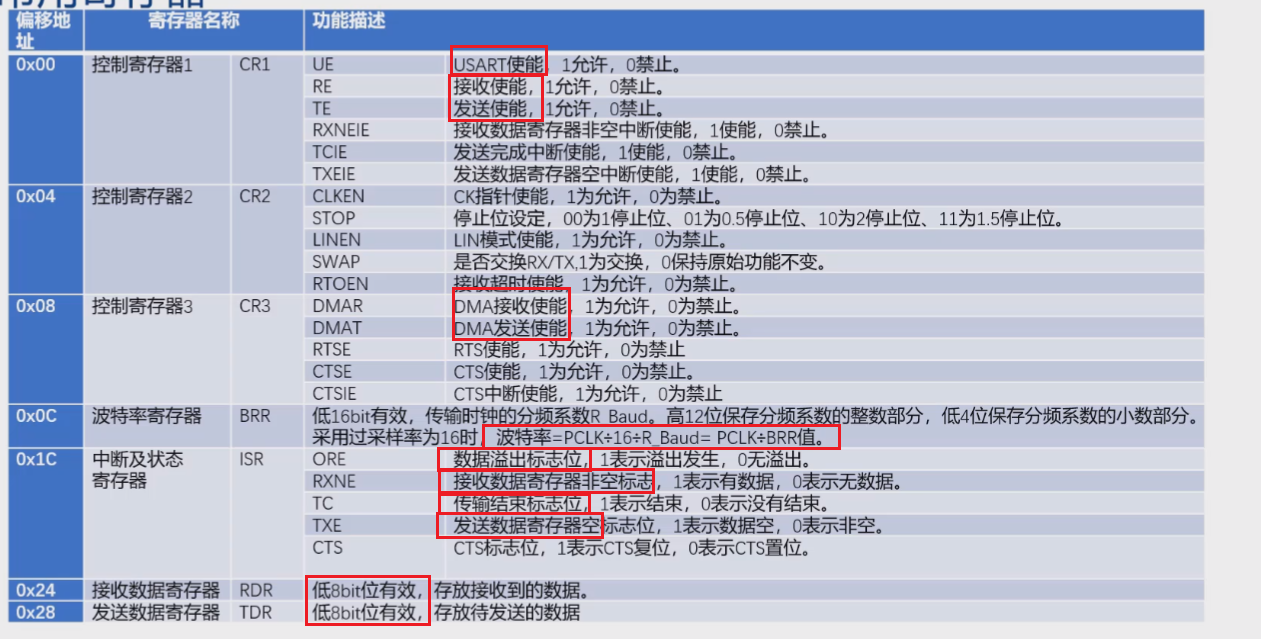

12.13.3 、常用寄存器

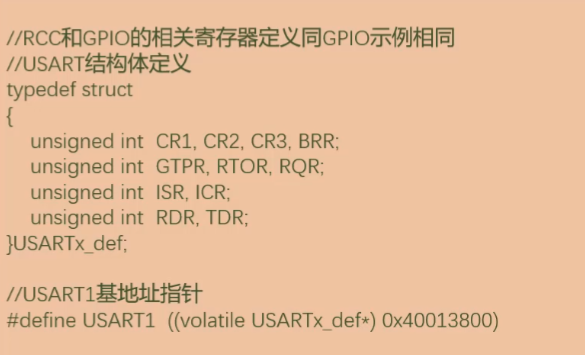

USART结构体定义

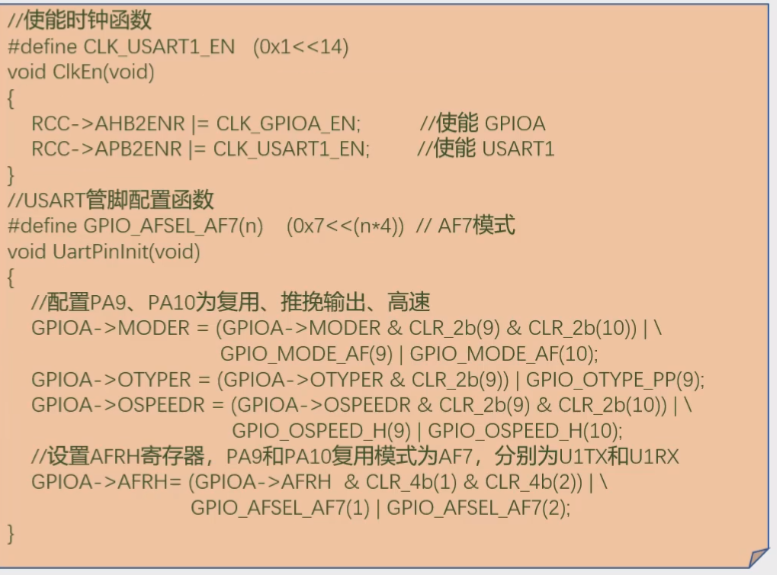

USART引脚配置

USART初始化

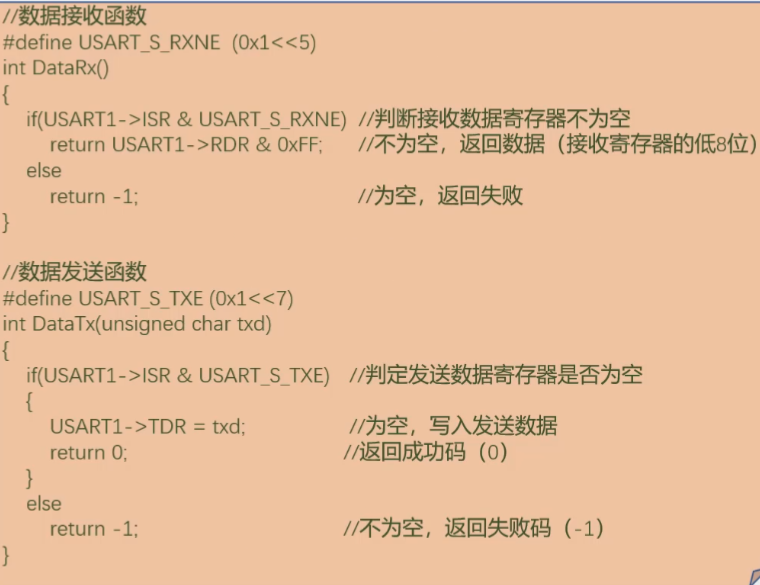

USART数据接收/发送函数(轮询方式)

主函数

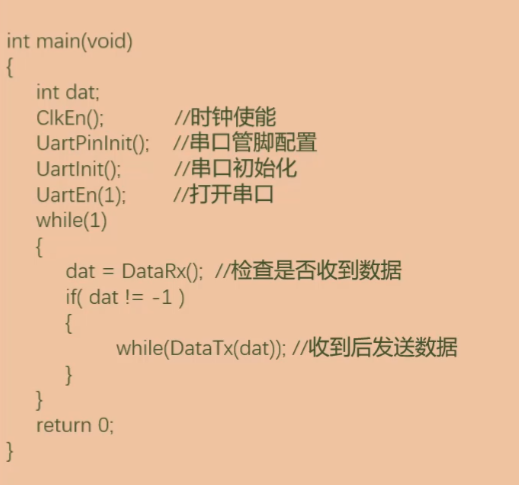

USART数据接收/发送中断处理函数(中断方式)

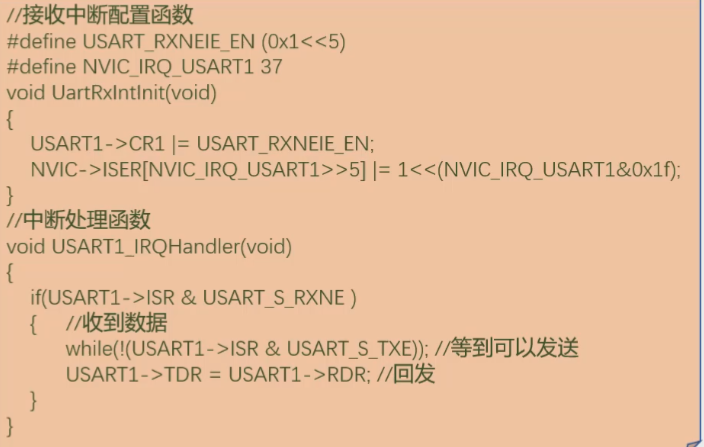

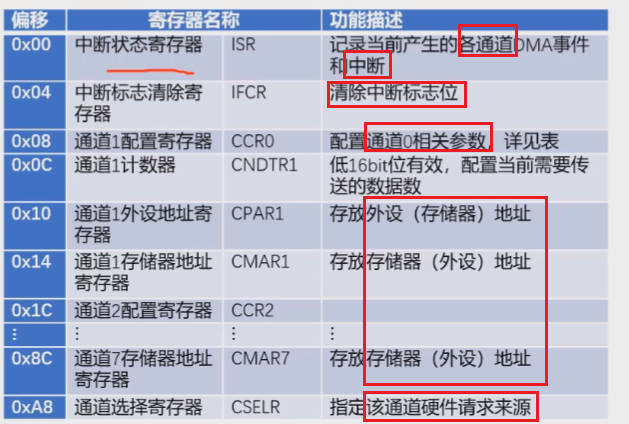

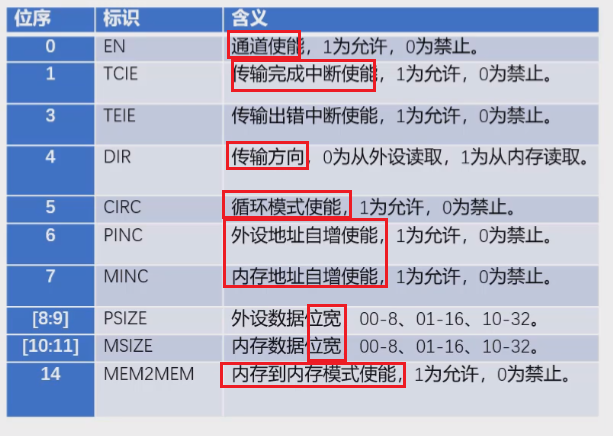

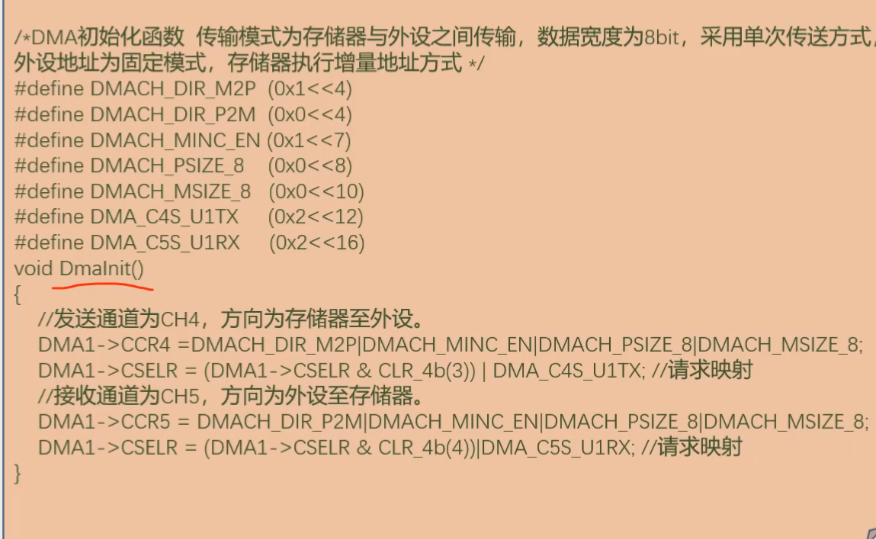

12.14 、DMAC

12.14.1 、DMAC操作步骤

12.14.2 、DMAC常用寄存器

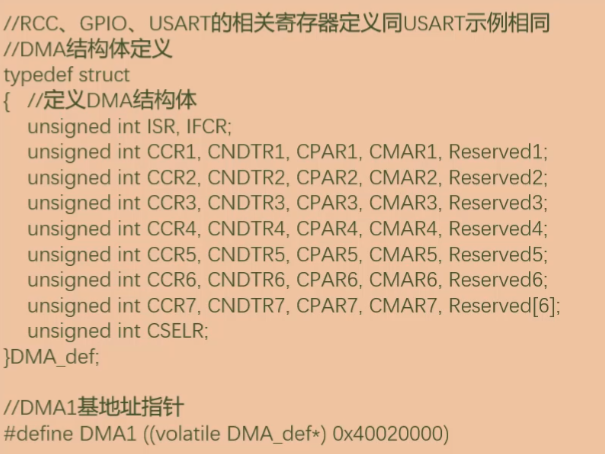

DMA结构体定义

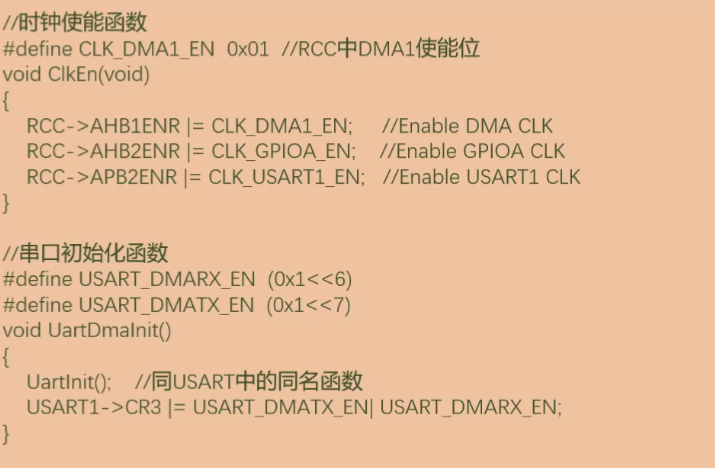

USART配置

DMA初始化

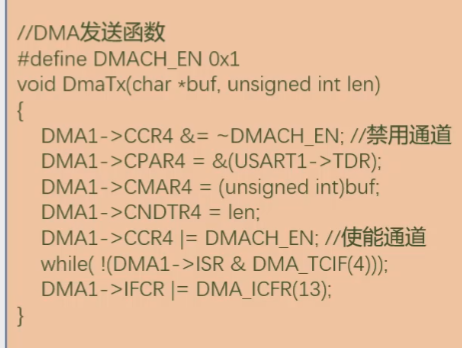

DMA发送函数

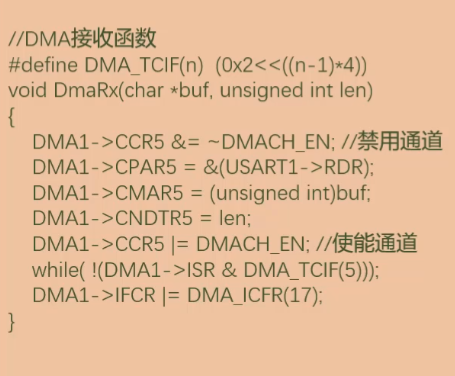

DMA接收函数

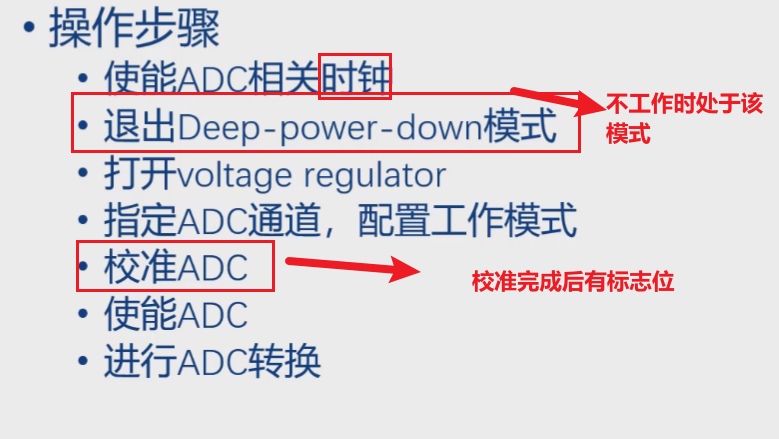

12.15 、ADC

12.15.1 、ADC操作步骤

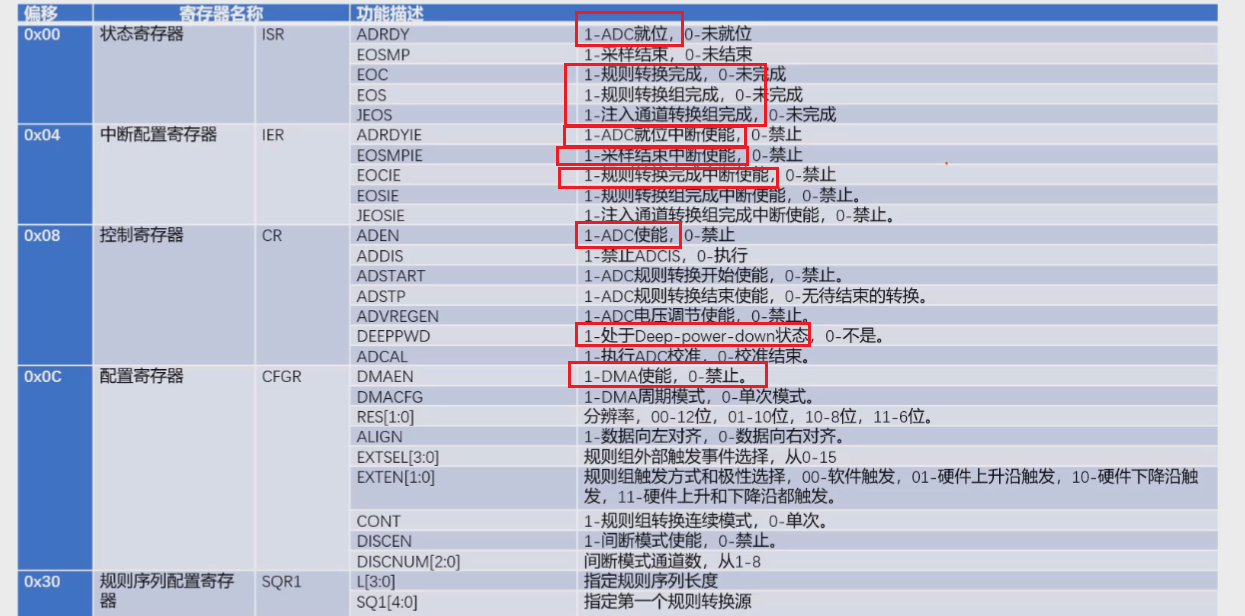

12.15.2 、ADC常用寄存器

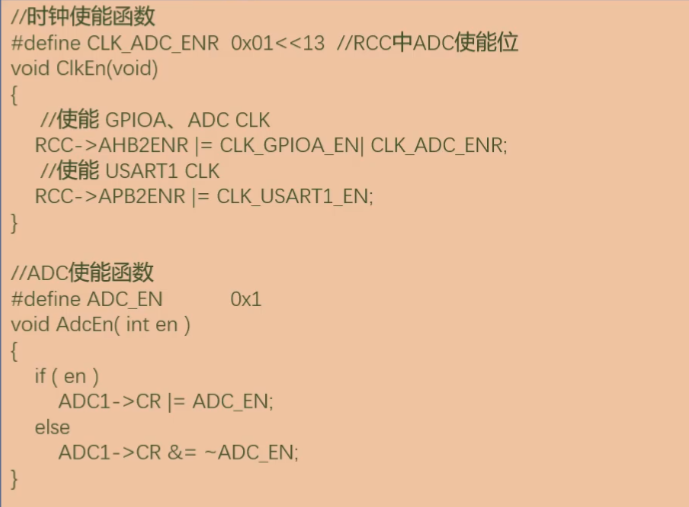

ADC结构体定义

ADC管脚配置

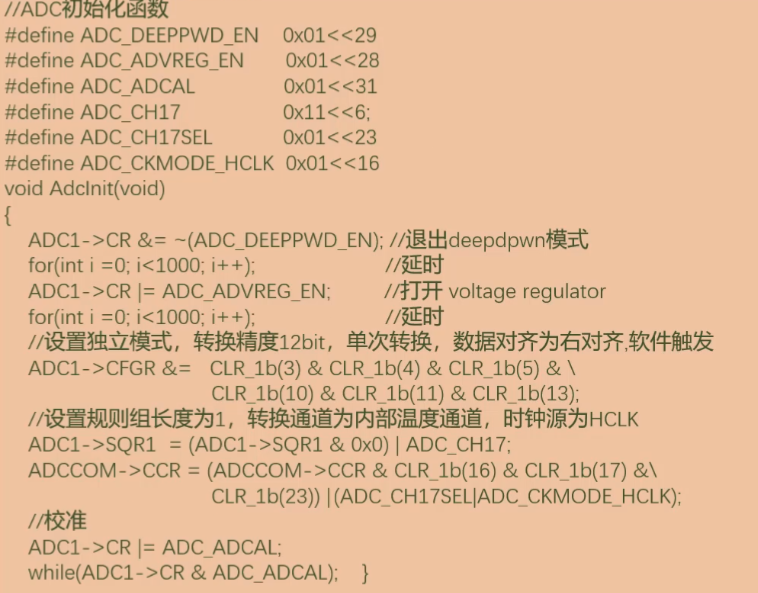

ADC初始化

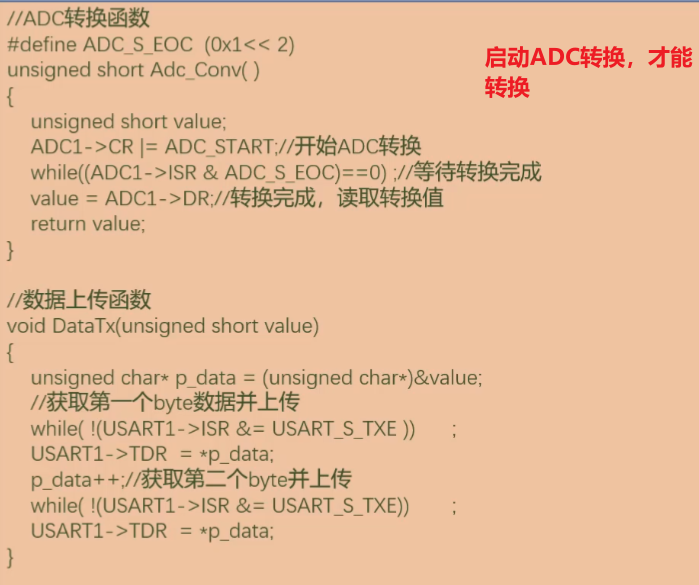

ADC转换和数据上传

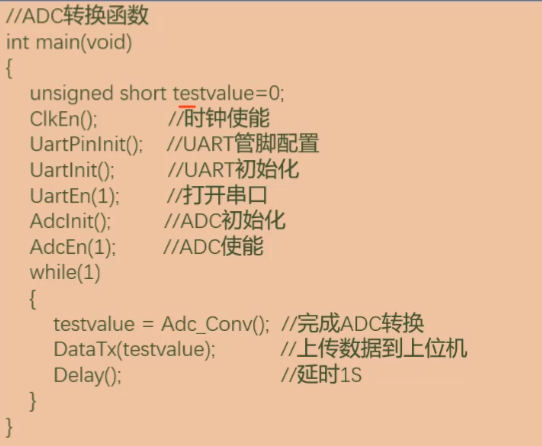

主函数

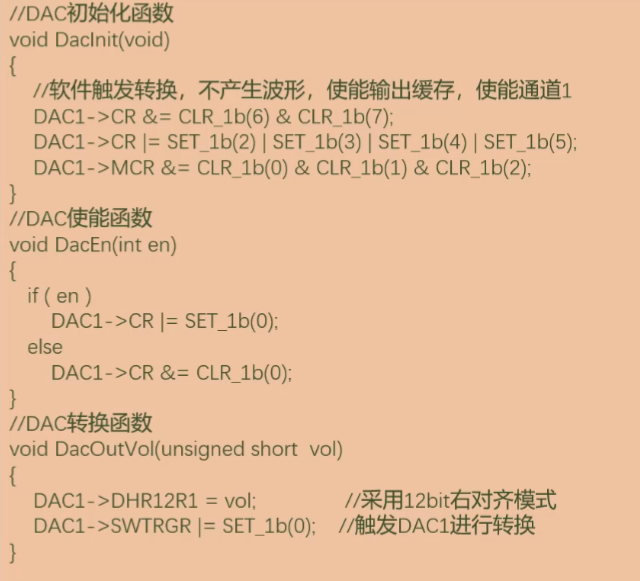

12.16 、DAC

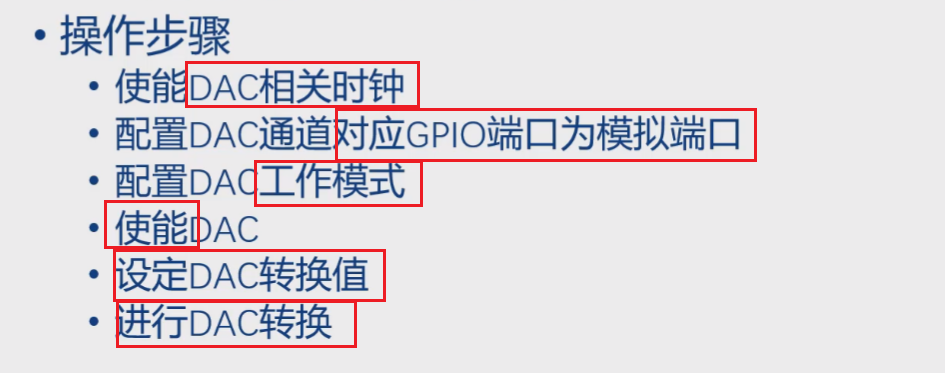

12.16.1 、DAC操作步骤

12.16.2 、DAC常用寄存器

设计要求:

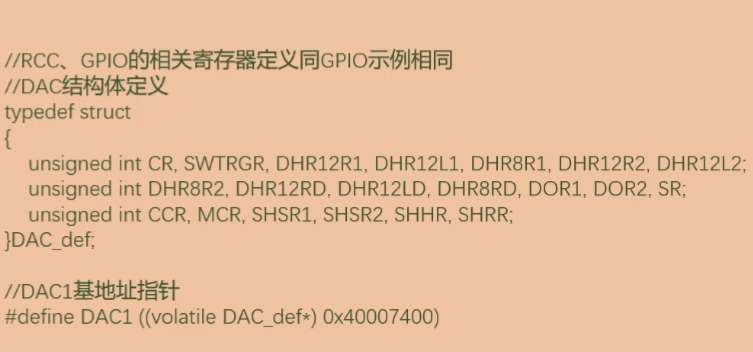

DAC结构体定义

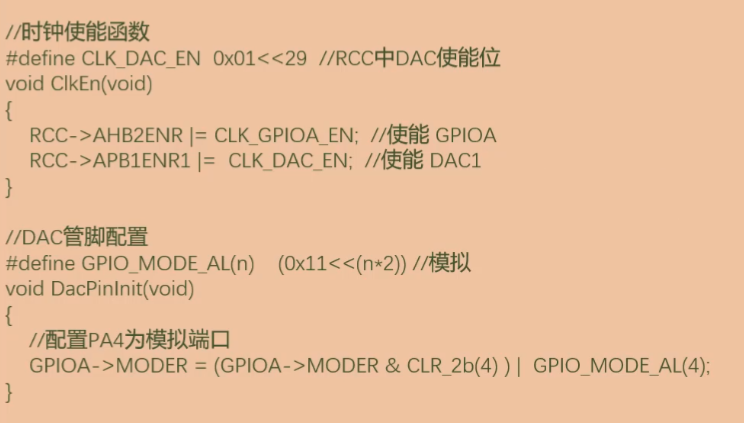

GPIO时钟使能、引脚配置

DAC初始化

主程序

本文来自博客园,作者:登云上人间,转载请注明原文链接:https://www.cnblogs.com/lj15941314/p/17330216.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号