数电基础 第四章

数电基础 第四章

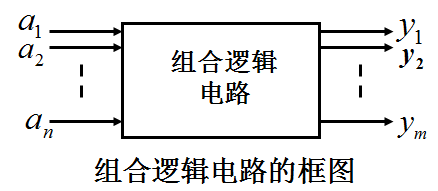

组合逻辑电路

组合逻辑电路的特点

1.从功能上 :任意时刻的输出仅取决于该时刻的输入

2.从电路结构上:不含记忆(存储)元件

逻辑功能的描述

组合逻辑电路的设计方法

1.逻辑抽象

分析因果关系,确定输入/输出变量

定义逻辑状态的含意(赋值)

列出真值表

2.写出函数式

3.选定器件类型

4.根据所选器件:对逻辑式化简,变换,或进行相应的描述

5.画出逻辑电路图

设计举例

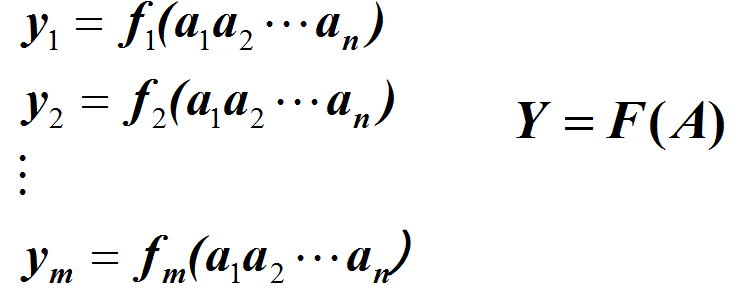

设计一个监视交通信号灯状态的逻辑电路

1.抽象

输入变量:红(R)、黄(A)、绿(G)

输出变量:故障信号(Z)

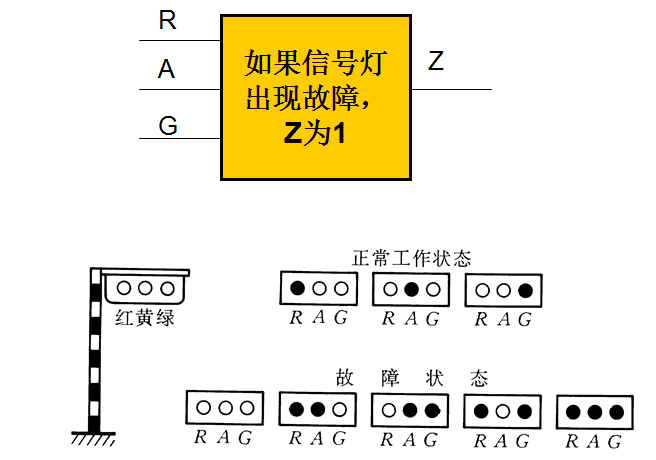

| 输入变量 | 输出 | ||

|---|---|---|---|

| R | A | G | Z |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

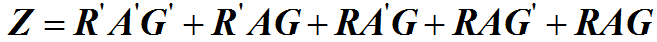

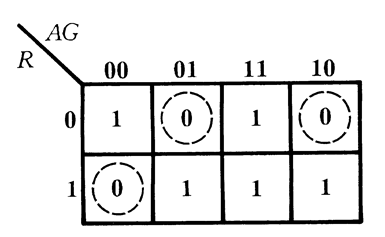

2.写出逻辑表达式

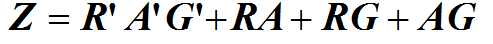

3.选用小规模SSI器件

4.化简

5.画出逻辑图

若干常用组合逻辑电路

编码器

编码:将输入的每个高/低电平信号变成一个对应的二进制代码

普通编码器

特点:任何时刻只允许输入一个编码信号。

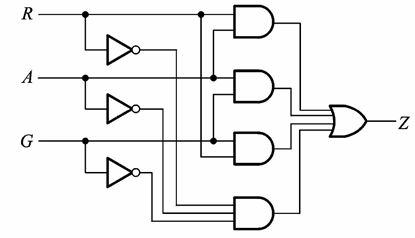

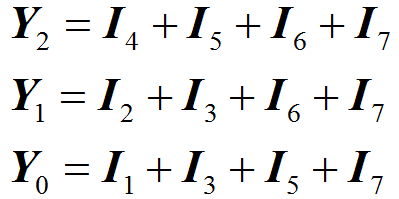

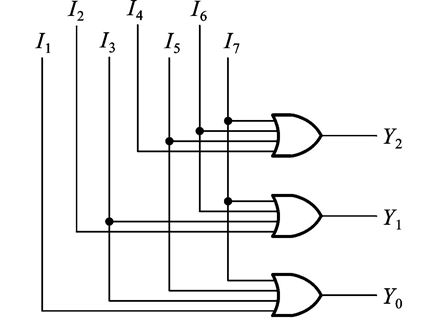

例:3位二进制普通编码器

| 输 入 | 输 出 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| I0 | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Y2 | Y1 | Y0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|

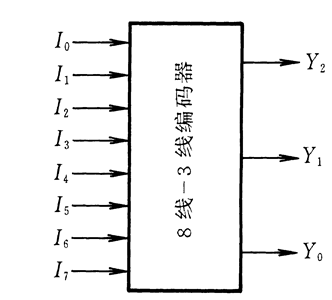

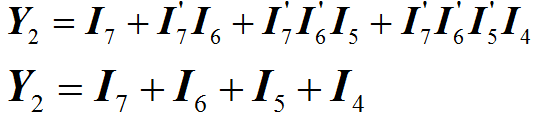

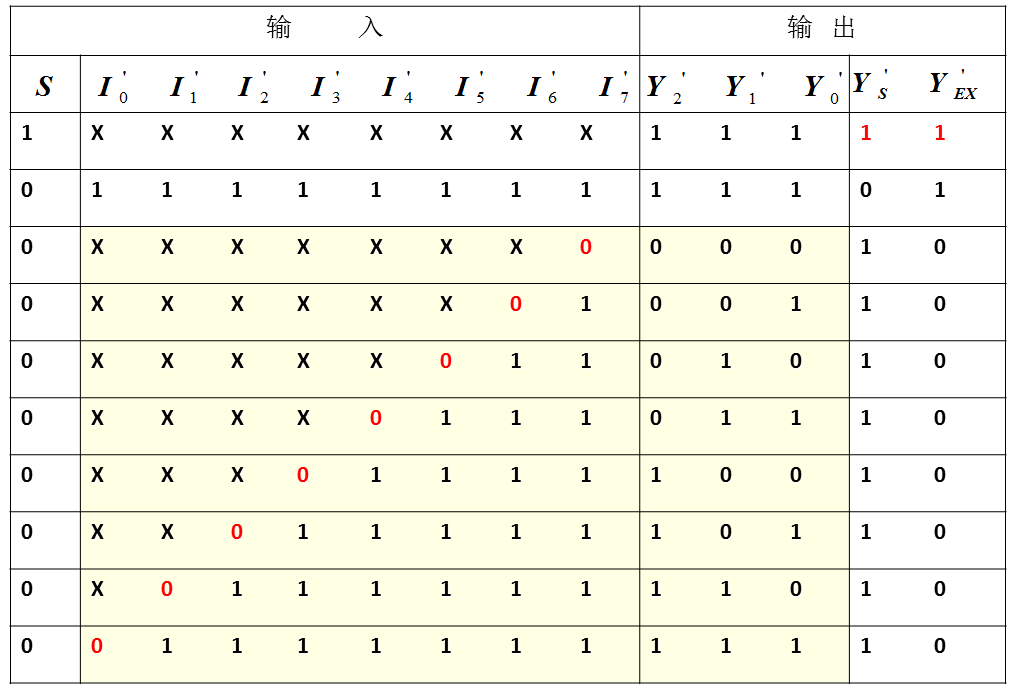

优先编码器

特点:允许同时输入两个以上的编码信号,但只对其中优先权最高的一个进行编码。

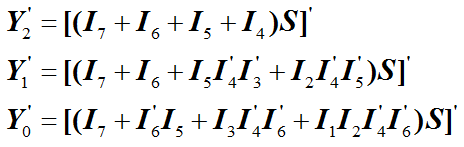

例:8线-3线优先编码器(设I7优先权最高…I0优先权最低)

| 输 入 | 输 出 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| I0 | I1 | I2 | I3 | I4 | I5 | I6 | I7 | Y2 | Y1 | Y0 |

| X | X | X | X | X | X | X | 1 | 1 | 1 | 1 |

| X | X | X | X | X | X | 1 | 0 | 1 | 1 | 0 |

| X | X | X | X | X | 1 | 0 | 0 | 1 | 0 | 1 |

| X | X | X | X | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| X | X | X | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| X | X | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| X | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

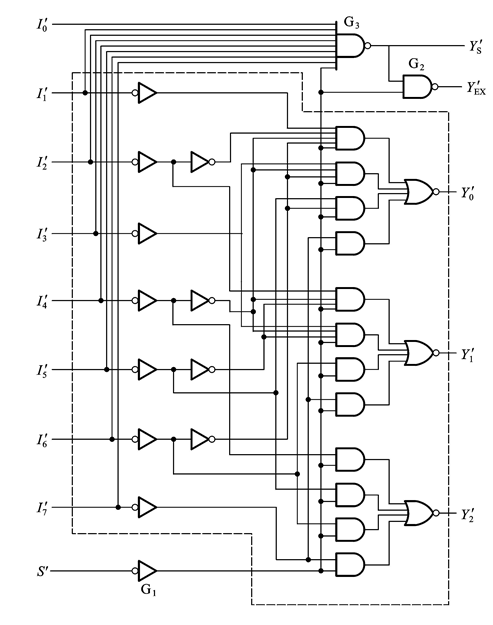

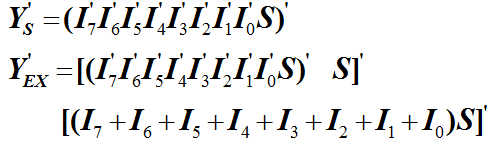

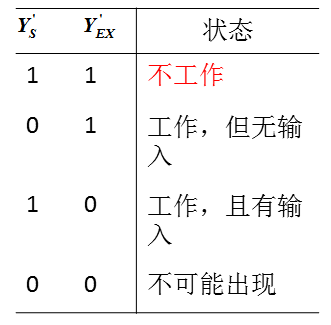

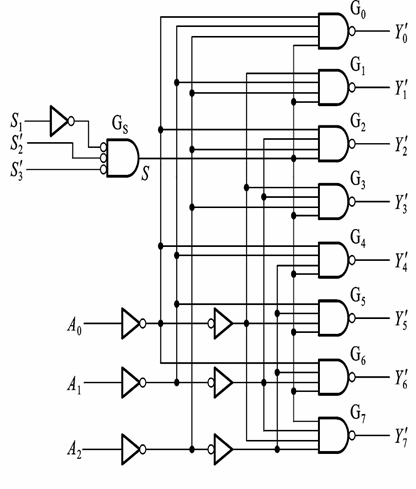

实例:74HC148

S`为选通信号

Ys`为0时电路工作无编码输入

YEX`为0时,电路工作有编码输入

附加输出信号的状态及含意

控制端扩展功能举例

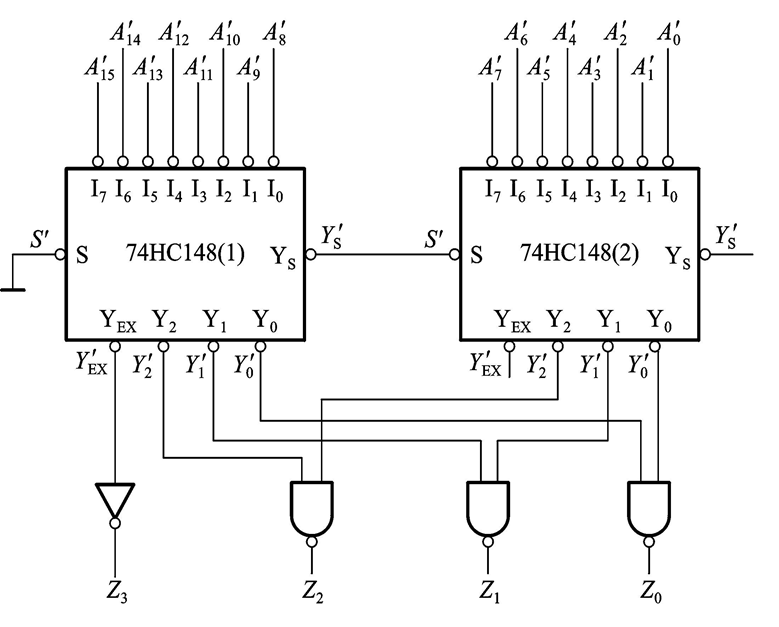

用两片8线-3线优先编码器扩展16线-4线优先编码器

第一片为高优先权

只有(1)无编码输入时,(2)才允许工作

第(1)片![]()

时表示对

的编码

低3位输出应是两片的输出的“或”

译码器

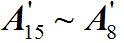

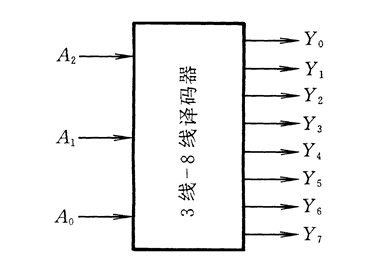

译码:将每个输入的二进制代码译成对应的输出高、低电平信号。

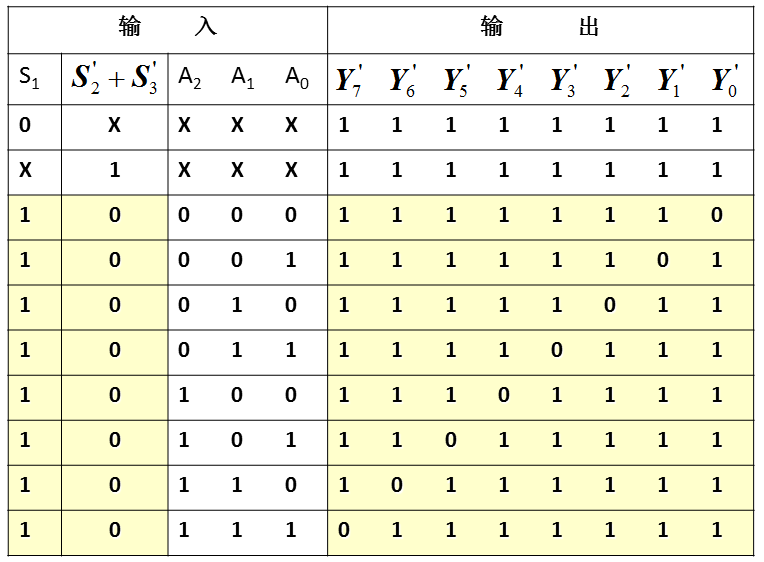

集成译码器实例:74HC138

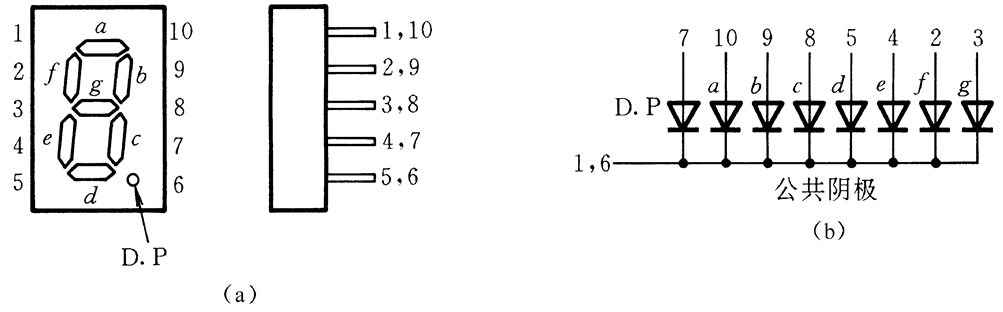

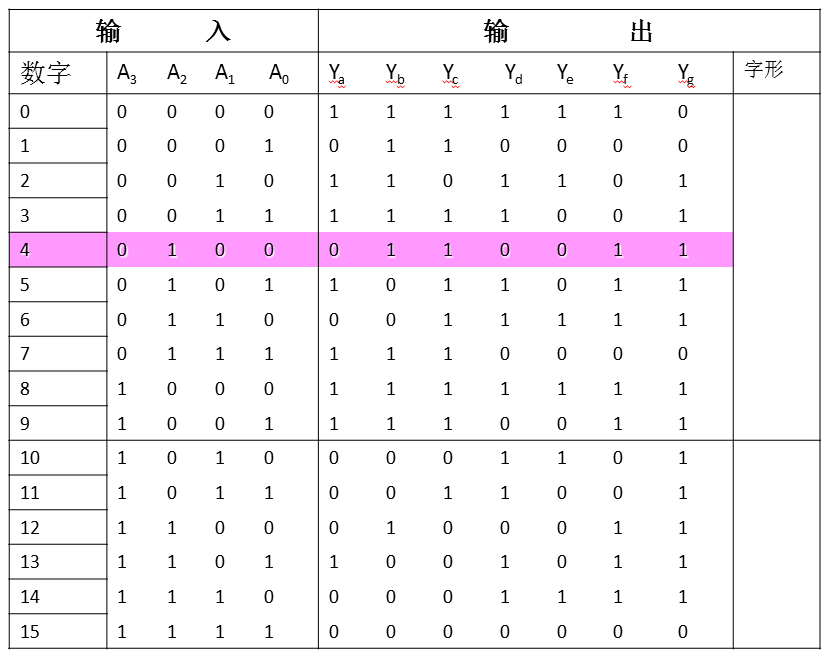

显示译码器

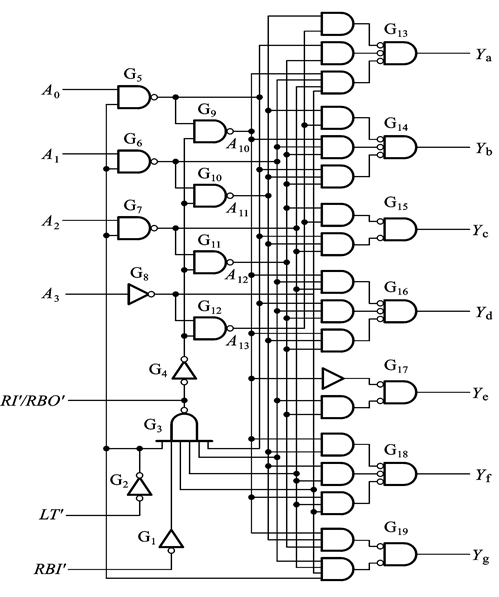

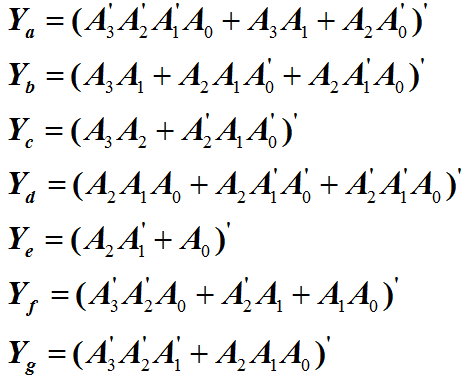

七段显示译码器7448的逻辑图

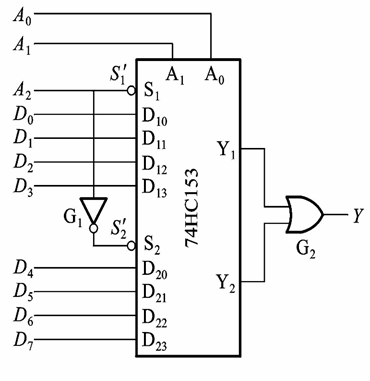

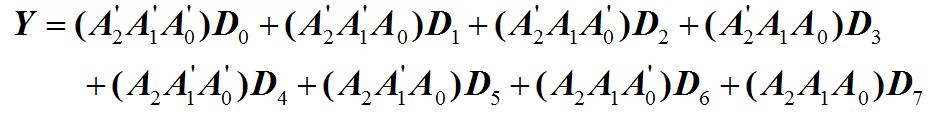

数据选择器

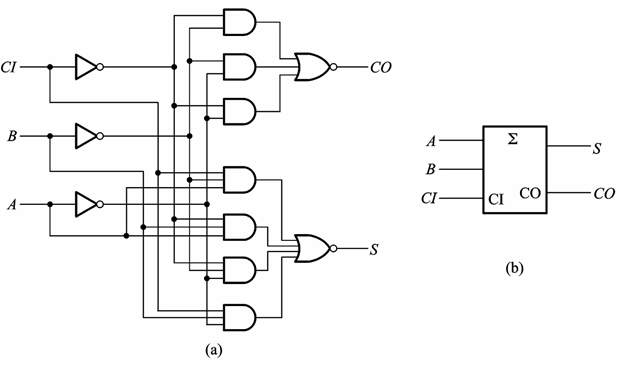

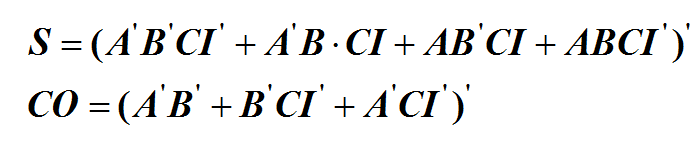

加法器

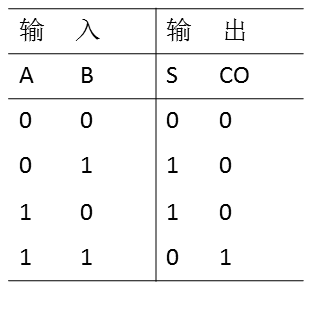

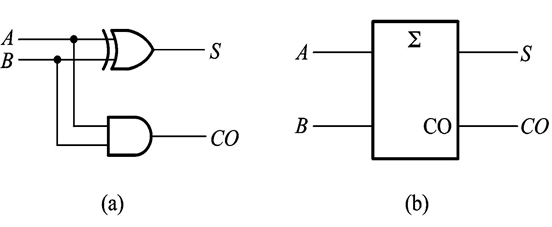

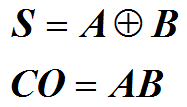

半加器,不考虑来自低位的进位,将两个1位的二进制数相加

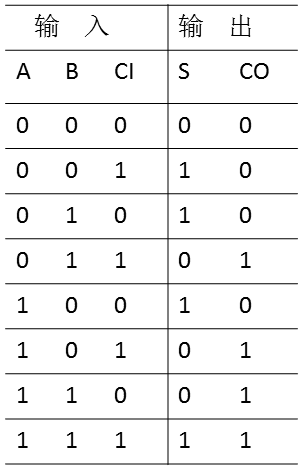

全加器:将两个1位二进制数及来自低位的进位相加

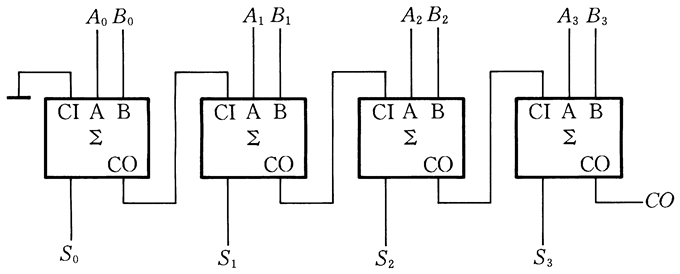

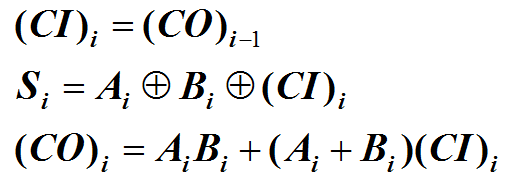

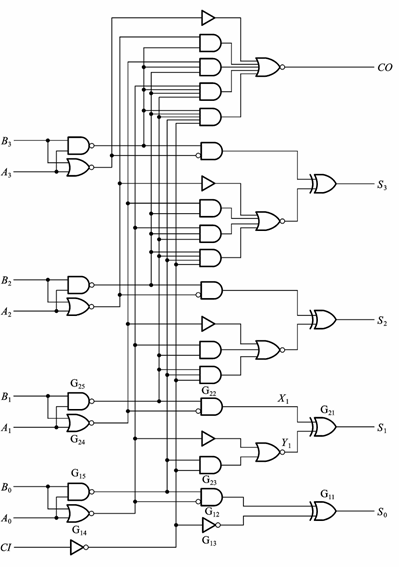

多位加法器

串行进位加法器

超前进位加法器

基本原理:加到第i位的进位输入信号是两个加数第i位以前各位(0 ~ j-1)的函数,可在相加前由A,B两数确定。

优点:快,每1位的和及最后的进位基本同时产生。

缺点:电路复杂。

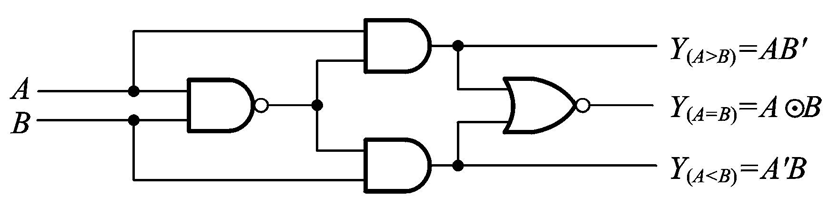

数值比较器

用来比较两个二进制数的数值大小

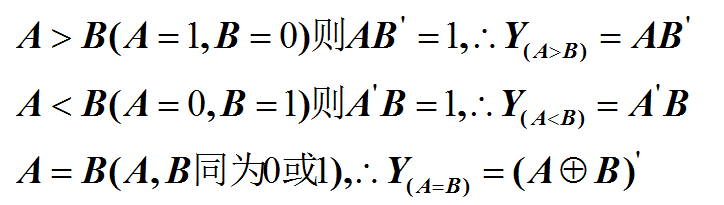

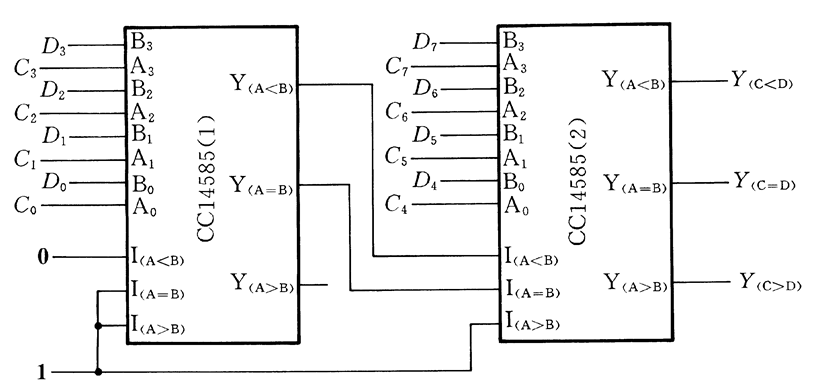

多位数值比较器

原理:从高位比起,只有高位相等,才比较下一位。

比较两个8位二进制数的大小

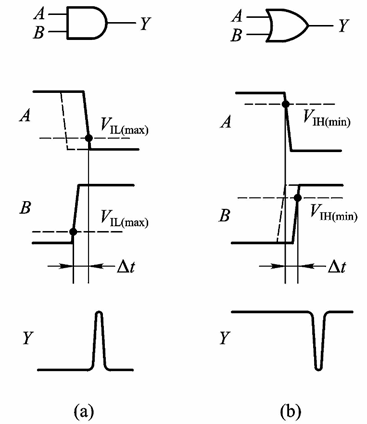

组合逻辑电路中的竞争-冒险现象

两个输入“同时向相反的逻辑电平变化”,称存在“竞争”

因“竞争”而可能在输出产生尖峰脉冲的现象,称为 “竞争-冒险”。

浙公网安备 33010602011771号

浙公网安备 33010602011771号