gate_clock、clock_gating cell 时序仿真

低功耗设计时,有时需要插入gate_clock,

其中一种办法是在RTL设计上,用lib库里的clock_gating cell替换时钟使能控制。

1、RTL仿真

clock_gating cell如果导入lib中的model,model内clk_out相对clk_in往往有预估的输出延迟,而其他的RTL设计没有延时,

有可能会导致时钟和数据不同步,造成仿真不通过。

=》所以在RTL仿真时,需要写一个RTL级的clock_gating cell model,专门用于仿真,避免时钟数据不同步问题。

2、DC综合仿真

RTL设计中,如果clock_gating cell输出时钟驱动模块大多,DC综合又还没加入clk_tree,

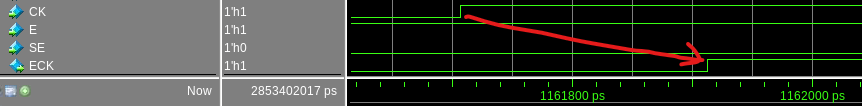

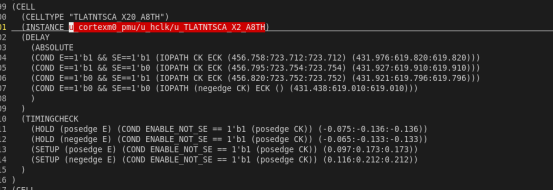

会造成DC综合后clock_gating cell负载太大,抽取的sdf输出延迟非常大。下图cell输出延时达几百ns:

如果超过半个时钟周期,clock_gating cell将不会有输出;

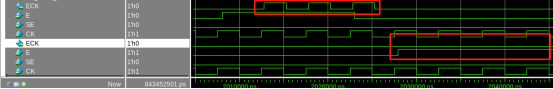

可以看到下图下半部分Enable使能之后,ECK还是没有输出。

=》遇到这种问题,可以先手动修改sdf文件,将输出延迟修改较小,先通过仿真验证功能是否正确;

=》前端工程师一定要告知后端对clock_gating cell输出时钟做clk_tree,插入clk_tree之后,负载太大的问题应该会自动解决,

布图后再仿真,确定没有问题。

3、添加门控时钟正确步骤

(1)代码设计手动添加时钟门控cell;

(2)dc_shell综合,添加set_ideal_network约束,否则sdf的load非常大;

(3)生成sdc时,删除set_ideal_network约束,否则后端布图时将把其当做理想时钟。

(4)形式验证时,加上 set verification_clock_gate_hold_mode collapse_all_cg_cells,否则gate-clock验证可能失败

浙公网安备 33010602011771号

浙公网安备 33010602011771号