【3段式状态机】— 可乐贩卖机

一、设计文件

// ---------------------------------------------------------- // 饮料单价 2 元,该售卖机只能接受 0.5 元、1 元的硬币,考虑找零和出货 // 3段式 //------------------------------------------------------------ module fsm_3 ( input Clk, input Rst_n, //input pi_input_0, input pi_input_5, input pi_input_10, output reg po_out_money, output reg po_out_water ); parameter IDLE = 3'd0; parameter HALF_1 = 3'd1; parameter ONE = 3'd2; parameter HALF_3 = 3'd3; reg [3:0] state ; reg [3:0] next_state ; always@(posedge Clk or negedge Rst_n)begin if(Rst_n == 1'b0) state <= IDLE; else state <= next_state; end always@(*)begin case(state) IDLE: case({pi_input_5, pi_input_10}) 2'b10: next_state<= HALF_1; 2'b01: next_state<= ONE; default: next_state<= IDLE; endcase HALF_1: case({pi_input_5, pi_input_10}) 2'b10: next_state<= ONE; 2'b01: next_state<= HALF_3; default: next_state<= HALF_1; endcase ONE: case({pi_input_5, pi_input_10}) 2'b10: next_state<= HALF_1; 2'b01: next_state<= IDLE; default: next_state<= ONE; endcase HALF_3: case({pi_input_5, pi_input_10}) 2'b10: next_state<= IDLE; 2'b01: next_state<= IDLE; default: next_state<= HALF_3; endcase endcase end always@(posedge Clk or negedge Rst_n)begin if(Rst_n == 1'b0) po_out_water <= 1'b0; else if(((state == HALF_3) && (pi_input_5 == 1'b1)) || ((state == ONE) && (pi_input_10 == 1'b1))) po_out_water <= 1'b1; else if((state == HALF_3) && (pi_input_10 == 1'b1)) begin po_out_water <= 1'b1; po_out_money <= pi_input_5; end else begin po_out_water <= 1'b0; po_out_money <= 1'b0; end end endmodule

二、测试文件

`timescale 1ns/1ns module tb_fsm_3; reg clk; reg Rst_n; //reg in_0; reg in_1; reg in_2; reg[1:0] in[2:0]; wire out_money; wire out_water; initial begin in[0]=0; in[1]=1; in[2]=2; clk = 1'b0; Rst_n = 1'b0; #10; Rst_n = 1'b1; in_1 = 1'b0; in_2 = 1'b0; end always #10 clk = ~ clk; always@(posedge clk or negedge Rst_n)begin if(Rst_n == 1'b0)begin in_1 <= 1'b0; in_2 <= 1'b0; end else begin {in_1,in_2}<=in[{$random}%3]; end end fsm_3 fsm_3_inst ( .Clk(clk), .Rst_n(Rst_n), //.pi_input_0(in_0), .pi_input_5(in_1), .pi_input_10(in_2), .po_out_money(out_money), .po_out_water(out_water) ); endmodule

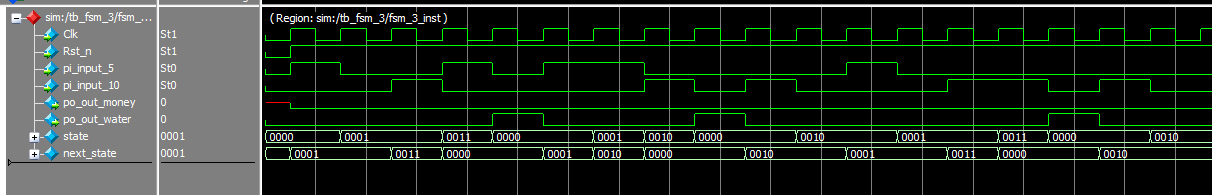

三、波形图

四、RTL图

浙公网安备 33010602011771号

浙公网安备 33010602011771号