【时序逻辑】— 3位模8同步加法器

一、设计文件

//====================================================================== // --- 名称 : 3位计数器 // --- 作者 : liuxiaoyan_fpga // --- 日期 : 2022-03-29 // --- 描述 : 设计一个3bit模8的加法器 // --- 用途 : 需要3个D触发器 //====================================================================== module add3 ( input Clk, input Rst_n, output reg Q0, output reg Q1, output reg Q2 ); always@(posedge Clk or negedge Rst_n)begin if(Rst_n == 1'b0)begin Q0 <= 1'b0; Q1 <= 1'b0; Q2 <= 1'b0; end else begin Q0 <= ~ Q0; Q1 <= Q0^Q1; Q2 <= (Q0 & Q1)^ Q2; end end endmodule 二、测试文件 `timescale 1ns/1ns module add3_tb; reg Clk; reg Rst_n; wire Q0; wire Q1; wire Q2; initial begin Clk = 1'b0; Rst_n = 1'b0; # 10; Rst_n = 1'b1; end always #10 Clk = ~ Clk; add3 a1 ( . Clk(Clk), . Rst_n(Rst_n), . Q0(Q0), . Q1(Q1), . Q2(Q2) ); endmodule

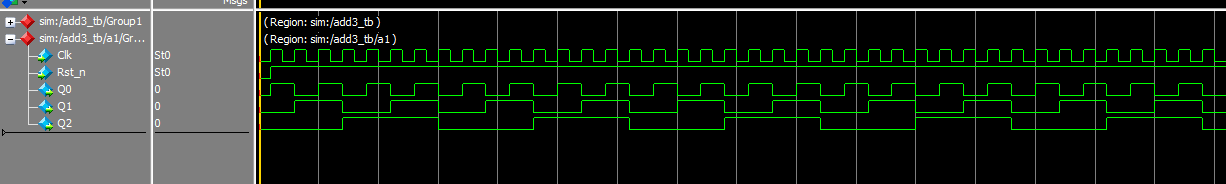

三、波形图

Q0低位、Q2高位

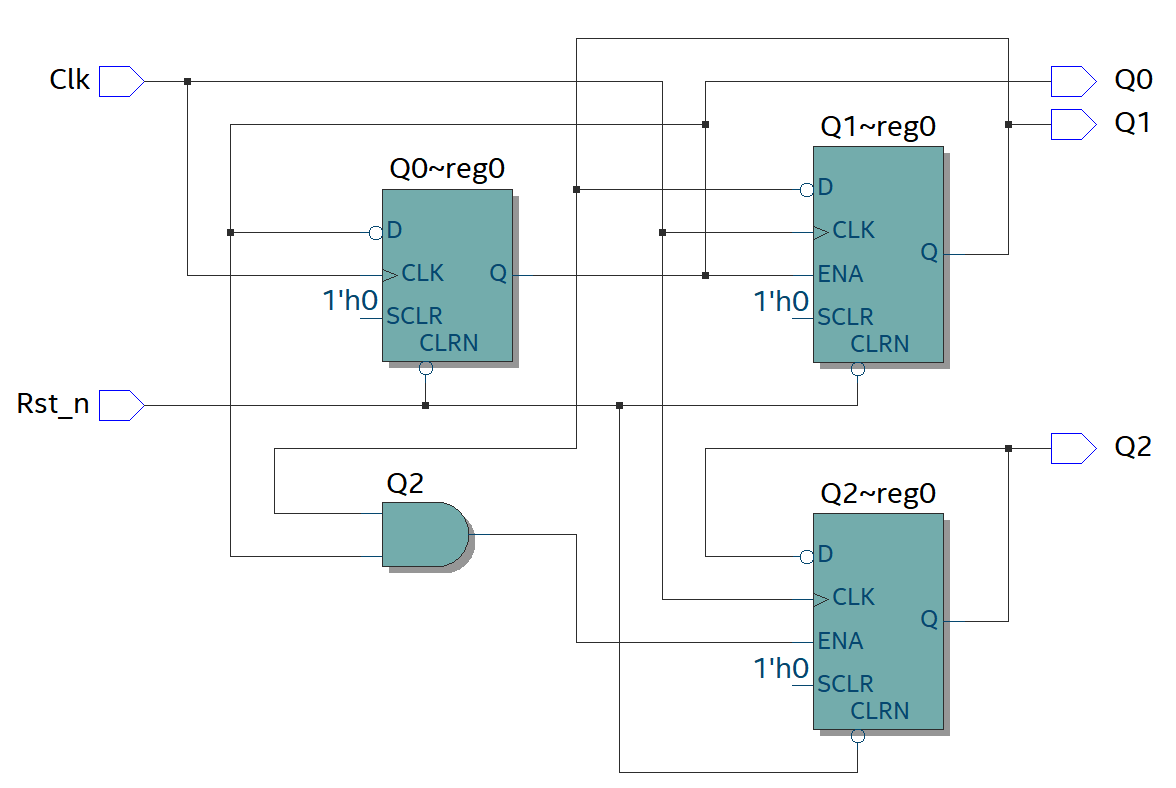

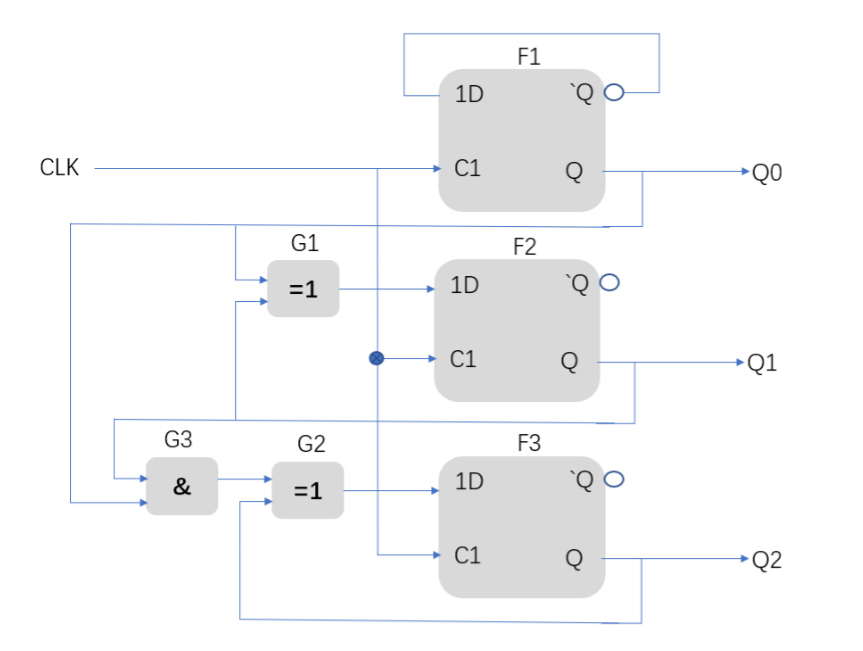

四、RTL图

浙公网安备 33010602011771号

浙公网安备 33010602011771号