UVM HDL access routines

或许有些用处的HDL access routines

1.rtl heir

module B; reg [3:0] cfg; endmodule module A; B b; endmodule // Testbench module module tb; A a(); initial run_test("base_test"); endmodule

2.uvm_hdl_check_path:

rtl层次check,用于对于直接访问dut层次的代码进行判断,某些情况下,并不想由于层次不对而编译不通过

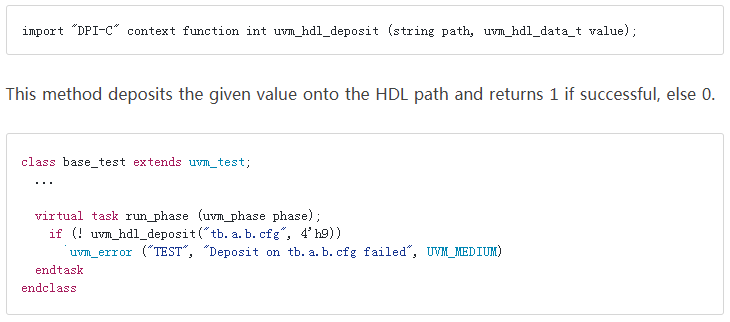

3.uvm_hdl_deposit:

可以在仿真过程中的某些时刻改变rtl中的值,在run_pahse中直接注错并处理,似乎也不错。

4.uvm_hdl_force

同hdl_deposit,但是force的值需要手动relased才可以,而deposit不需要release。

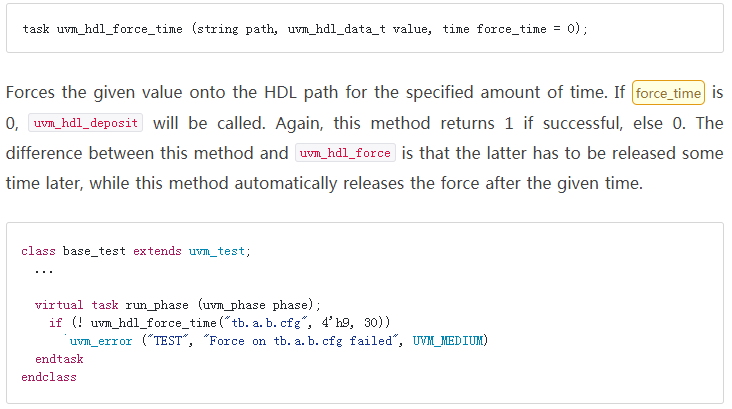

5.uvm_hdl_force_time

指定时间后自动released

6.uvm_hdl_release_and_read

force后released,并读取数据check

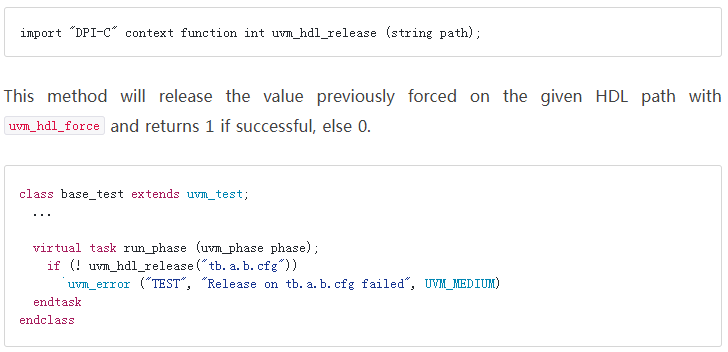

7.uvm_hdl_release

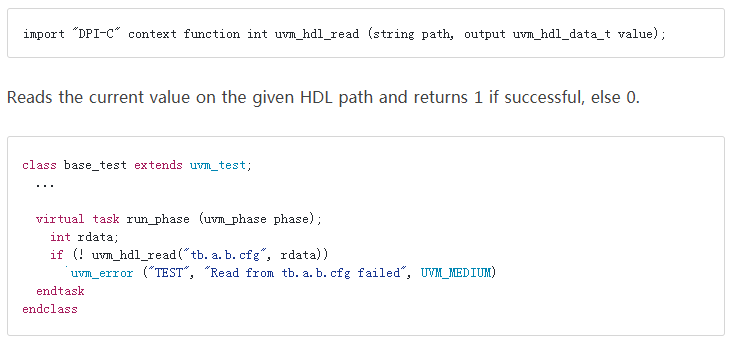

8.uvm_hdl_read

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/11109707.html

posted on 2019-06-30 14:47 hematologist 阅读(1378) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号