013 PHY(Physical Layer,PHY)

一、PHY

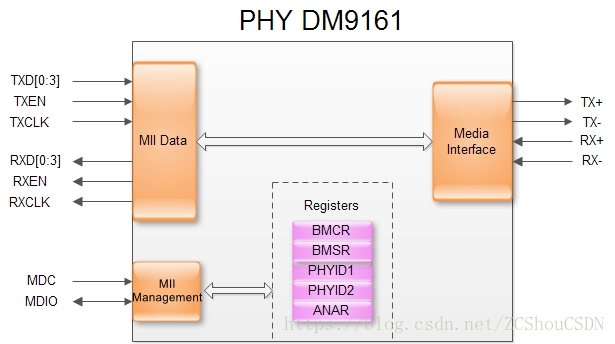

PHY((Physical Layer,PHY))是IEEE802.3中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC或CPU)通过SMI(Serial Manage Interface)对PHY的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。一个PHY的基本结构如下图:

PHY是物理接口收发器,它实现OSI模型的物理层。IEEE-802.3标准定义了以太网PHY。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。

PHY寄存器在IEEE802.3标准的 22.2.4 Management functions 节有介绍,但不涉及所有的寄存器,个别寄存器需要到其它章节中看,当然,文档里面也提到该在哪里找到哪个寄存器。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据)然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去,收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能,它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

二、PHY芯片

从硬件上来说,一般PHY芯片为模数混合电路,负责接收电、光这类模拟信号,经过解调和A/D转换后通过MII接口将信号交给MAC芯片进行处理。一般MAC芯片为纯数字电路。

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。

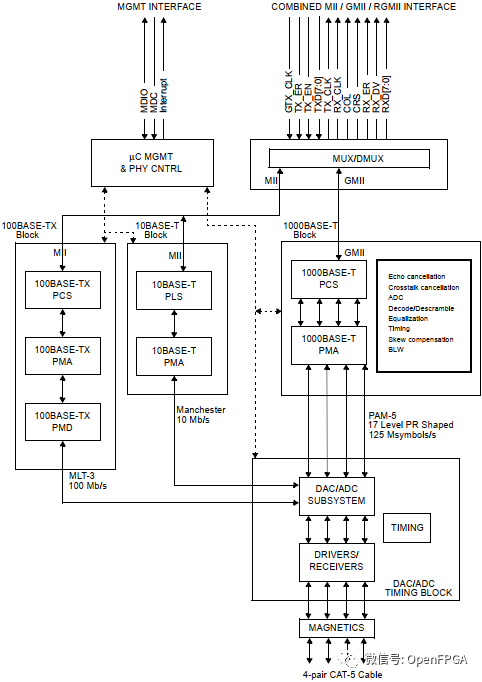

下图为RTL8211的原理框图,详细的数据手册链接如下:

http://download3.dvd-driver.cz/realtek/datasheets/pdf/rtl8211e(g)-vb(vl)-cg_datasheet_1.6.pdf

图8‑7 RTL8211原理框图

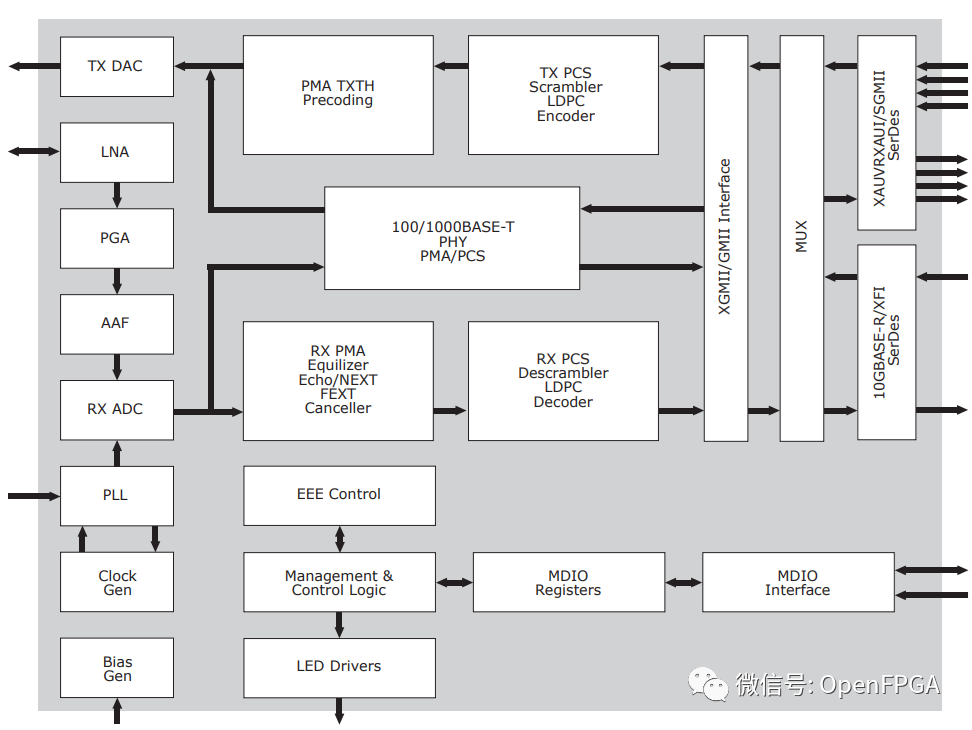

下图是Ti的DP83865原理框图,详细的数据手册链接如下:

http://www.ti.com/product/DP83865/technicaldocuments

图8‑8 DP83865原理框图

下图为88X3140/3120的原理框图,详细的数据手册链接如下:

https://www.marvell.com/products/transceivers/alaska-x-gbe.html

图8‑9 88X3140/3120原理框图

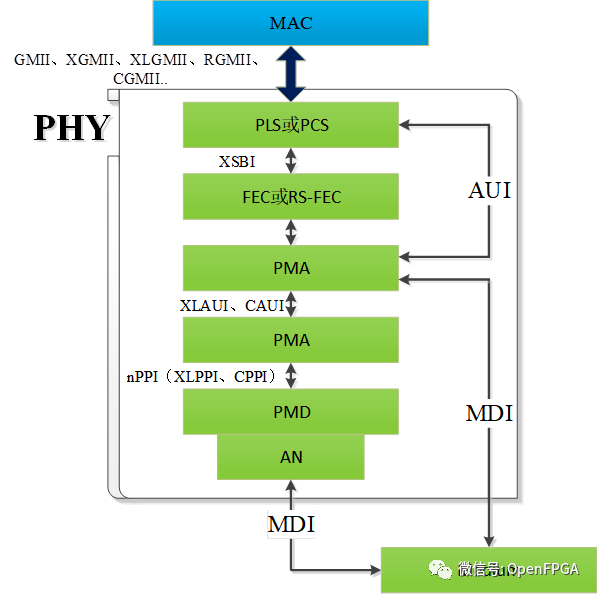

通过几个PHY片的原理框图可以总结出下面的简化PHY片的原理框图。

图8‑10 PHY简化的原理框图

从上图可知,PHY它包含了多个功能模块,功能模块的多少会因需要的不同而有所增减,比如:

只有10GBase-R、40GBase-R、100GBase-R的PCS需要FEC;

40GBase-R的PCS需要2个PMA、100GBase-R的PCS需要3个PMA;

只有≥1Gbps以上的背板应用场景才会用到AN。

接下来详细介绍上图中各个功能模块:

表8‑3各个功能模块的作用

|

名称 |

作用 |

|

|

PLS |

Physical Sublayer Signaling |

对MAC给的信息进行传递,只在1Mb/s、10Mb/s的应用场景才出现; |

|

PCS |

Physical Coding Sublayer |

对MAC给的信息进行编码,应用于≥100 Mb/s的应用场景,比如完成8B/10B、64B/66B、256B/257B编码; |

|

FEC |

Forward Error Correction |

前向纠错,与10GBase-R、40GBase-R的PCS 搭配; |

|

RS-FEC |

Reed-Solomon Forward Error Correction |

Reed-Solomon前向纠错,比单纯的FEC纠错能力更强,与100GBase-R的PCS 搭配,采用256B/257B编码; |

|

PMA |

Physical Medium Attachment |

物理介质连接子层。执行并串/串并转换 |

|

PMD |

Physical Medium Dependent |

物理介质相关子层。信号转换到特定介质上或反向转换 |

|

AN |

Auto-Negotiation Function |

自动协商,使背板两侧的Device能够互换信息以发挥出彼此最大的优势; |

图中还有连接各个模块间的接口比较特殊,这里面在单独列出来,如下表所示:

表8‑4各个模块间的接口

|

名称 |

备注 |

|

|

PLS与PMA间的接口 |

AUI |

Attachment Unit Interface |

|

PCS与FEC间的接口 |

XSBI |

10-Gigabit Sixteen Bit Interface |

|

PMA与PMA间的接口-可以是chip to chip,也可以是chip to module |

XLAUI |

40 Gigabit Attachment Unit Interface,4条lane,每条lane的数率是10.3125Gbps; |

|

CAUI |

100 Gigabit Attachment Unit Interface,10条lane,每条lane的数率是10.31250Gbps; |

|

|

PMA与PMD间的接口 |

nPPI1 |

Parallel Physcial Interface |

1:nPPI特定出现在PMD所接的媒介是光纤的情况下,比如40GBase-SR4、100GBase-SR10、40GBase-LR4协议。也就是说这种情况下的PMD是光模块,nPPI就必然是一种chip to module间的接口,这也是IEEE802.3标准与OIF_CEI标准兼容的地方之一。

三、PHY寄存器

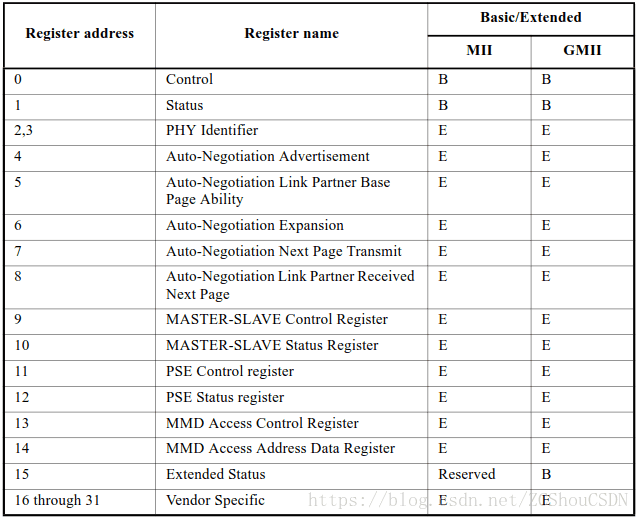

PHY寄存器的地址空间为5位,从0到31最多可以定义32个寄存器(随着芯片功能不断增加,很多PHY芯片采用分页技术来扩展地址空间以定义更多的寄存器),IEEE802.3定义了地址为0-15这16个寄存器的功能,地址16-31的寄存器留给芯片制造商自由定义,如下表所示。

(1)官方介绍请参考IEEE802.3标准的 22.2.4 Management functions 节。

(2)上图的B和E表示了,在特定接口下,寄存器是基本的还是扩展的。例如:MII接口下只有0和1寄存器是基本的,其它的是扩展的。注意:所为扩展是指留给IEEE以后的扩展特性用,不是给PHY厂商的扩展,PHY厂商自定义的只能是16~31号寄存器

(3)在IEEE标准文档及某些PHY手册中,某寄存器的比特(bit)用X.y表示,如0.15表示第0寄存器的第15位。

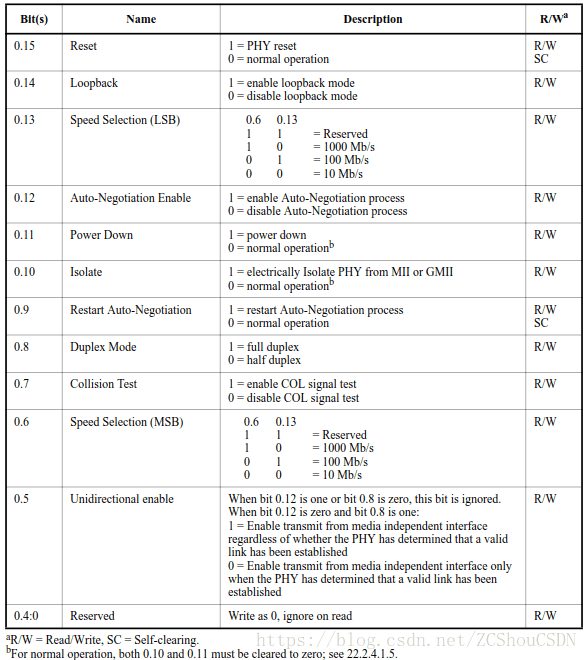

1、Control Register (Register 0)

寄存器0是PHY控制寄存器,通过Control Register可以对PHY的主要工作状态进行设置。应该保证控制寄存器每个位的默认值,以便在没有管理干预的情况下,上电或复位时PHY的初始状态为正常操作状态。Control Register的每一位完成的功能见下。

Reset: 通过将位0.15设置为逻辑1来完成复位PHY。 该操作应将状态和控制寄存器设置为其默认状态。 因此,此操作可能会改变PHY的内部状态以及与PHY关联的物理链路的状态。复位过程中Bit15保持为1,复位完成之后该位应该自动清零。 在复位过程完成之前,PHY不需要接受对控制寄存器的写入操作,并且在复位过程完成之前写入0.15以外的控制寄存器位可能不起作用。 复位过程应在0.15位设置的0.5 s内完成。

(1)一般要改变端口的工作模式(如速率、双工、流控或协商信息等)时,在设置完相应位置的寄存器之后,需要通过Reset位复位PHY来使配置生效。

(2)该比特位的默认值为 0。

Loopback: 当位0.14被设置为逻辑1时,PHY应置于环回操作模式。 当位0.14置位时,PHY接收电路应与网络介质隔离,并且MII或GMII处的TX_EN断言不应导致网络介质上的数据传输。 当位0.14置位时,PHY应接受来自MII或GMII发送数据路径的数据,并将其返回给MII或GMII接收数据路径,以响应TX_EN的断言。 当位0.14置位时,从断言TX_EN到断言RX_DV的延迟应小于512 BT。 当位0.14置位时,除非设置了位0.7,否则COL信号应始终保持无效,在这种情况下,COL信号的行为应如22.2.4.1.9所述。 清0.14位为零允许正常操作。

Loopback是一个调试以及故障诊断中常用的功能,Bit14置1之后,PHY和外部MDI的连接在逻辑上将被断开,从MAC经过MII/GMII(也可能是其他的MAC/PHY接口)发送过来的数据将不会被发送到MDI上,而是在PHY内部(一般在PCS)回环到本端口的MII/GMII接收通道上,通过Loopback功能可以检查MII/GMII以及PHY接口部分是否工作正常,对于端口不通的情况可用于故障定位。

(1)需要注意的是,很多时候PHY设置Loopback后端口可能就Link down了,MAC无法向该端口发帧,这时就需要通过设置端口Force Link up才能使用Loopback功能。

(2)该比特位的默认值为 0。

Speed Selection: ***Bit13和Bit6两位联合实现***对端口的速率控制功能。链接速度可以通过自动协商过程或手动速度选择来选择。 通过将位0.12清零来禁用自动协商时,允许手动速度选择。

当禁用自动协商并将位0.6清除为逻辑0时,将位0.13设置为逻辑1将PHY配置为100 Mb / s操作,并将位0.13清除为逻辑0将PHY配置为10 Mb / s操作 。

当禁用自动协商并将位0.6设置为逻辑1时,将位0.13清零为逻辑0会选择1000 Mb / s的操作。 将位0.6和0.13设置为逻辑1的组合保留用于未来的标准化。

当使能自动协商时,可以读取或写入位0.6和0.13,但位0.6和位0.13的状态对链路配置没有影响,位0.6和位0.13不需要反映当它被读取时链接。

如果PHY通过比特1.15:9和比特15.15:12报告它不能工作在所有速度时,则比特0.6和0.13的值应该与PHY可以操作的速度相对应。并且任何试图将该位设置为无效的操作均将被忽略。

(1)对Speed Selection的修改设置,往往需要复位端口才能配置生效。因此在设置该位置的时候需要检查自动协商的设置并通过Bit15复位端口。

(2)位0.6和0.13的默认值是根据位1.15:9和15.15:12所指示的PHY可以操作的***最高数据速率***的编码组合。

Auto-Negotiation Enable: 自动协商过程应通过将位0.12设置为逻辑1来启用。 如果位0.12设置为逻辑1,则位0.13、0.8和0.6不应对链路配置和除了自动协商协议规定之外的站操作产生影响。 如果将位0.12清零为逻辑0,则无论链路配置和自动协商过程的先前状态如何,位0.13、0.8和0.6都将确定链路配置。

如果PHY通过位1.3报告它缺乏执行自动协商的能力,则PHY应在位0.12返回零值。 如果PHY通过位1.3报告它缺乏执行自动协商的能力,则位0.12应该始终写为0,并且任何尝试将1写入位0.12都应该被忽略。

必须注意的是,对于1000BASE-T接口,自动协商必须打开。

Power Down: 通过将位0.11设置为逻辑1,可以将PHY置于低功耗状态。 清0.11位为零允许正常操作。 PHY在掉电状态下的具体行为是特定实现的。 处于掉电状态时,PHY应响应管理事务。 在转换到掉电状态期间和处于掉电状态期间,PHY不应在MII或GMII上产生寄生信号。

当位0.11或位0.10被设置为逻辑1时,PHY不需要满足RX_CLK和TX_CLK信号功能要求。 在位0.11和0.10清零后,PHY应在0.5 s内满足22.2.2中定义的RX_CLK和TX_CLK信号功能要求。

(1)Power Down模式一般在软件shut down端口的时候使用,需要注意的是端口从Power Down模式恢复,需要复位端口以保证端口可靠的连接。

(2)该位的默认值为 0。

Isolate: 通过将位0.10设置为逻辑1,PHY可能被迫将其数据路径与MII或GMII电隔离。 清零位0.10允许正常操作。 当PHY与MII或GMII隔离时,它不会响应TXD数据包和TX_EN,TX_ER、GTX_CLK的输入。并且它的TX_CLK,RX_CLK,RX_DV,RX_ER,RXD数据包、COL和CRS输出均应为高阻态。 当PHY与MII或GMII隔离时,它将响应管理事务(MDC/MDIO接口的信号)。

(1)IEEE802.3没有对Isolate 时MDI接口的状态进行规范,此时MDI端可能还在正常运行。Isolate在实际应用中并没有用到。

(2)由于目前很多百兆的PHY芯片其MAC接口主流的都是SMII/S3MII,8个端口的接口是相互关联的,一个端口设置Isolate可能会影响其他端口的正常使用,因此在使用中注意不要随意更改bit10的状态。

Restart Auto-Negotiation: 如果PHY通过位1.3报告它缺乏执行自动协商的能力,或者如果自动协商被禁用,则PHY应在位0.9返回零值。 如果PHY通过位1.3报告它缺乏执行自动协商的能力,或者如果禁用了自动协商,则应将位0.9始终写为0,并且任何尝试将1写入位0.9应被忽略。

Bit9置1将重新启动端口的自动协商进程,当然前提是Auto-Negotiation Enable是使能的。

一般在修改端口的自动协商能力信息之后通过Bit9置1重新启动自动协商来使端口按照新的配置建立link。

Duplex Mode: 可以通过自动协商过程或手动双面选择来选择双工模式。 通过将位0.12清零来禁用自动协商时,允许手动双面选择。

当禁用自动协商时,将位0.8设置为逻辑1将PHY配置为全双工操作,并将位0.8清零以将逻辑0配置为用于半双工操作的PHY。

当启用自动协商时,可以读取或写入位0.8,但位0.8的状态对链路配置没有影响。

如果PHY通过位1.15:9和15.15:12报告它只能在一个双工模式下工作,则位0.8的值应该与PHY可以工作的模式相对应,并且任何尝试改变将该位0.8修改为无效指的操作应被忽略。

对Duplex Mode的修改配置也需要复位端口才能生效。

Collision Test: 冲突信号(COL)测试开关。在需要对COL信号进行测试时,可以通过Bit7置1,这时PHY将输出一个COL脉冲以供测试。实际测试操作中也可以将端口配置为半双工状态,通过发帧冲突来测试COL信号,因此该配置实用价值不大。

Unidirectional enable: 如果PHY通过比特1.7报告它不具备编码和传输来自媒体独立接口的数据的能力,而不管PHY是否确定已建立有效链路,则PHY应在比特0.5中返回零值,并且 任何尝试写一个到位0.5应该被忽略。

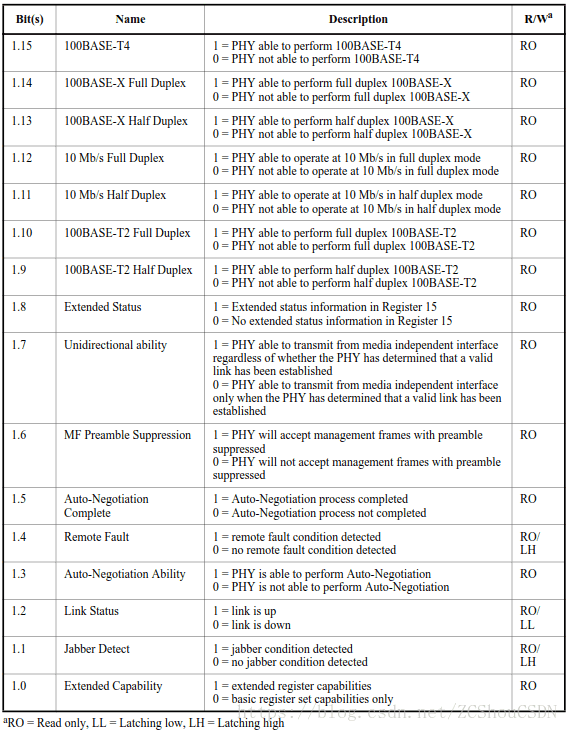

2、Status register

寄存器1是PHY状态寄存器,主要包含PHY的状态信息,大多数bit的值都是由芯片厂家确定的,每一个bit的功能在表3中已有详细说明。

寄存器中各位的详细说明如下:

100BASE-T4 ability: 当读为逻辑1时,位1.15指示PHY有能力使用100BASE-T4信令规范执行链路发送和接收。 当读为逻辑0时,位1.15表示PHY缺乏使用100BASE-T4信令规范执行链路发送和接收的能力。

100BASE-X full duplex ability: 当读为逻辑1时,位1.14指示PHY有能力使用100BASE-X信令规范执行全双工链路传输和接收。 当作为逻辑0读取时,bit1.14表示PHY缺乏使用100BASE-X信令规范执行全双工链路传输和接收的能力。

100BASE-X half duplex ability: 当读为逻辑1时,位1.13指示PHY有能力使用100BASE-X信令规范执行半双工链路传输和接收。 当读为逻辑0时,位1.13指示PHY缺乏使用100BASE-X信令规范执行半双工链路传输和接收的能力。

其他同类型的值意义基本与上面几个相同:指示PHY所具有的工作模式能力,不再一一说明。

Unidirectional ability: 当读为逻辑1时,位1.7指示PHY具有编码和传输来自媒体独立接口的数据的能力,而不管PHY是否确定已建立有效链路。 当读为逻辑0时,位1.7指示PHY只有在PHY确定已建立有效链路时才能从媒体独立接口传输数据。

MF preamble suppression ability: 当读为逻辑1时,位1.6指示PHY能够接受管理帧,而不管它们是否在22.2.4.5.2中描述的前导码模式之前。 当读为逻辑0时,位1.6指示PHY不能接受管理帧,除非它们之前是22.2.4.5.2中描述的前导码模式。

Auto-Negotiation Complete: 当读为逻辑1时,位1.5指示自动协商过程已完成,并且由自动协商协议(条款28或条款37)实施的扩展寄存器的内容是有效的。 当读为逻辑0时,位1.5指示自动协商过程尚未完成,并且扩展寄存器的内容由自动协商协议的当前状态定义,或者为手动配置写入。 如果自动协商通过清除位0.12禁用,则PHY应在位1.5返回零值。 如果PHY缺乏执行自动协商的能力,它还应在位1.5返回零值。

在调试以及异常故障处理时,可以通过该位寄存器的状态判断AN是否成功,从而进一步的检查AN相关的设置是否正确,或者芯片的AN功能是否正常等。

Remote Fault: 当读为逻辑1时,位1.4表示检测到远程故障状态。 故障类型以及故障检测的标准和方法是PHY特定的。 远程故障位必须使用锁存功能来实现,以便发生远程故障将导致远程故障位置位,并保持置位状态直至被清除。 每当通过管理接口读取寄存器1时,远程故障位应清零,并且还应通过PHY复位清零。

远端错误指示位。Bit4=1代表连接对端(Link Partner)出错,至于出错的具体类型以及错误检测机制在规范中并没有定义,由PHY的制造商自由发挥,一般的厂商都会在其他的寄存器(Register16-31由厂商自行定义)指示比较详细的错误类型。在与端口相关的故障查证中,Remote Fault是一个重要的指示信息,通过互联双方的Remote Fault信息(可能要加上其他的具体错误指示),可以帮助定位故障原因。

Auto-Negotiation ability: 当读为逻辑1时,位1.3指示PHY有能力执行自动协商。 当读为逻辑0时,位1.3指示PHY缺乏执行自动协商的能力。

Link Status: 当读为逻辑1时,位1.2指示PHY已经确定已建立有效链路。 当作为逻辑0读取时,位1.2指示该链接无效。 确定链路有效性的标准是PHY特定的。 链路状态位应该使用锁存功能来实现,以便发生链路故障情况将导致链路状态位清零并保持清零,直到通过管理接口读取。 此状态指示旨在支持在30.5.1.1.4,aMediaAvailable中定义的管理属性。

实际应用中一般都是通过Bit2来判断端口的状态。而且,一般的MAC芯片也是通过轮询PHY的这个寄存器值来判断端口的Link状态的(这个过程可能有不同的名称,比如BCM叫做Link Scan,而Marvell叫做PHY Polling。)如前所述,在AN Enable的情况下,Link Status的信息只有在Auto-Negotiation Complete指示已经完成的情况下才是正确可靠的,否则有可能出错。

Jabber Detect: 当作为逻辑1读取时,位1.1指示已经检测到爆音条件。 此状态指示旨在支持30.5.1.1.6中定义的管理属性,aJabber和30.5.1.3.1 nJabber中定义的MAU通知。 检测Jabber条件的标准是PHY特定的。 Jabber检测位应该使用锁存功能来实现,以便发生Jabber条件将导致Jabber检测位置位,并保持置位状态直至被清除。 每次通过管理接口读取寄存器1时,Jabber检测位应清零,并且还应通过PHY复位清零。

IEEE802.3对Jabber的解释是“A condition wherein a station transmits for a period of time longer than the maximum permissible packet length, usually due to a fault condition”。这一位指示的是Link Partner发送的时间超过了规定的最大长度。值得注意的是,Jabber Detect只有在10BASE-T模式下才有意义,100和1000M模式是没有定义Jabber这一功能的。

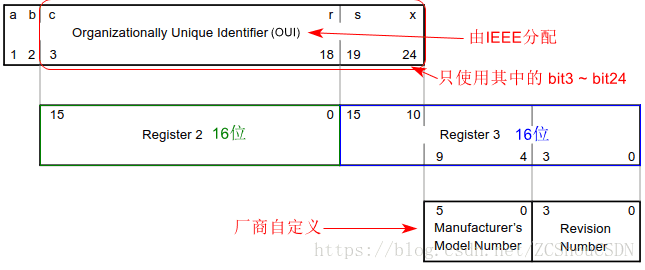

3、PHY Identifier Register

寄存器2和3存放PHY芯片的型号代码,寄存器2(PHY ID1)为高16位,而寄存器3(PHY ID2)为低16位。由芯片制造商自行定义,实际应用中软件通过读取这两个寄存器的内容可以识别PHY的型号和版本。

PHY标识符应由由IEEE分配给PHY制造商的组织唯一标识符(OUI)的(只需要使用第3至第24位,共22位),加上6位制造商的型号以及4位制造商的修订版编号组成。 PHY标识符旨在提供足够的信息来支持30.1.2中所要求的oResourceTypeID对象。

OUI的第三位分配给位2.15,OUI的第四位分配给位2.14,依此类推。 位2.0包含OUI的第十八位。 位3.15包含OUI的第十九位,位3.10包含OUI的第二十四位。 位3.9包含制造商型号的MSB。 位3.4包含制造商型号的LSB。 位3.3包含制造商版本号的MSB,位3.0包含制造商版本号的LSB。具体如下图所示:

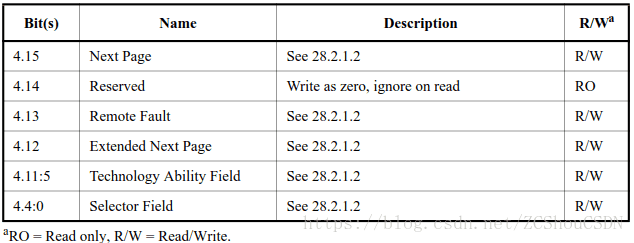

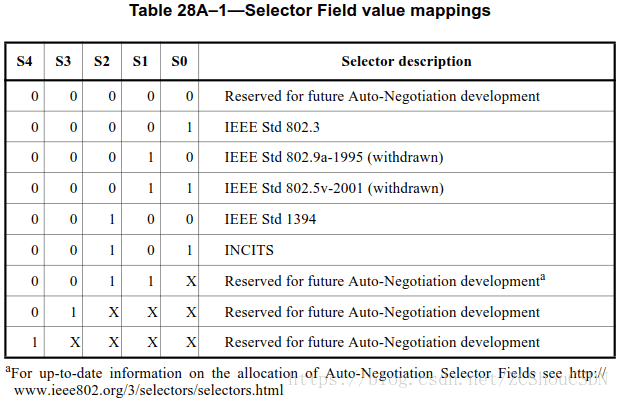

4、Auto-Negotiation Advertisement Register (Register 4) (R/W)

寄存器4是自动协商的能力通告寄存器,在AN Enable的前提下(见寄存器0),端口根据该寄存器的相关配置将自动协商信息通过FLP在MDI上进行通告。当AN配置为Disable状态的时候,寄存器4的配置将不起作用,端口的工作模式由控制寄存器中的配置决定。

该寄存器包含PHY的通告能力,它们将在自动协商期间传送给其链接伙伴。 基本页的位定义在IEEE标准的28.2.1.2中定义。 上电时,在自动协商开始之前,该寄存器应具有以下默认配置:

Selector Field (4.4:0): 被设置为适当的代码,如IEEE标准的附件28A中所规定。

Reserved(4.14): 被设置为逻辑0。

Technology Ability Field(4.11:5): 根据MII状态寄存器(寄存器1)(1.15:11)中设置的值或等效值设置。 另见28.2.1.2.3和附件28D。

4.1 Link codeword encoding(基本链路码字)

在FLP Burst内传输的基本链路代码字(基本页面)应该传达如图28-7所示的编码。 自动协商功能可以使用下一页功能支持其他页面。 下一页交换中使用的链接代码字的编码在28.2.3.4中定义。 在FLP Burst中,D0应该是第一个传输的位。

4.2 Next Page function

下一页功能使用标准的自动协商仲裁机制来允许交换任意的数据。 数据由可选的下一页信息携带,其遵循用于基本链接码字的传输和确认过程。 定义了四种类型的下一页编码:消息页面,未格式化页面,扩展消息页面和扩展的未格式化页面。

关于该部分,具体见IEEE标准的28.2.3.4 Next Page function。

在IEEE标准中,Auto-Negotiation Advertisement Register中的各部分全部是在独立章节中进行介绍的。具体如下:

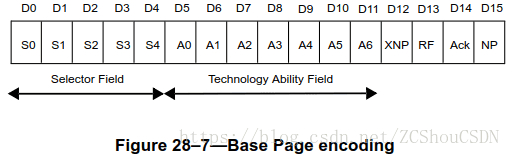

Selector Field: 选择器字段(S [4:0])是一个5位宽的字段,编码32个可能的消息。 链路码字中的选择器字段S [4:0]应用于识别自动协商发送的消息的类型。 下表列出了可能发送的消息的类型。 随着新消息的发展,该表格将相应更新。

未指定的组合保留供将来使用。 不会传输选择器字段的预留组合。***我们所接触的以太网PHY遵从IEEE802.3规范,Selector Field=0001,该区域不可随意更改(很多PHY将此区域设计为只读寄存器,以免被修改)***。

Technology Ability Field: 技术能力字段(A [6:0])是一个7位宽的字段,其中包含指示选择器字段值特定的支持技术的信息。 这些位被映射到各个技术,以便能够针对单个选择器字段值并行通告能力。 附录28B.2和附件28D描述了IEEE 802.3选择器的技术能力字段编码。 链接代码字中可能会公布多种技术。 设备应支持其宣传的技术的数据服务能力。

Extended Next Page: 扩展下一页(XNP)被编码在基本链路码字的位D12中。 扩展下一页位指示本地设备在设置为逻辑1时支持扩展下一页的传输,并指示本地设备在设置为逻辑0时不支持扩展下一页。 Extended Next Page的使用与协商的数据速率,媒体或链接技术是正交的。 扩展下一页位按照28.2.3.4中的扩展下一页功能规范使用。

Next Page: 无论选择器字段值还是链接码字编码,下一页(NP)都在D15位编码。 支持附加链接码字编码的传输和接收是可选的。 如果不支持Next Page功能,NP位应始终设置为逻辑0。 如果设备实现下一页功能并希望进行下一页交换,则应将NP位设置为逻辑1。 设备可以实现下一页功能,并通过将NP位设置为逻辑0来选择不参与下一页交换。 下一页功能在28.2.3.4中定义。

Remote Fault: 远程故障(RF)编码在基本链路码字的位D13中。 默认值是逻辑零。 远程故障位为传输简单的故障信息提供了一种标准的传输机制。 当自动协商通告寄存器(寄存器4)中的RF位设置为逻辑1时,发送的基本链路码字中的RF位被设置为逻辑1。 当接收到的基本链路代码字中的RF位被设置为逻辑1时,如果存在MII管理功能,则MII状态寄存器(寄存器1)中的远程故障位将被设置为逻辑1。

5、Auto-Negotiation Link Partner ability register (Register 5) (RO)

寄存器5保存的是本端PHY接收到的对端PHY所通告的端口能力,寄存器5的结构和寄存器4基本一致。

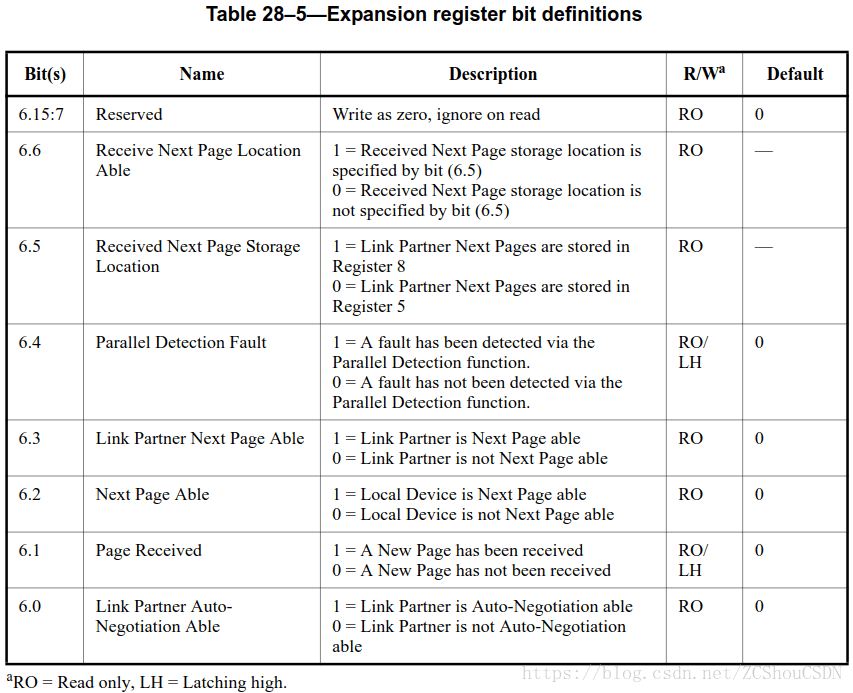

6、Auto-Negotiation Expansion Register (Register 6) (RO)

寄存器6保存了PHY自动协商过程的异常信息。从这个寄存其中我们可以获取到Link Partner子否支持自动协商以及自动协商下一页有没有收到的信息。

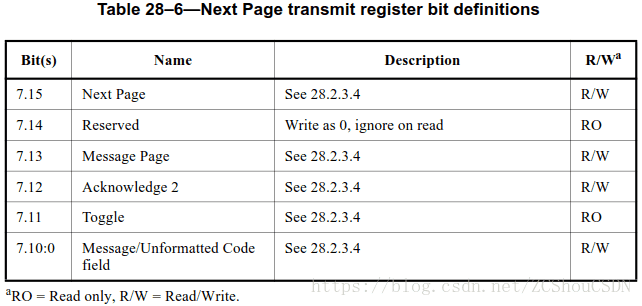

7、Auto-Negotiation Next Page transmit register (Register 7) (R/W)

自动协商下一页发送寄存器包含在支持下一页功能时要发送的下一页链接码字。 (见表28-6)内容在28.2.3.4中定义。 上电时,该寄存器应包含默认值2001H,该值表示消息代码设置为Null消息的消息页面。 该值可以由设备希望传输的任何有效的下一页消息代码替换。 写入该寄存器应将mr_next_page_loaded设置为true。

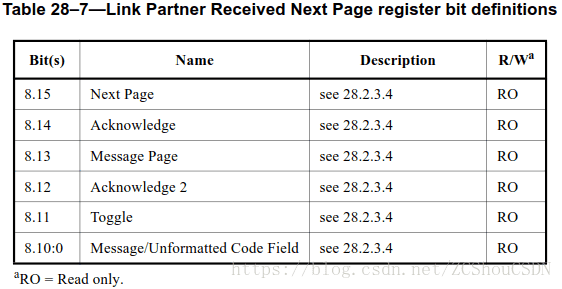

8、Auto-Negotiation Link Partner Received Next Page register (Register 8) (RO)

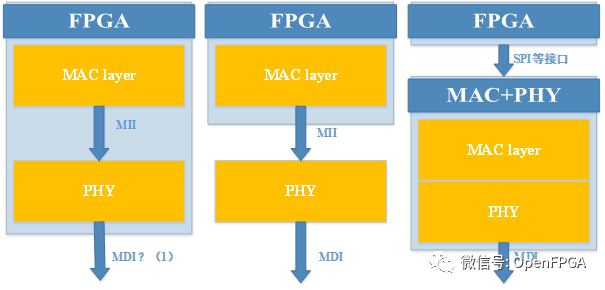

四、FPGA实现网口通信三种方式

从之前文章分析可知,FPGA实现网口通信主要有以下几种方式:

FPGA独立实现MAC与PHY协议;

FPGA独立实现MAC协议,PHY采用独立芯片;

FPGA既不实现MAC也不实现PHY,MAC与PHY均采用集成芯片;

相应的框图如下:

图8‑11 FPGA实现网口通信三种方式

五、参考资料

1、https://blog.csdn.net/zcshoucsdn/article/details/80090802#comments

2、https://blog.csdn.net/ChenGuiGan/article/details/108603550

3、https://mp.weixin.qq.com/s/rnikc3srIjHw3ZLFkrVNFQ

4、https://mp.weixin.qq.com/s/EJOdYYI8l7TCD2l1bdy3MA

浙公网安备 33010602011771号

浙公网安备 33010602011771号