verdi基本使用

verdi用起来

可以参考 https://blog.csdn.net/qq_42240380/article/details/122342639

使用verdi,需在testbench文件里输入

</details>

`ifdef FSDB // For Synopsys VCS

initial begin

$fsdbDumpfile("waveform.fsdb");

// Dump all signals from the top level module 'tb_top' and below

$fsdbDumpvars;

end

`elsif VCDPLUS // For Cadence Xcelium/Incisive

initial begin

$vcdplusfile("waveform.vpd");

// Dump all signals from the top level module 'tb_top' and below

$vcdpluson;

end

`endif

当我们的源文件准备好之后,可以 find -name "*.v" >verif.f其效果就是寻找当前文件夹下的.v文件,将其路径输出到verif.f文件内,这个文件名是随意的。

编写Makefile

# Makefile For Verdi

all: compile simulate

compile:

vcs \

-full64 \ #支持64位运行模式

-debug_acc+all \ #在完全模式下进行调试,可替换为-debug_access+all

-timescale=1ns/1ns \

-fsdb +define+FSDB \ #生成fsdb文件,并对所有.v源文件进行宏定义

-l com.log \ #生成com.log文件用于查看编译日志

-f verif.f #文件列表,将verif.f所列文件全部编译

simulate:

./simv -l sim.log #生成sim.log文件用于查看仿真日志

dve:

dve \

-vpd *.vpd & #启动Dve查看vpd类型的波形文件

verdi:

verdi \

-f verif.f \ #用Verdi加载verif.f所列全部源文件

-nologo \

-ssf *.fsdb & #启动Verdi查看fsdb类型的波形文件

clean:

@rm -rf csrc DVEfiles simv simv.daidir ucli.key VCS*

@rm -rf *.log *.vpd *.ddc *.svf *.SDF *Synth *Netlist*

@rm -rf alib-52 work

@rm -rf *.conf *.rc *.fsdb verdiLog

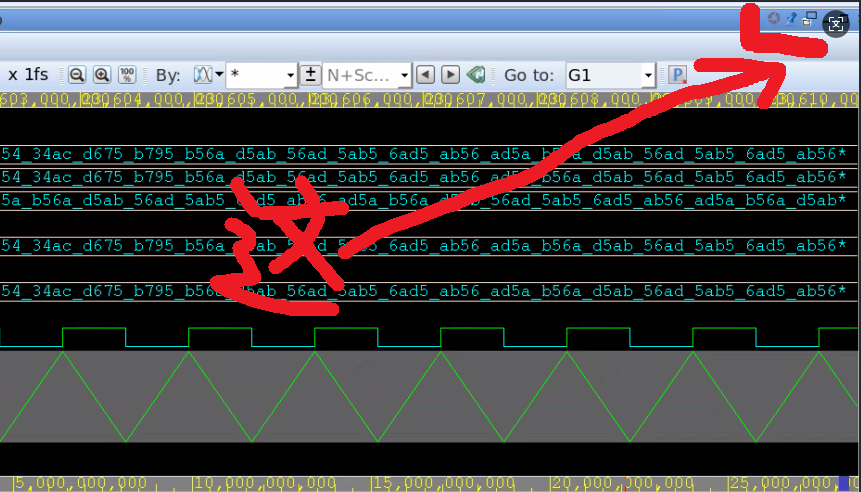

make compile进行编译,make simulate进行仿真,make verdi查看波形,选中源代码中的信号,按CTRL+W,即可在波形窗口看到波形。

veridi查看波形参考:https://blog.csdn.net/StephenX9760/article/details/128170988

使用经验积累

verdi波形窗口调整

不想显示的窗口,可以最小化。如果最小化后想调整回来,在右下脚的window manager可以看到。

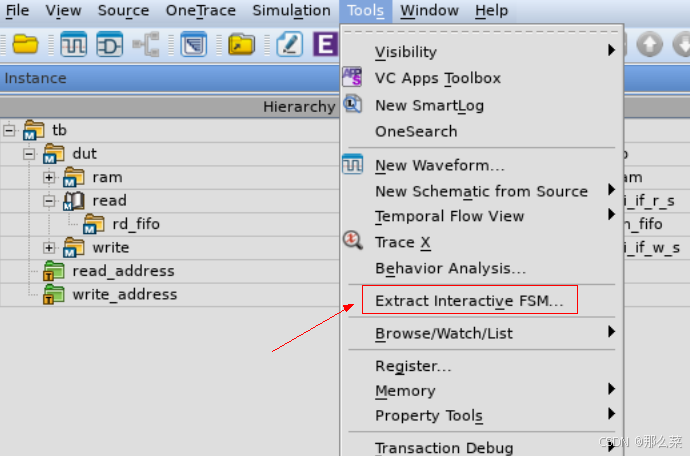

verdi查看状态机

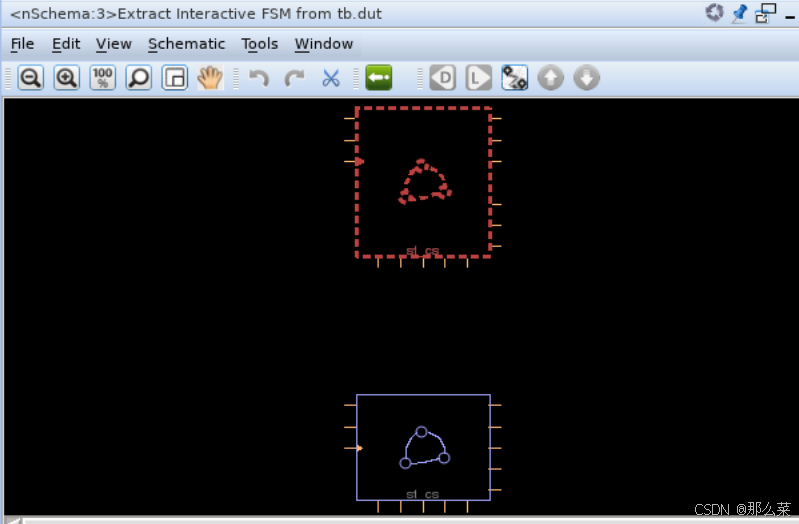

出现弹窗,默认all stages,然后出现状态机

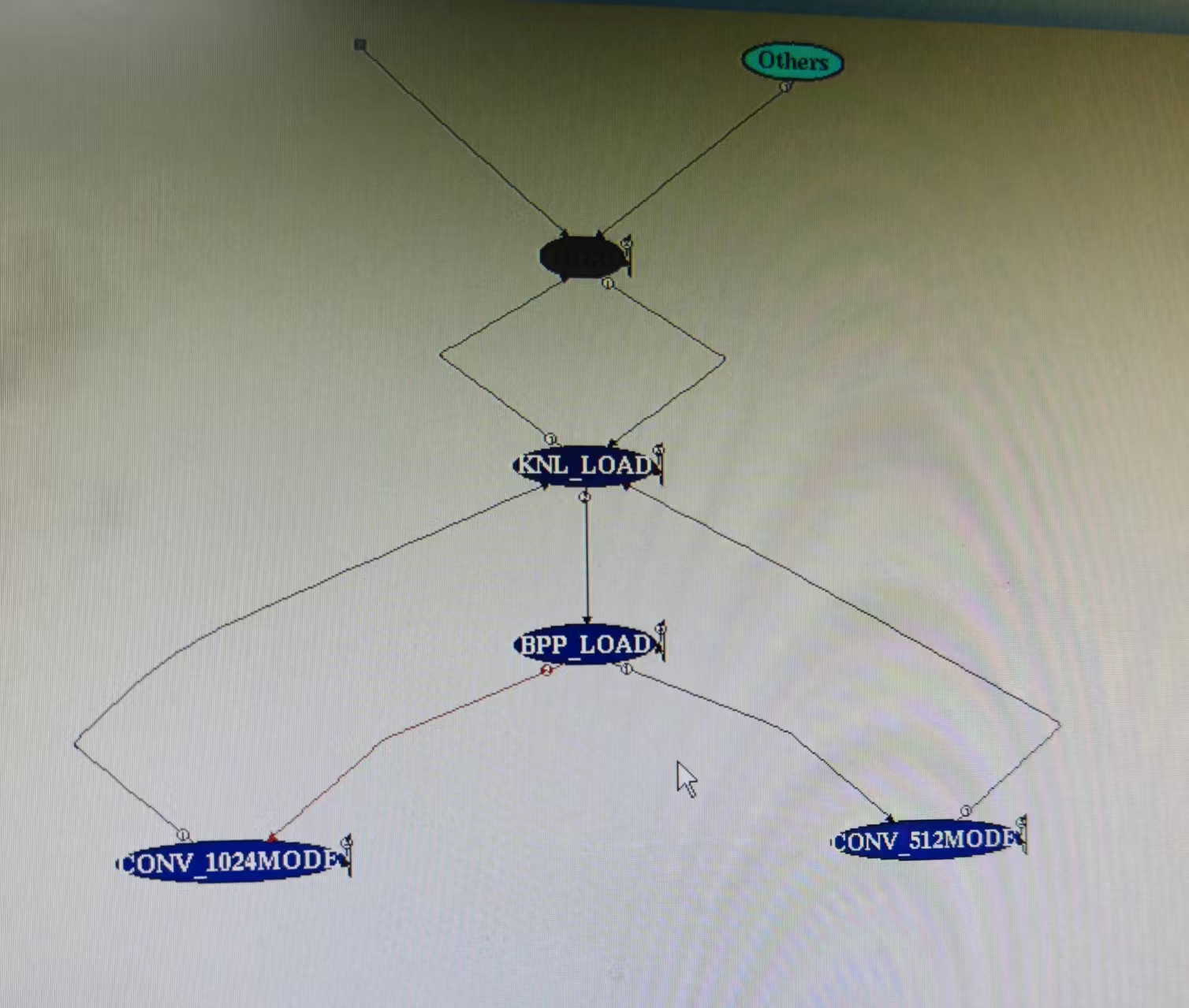

点击可以看到详情

放大后,可以看到状态机的转换条件(点击状态周围的序号)

如果想加载状态机的波形,可以鼠标点一下FSM界面空白处(这是说明我们在这个窗口操作),然后ctrl+w (右键,add signals to waveform)

浙公网安备 33010602011771号

浙公网安备 33010602011771号