常见器件的Verilog写法

最后修改日期:2023.04.12

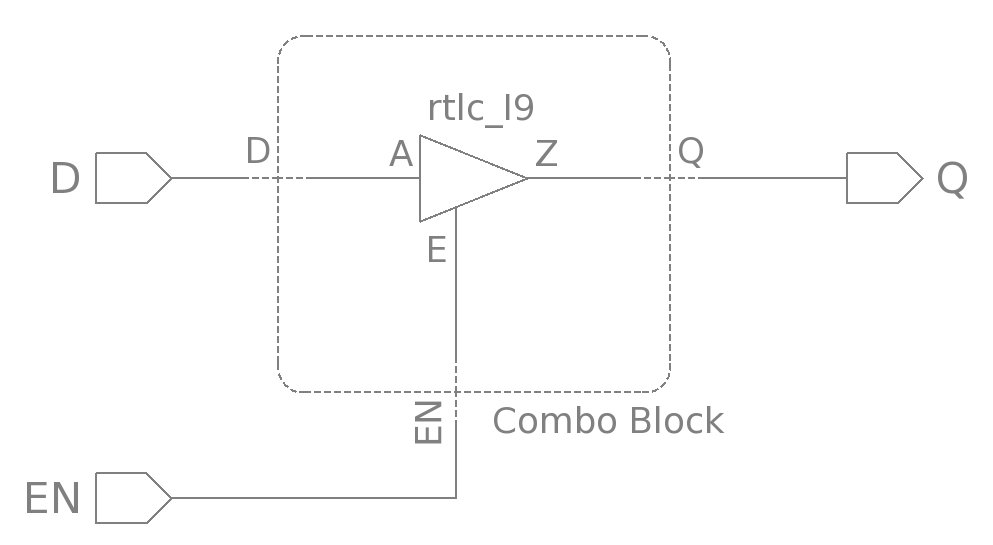

1. 三态门

1.1. 写法

wire q;

assign q = en ? d : 1'bz;

1.2. 解释

q必须是wire类型,否则就是类似于锁存器/寄存器的结构。

三态门常用在总线结构上。但是直接用三态门去写,综合的结果并不好。这可能是因为,三态门的高阻z有多高是不太确定的,所以综合器需要以最坏情况来考虑驱动,从而占用了更多的资源。

三态门还常用在双向接口上。

1.3. 综合结果

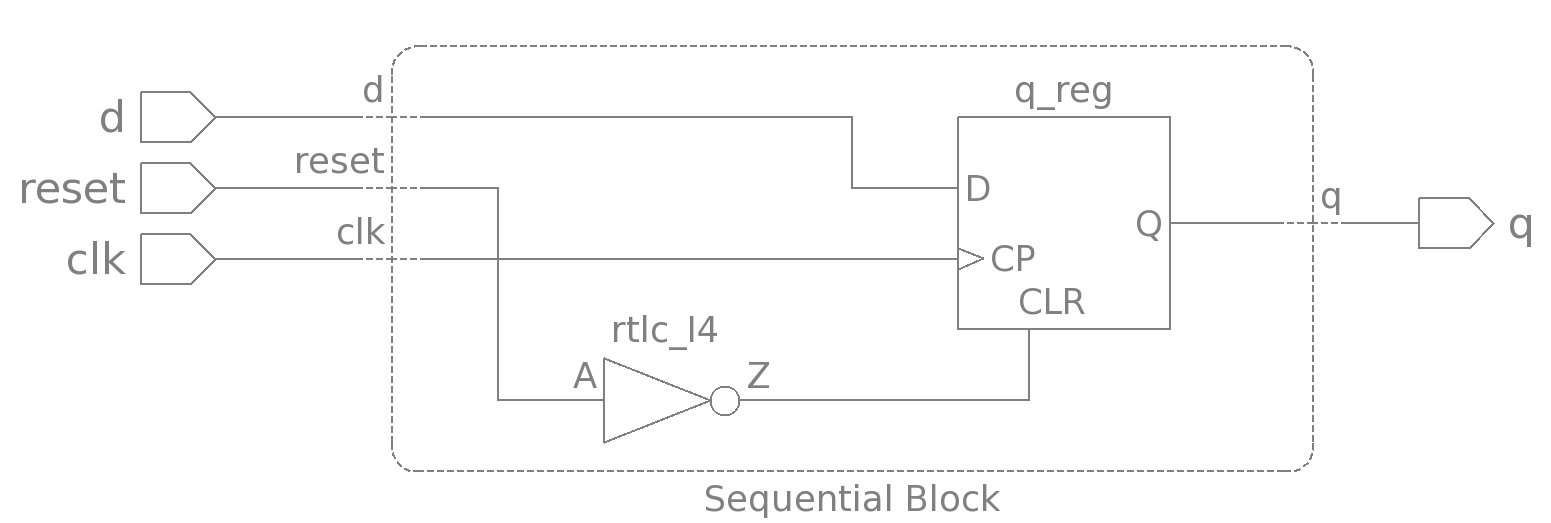

2. 带有低电平异步复位的D寄存器(register)

reg q;

always @ (posedge clk or negedge reset) begin

if(!reset)

q <= 0;

else

q <= d;

end

2.1. 解释

注意,虽然reset是低电平有效复位信号,但是其在敏感列表中依然写作negedge reset。虽然从电路功能来说,好像也没有太大区别,但是negedge确确实实是边沿敏感的描述方式。这也是很多人诟病Verilog的原因之一:它甚至连基本的寄存器描述都不严谨。

因为是异步复位,所以reset出现在分支语句的第一个分支。如果想要写同步复位,把reset从敏感列表中移除即可。

事实上,同步复位在实际的电路中极少运用,因为复位就是为了重置电路状态,它应该是最优先的命令,不应该受到时钟影响。不过,也许同步复位在某些FPGA中是更合适的写法?毕竟Xilinx是推荐对其FPGA使用同步复位逻辑的。

2.2. 综合结果

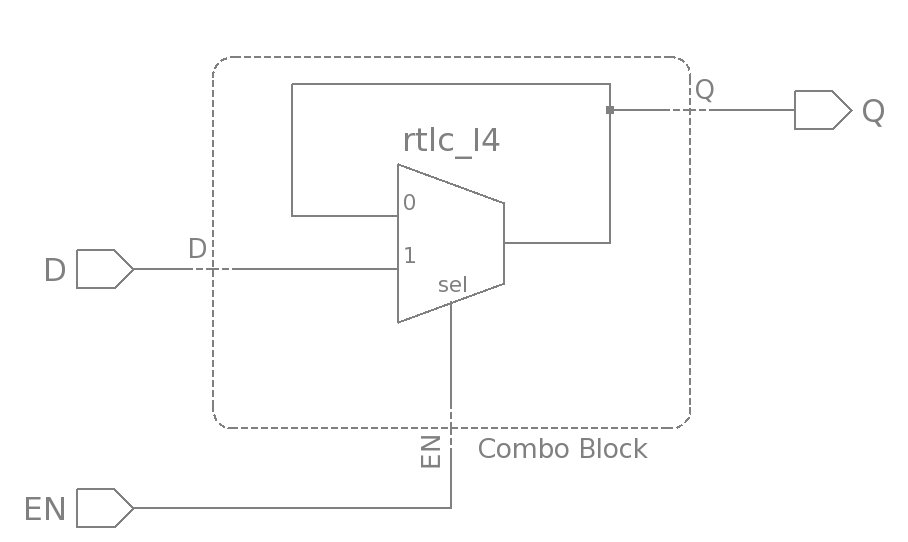

3. 没有复位的D锁存器(latch)

reg q;

always @ (*) begin

q = en ? d : q

end

3.1. 综合结果

如下图是无复位锁存器的综合结果,其本质是环接的2-1多路选择器。

3.2. 注意

3.2.1. FPGA中不要使用锁存器

在FPGA中,尽量避免使用锁存器,其本质上是组合逻辑电路。

在组合逻辑当中,将一个组合逻辑的输出不经过寄存器直接接到其输入,这个问题一般被称为组合逻辑环路(combinational loop)。这会带来许多的问题,比如时序、稳定性等问题。

尤其对于FPGA,其中的组合逻辑大都使用多级LUT实现。如果出现环路,那么延时将变得难以控制。

3.2.2. ASIC中有时可以使用锁存器

因为锁存器的面积比寄存器小得多,所以在有面积需求的情况下可以考虑使用锁存器。在使用的时候务必对锁存器的功能深思熟虑,确保锁存器不会带来功能上的问题。

尽管如此,锁存器在Verilog代码中还是时常会被报错,诸如latch inferred, combinational loop exists等。

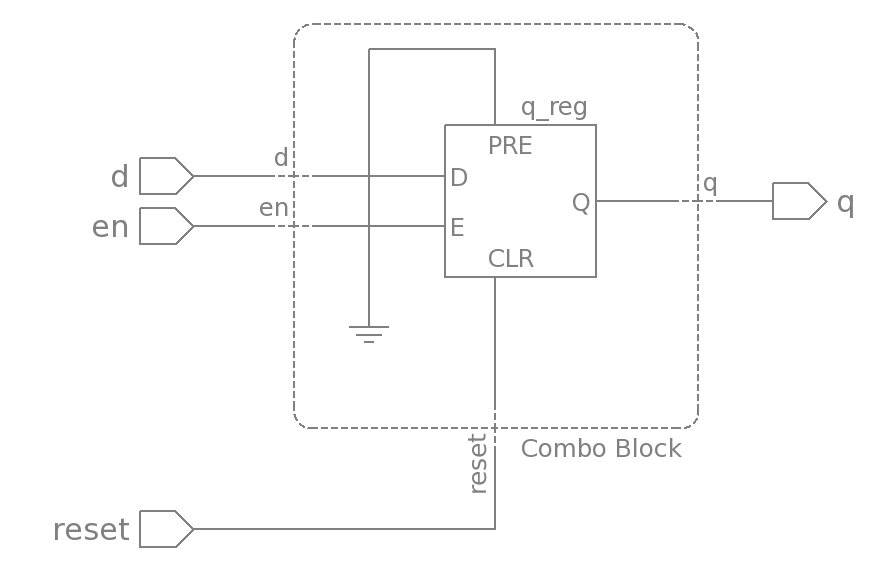

4. 带有低电平异步复位的D锁存器

reg q;

always @ (reset or en or d) begin //等待reset、 en或输入信号d的改变

if(reset) //若reset信号为高,把q置0

q = 0;

else if(en) //若en信号为高,锁存输入信号d

q = d;

end

4.1. 综合结果

标准的D锁存器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号