时序分析7讲 input delay 项目实操 8讲 中心 边沿对齐

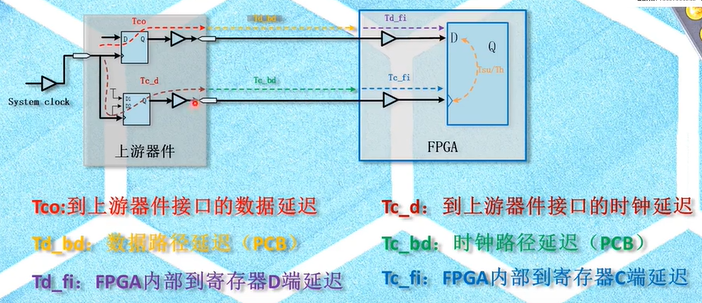

CMOS芯片和FPGA芯片,coms芯片给fpga发时钟和 (复数)数据。看手册 从CMOS发出的时钟和数据有什么相位关系?需要我们知道

还需知道 pcb之间 时钟的延时和数据延时的差又是多少

这样我们就能知道这个时刻时钟和数据的状态,就能做 input delay约束了

在时钟前面的数据 min input delay就变成负值

记住发射沿和数据最大最小延时之间的关系,就能进行input delay

1.看数据手册找到从芯片管脚输出时钟和数据的关系

2.讨论PCB的延时

input delay

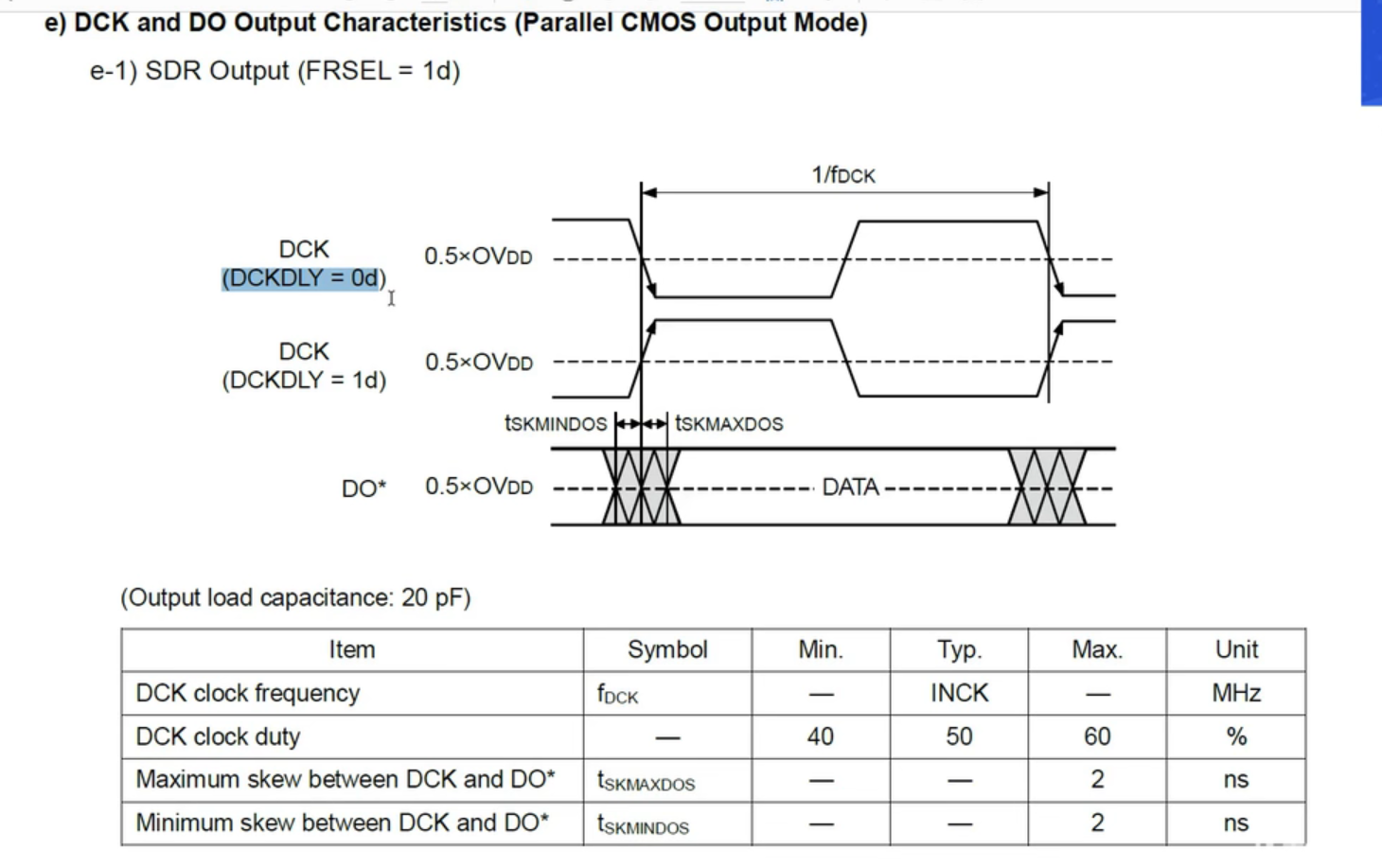

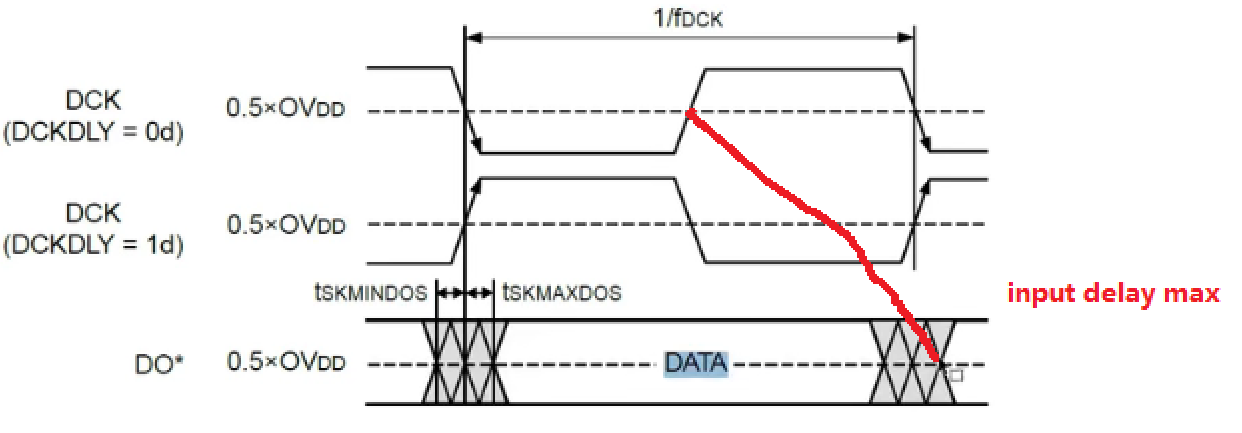

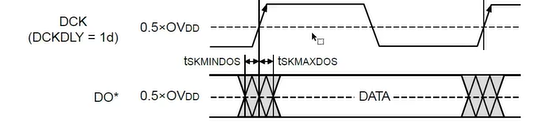

看哪种对齐方式 中心对齐 0d 还是边沿对齐 1d

假设板子上延时是相同的,布局布线设置

中心对齐模式 0d

min (1/F)/2-2ns

max (1/F)/2+2ns

开始

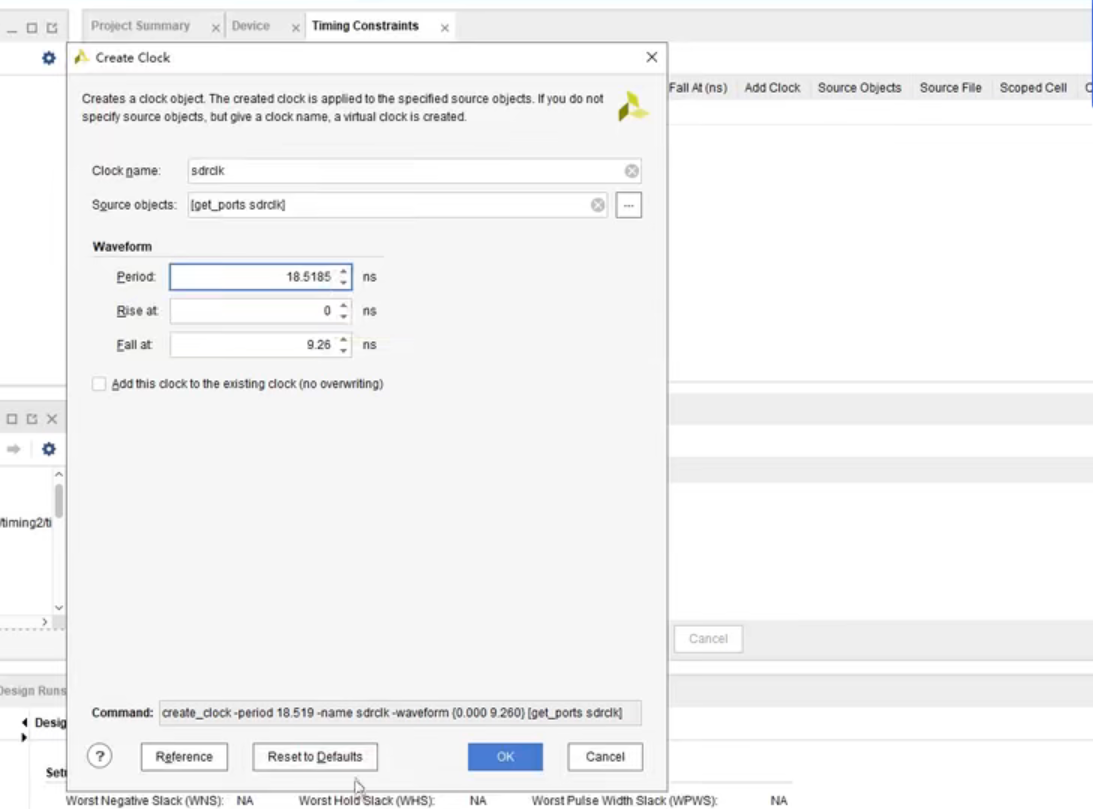

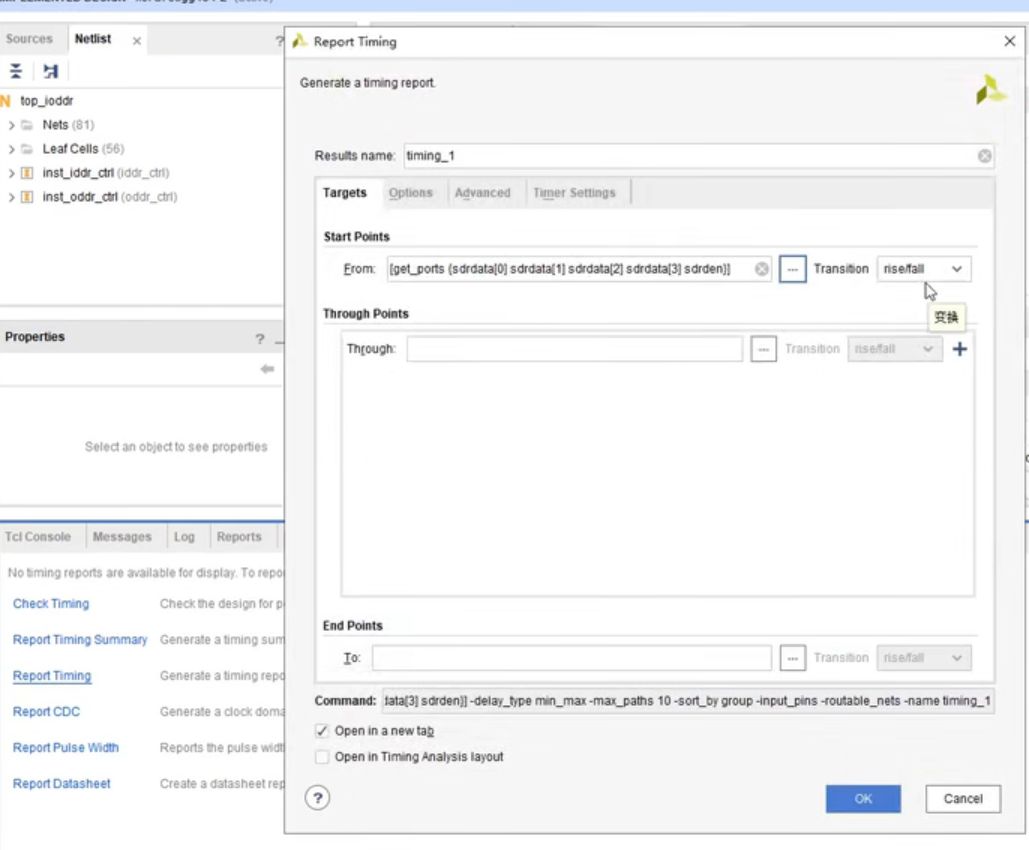

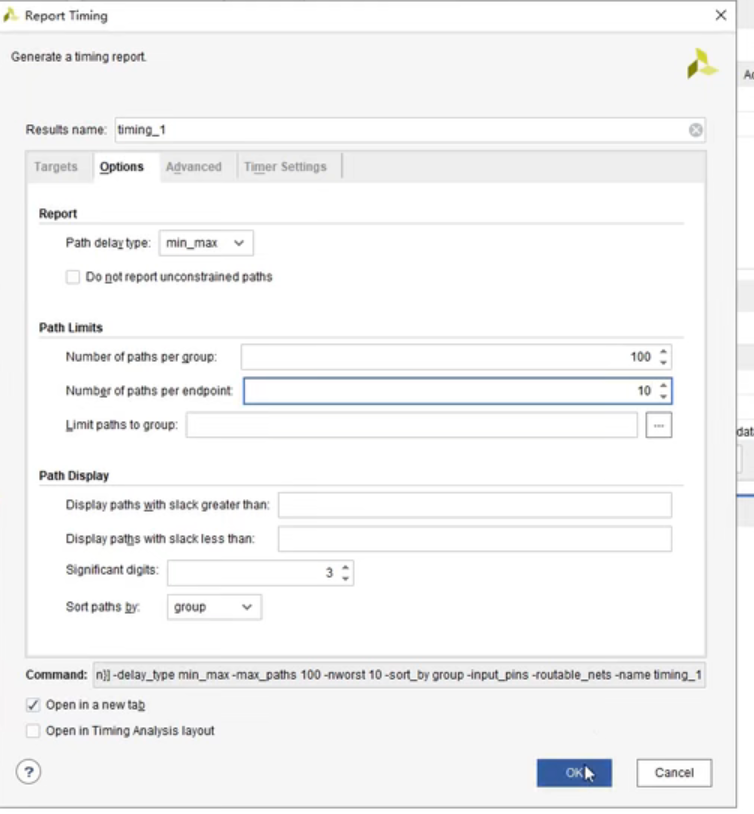

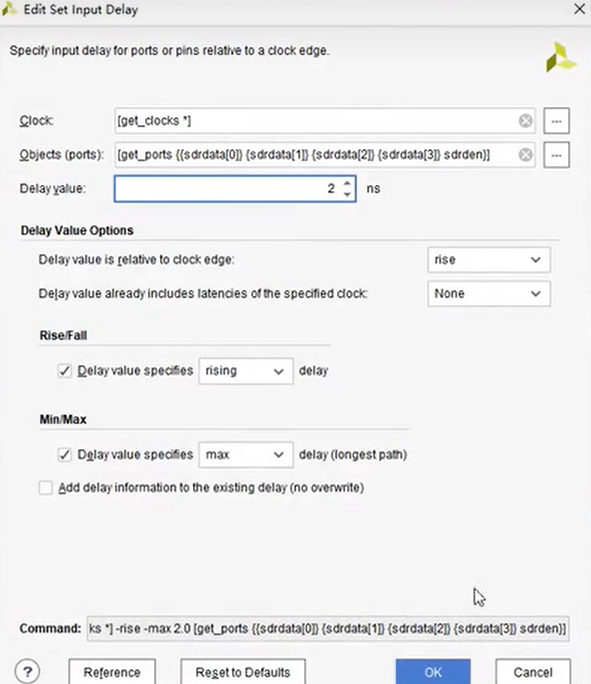

1.creat clock

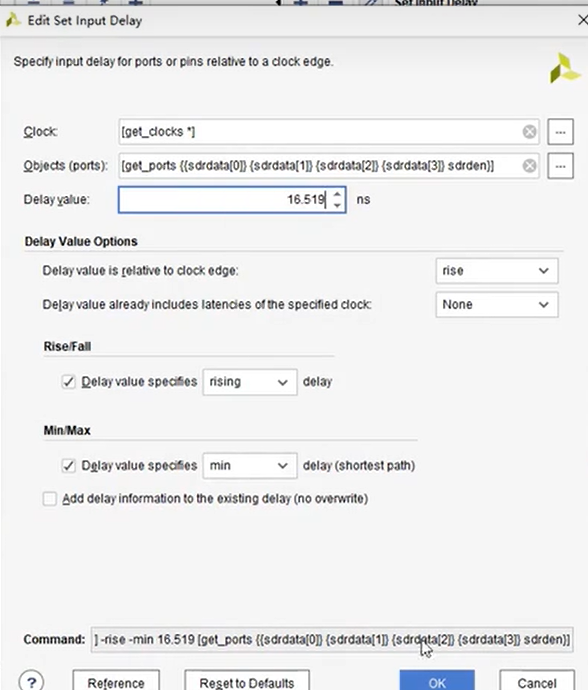

input delay

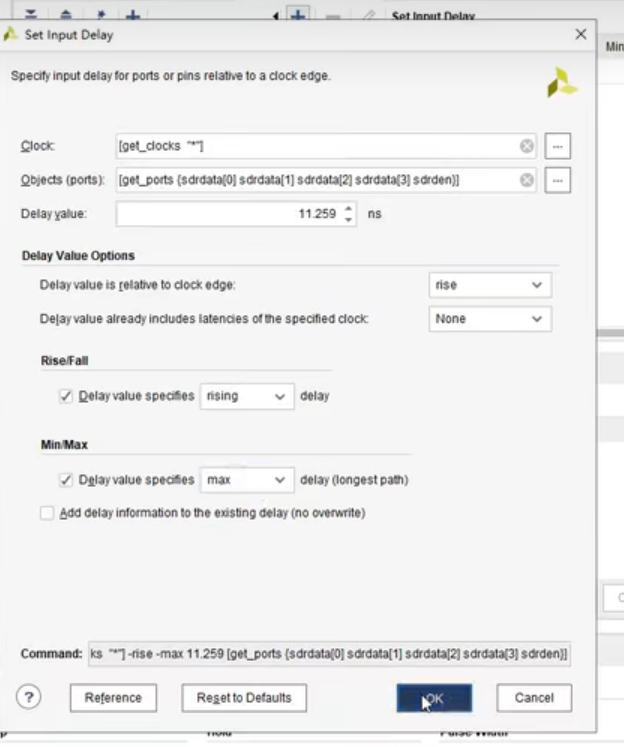

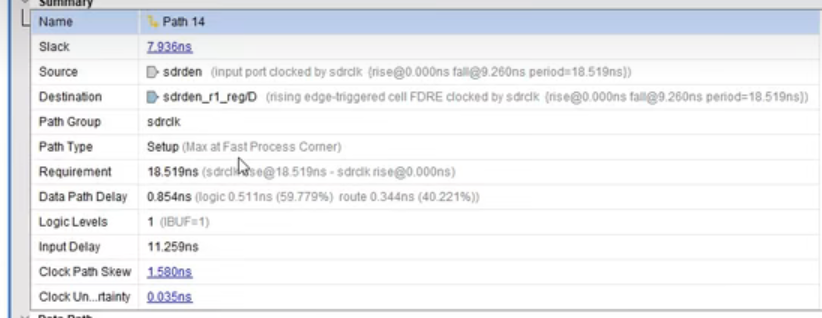

(1/54)=18.52ns 18.52/2=9.259 9.259+2=11.259ns 最大input delay为11.259ns

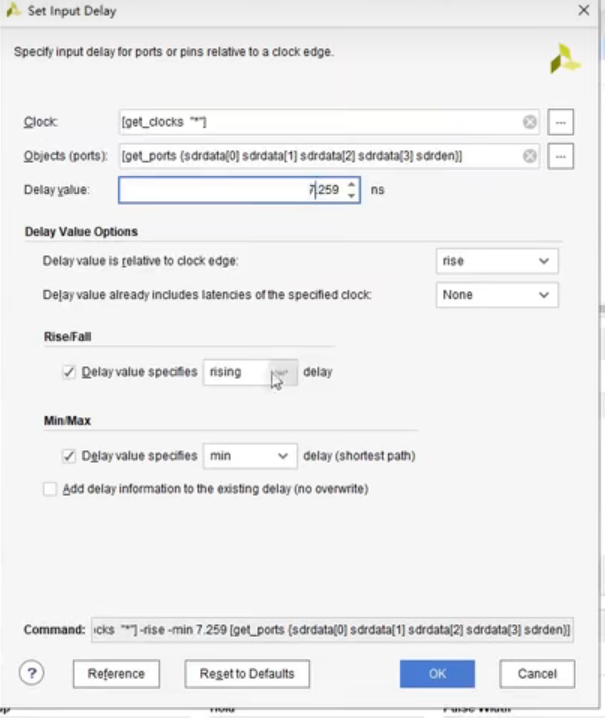

再添加 min input delay 9.259-2=7.259ns

重新生成XDC文件,bit文件

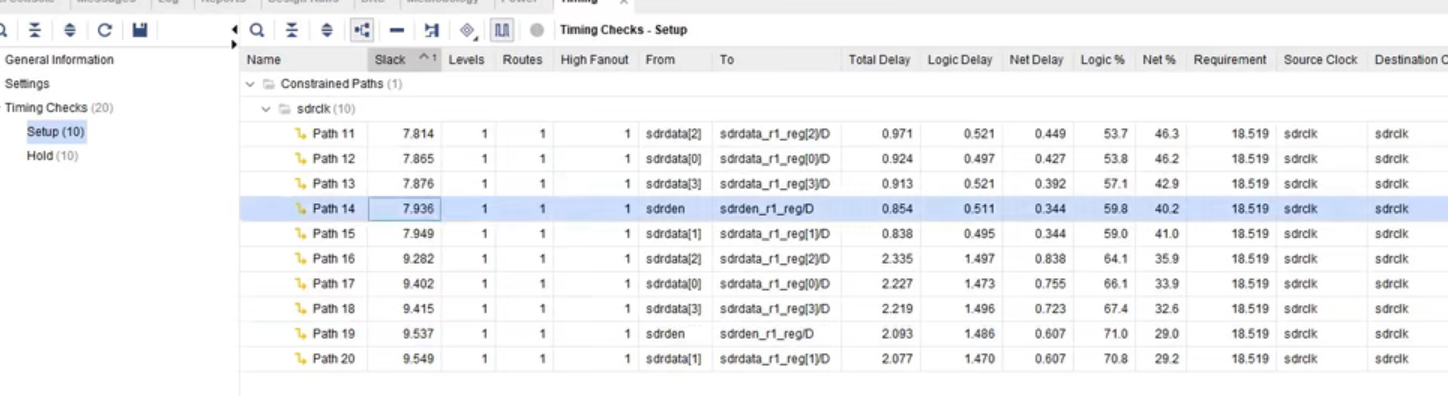

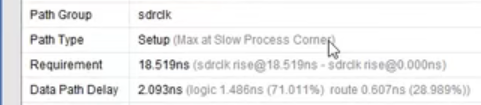

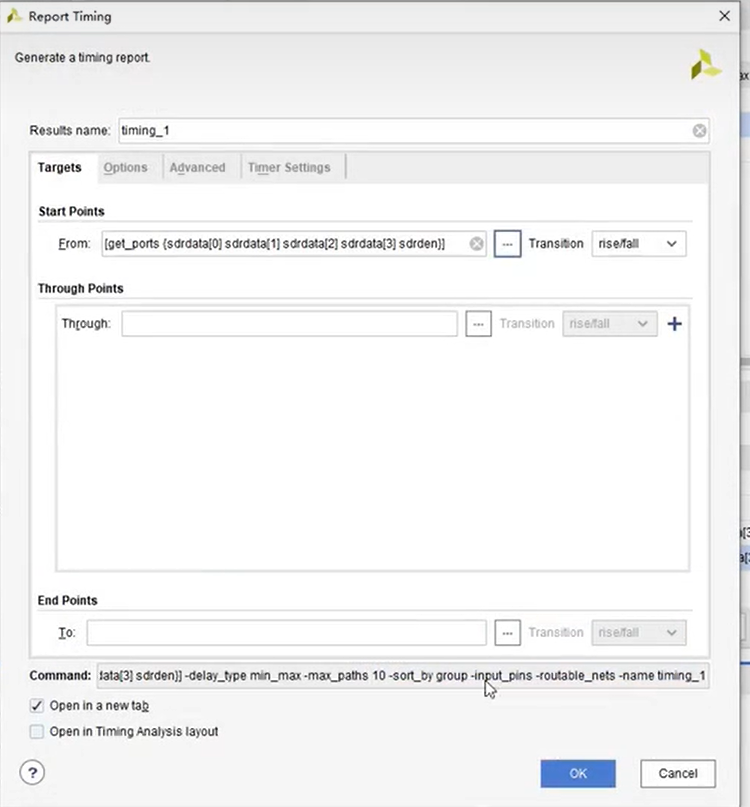

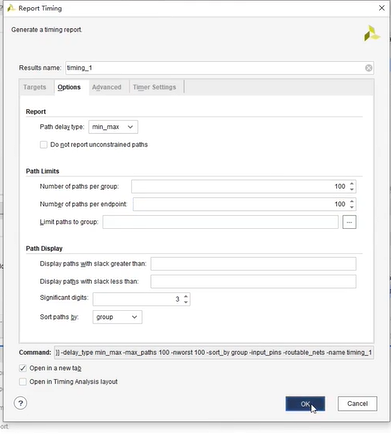

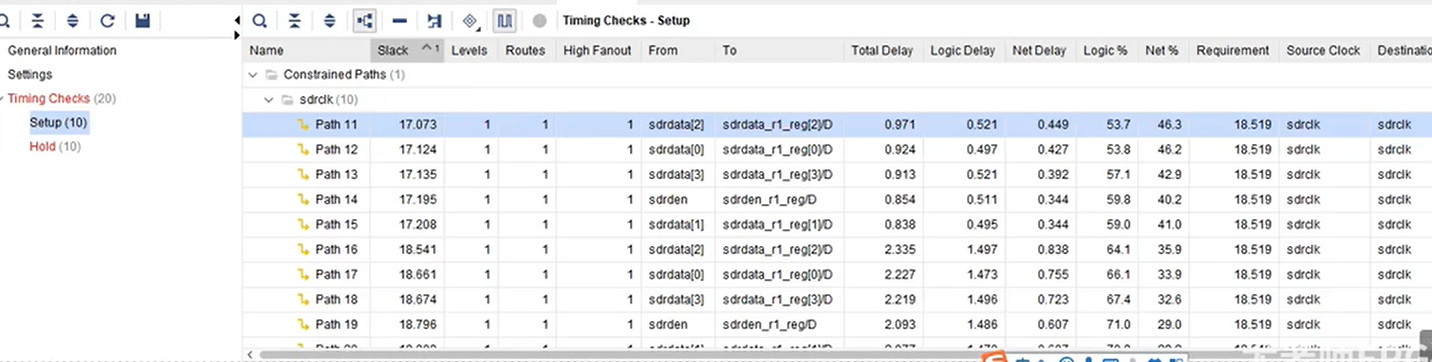

report timing

发现有两个一样的名字的路径,但是slack不一样

这就是endport 不同的环境下分析的路径

fast comer 快速模型

芯片在低温高压,温度低,电压高的临界。这时芯片里的走线,延时都处在最快的情况下

slow 芯片处在高温低压。布线延时增加,速度就慢了

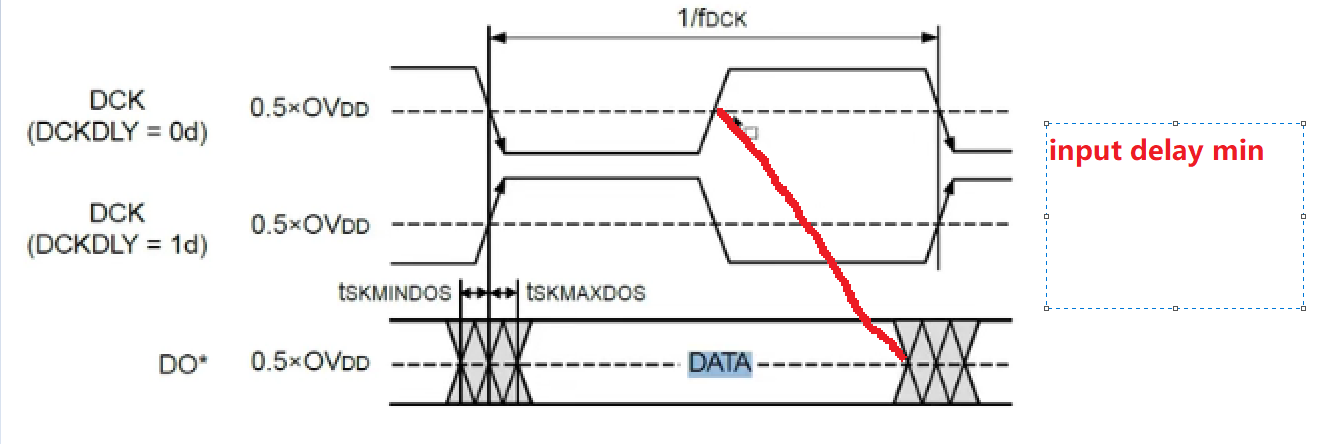

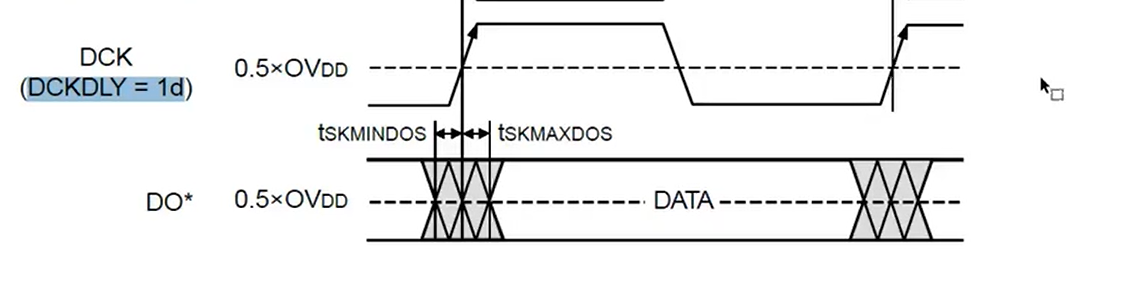

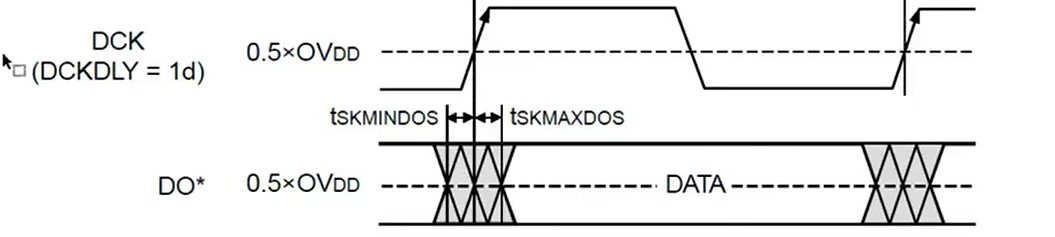

如果上游器件用的是边沿对齐,不是中心对齐

8讲

这次整边沿对齐

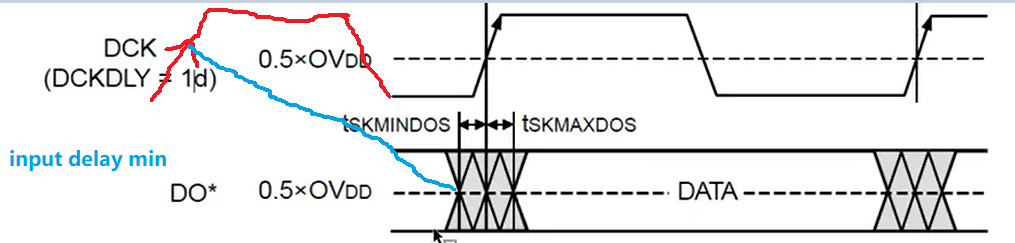

input delay :描述发射沿和数据起始位的延时

数据源是上一个寄存器给的,要说明上升沿射数据起始位的关系

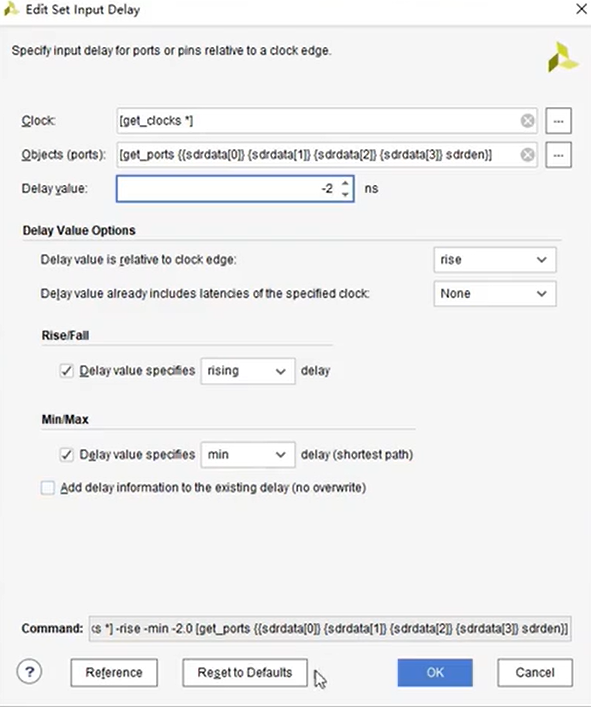

max input delay=2ns

min input delay=-2ns

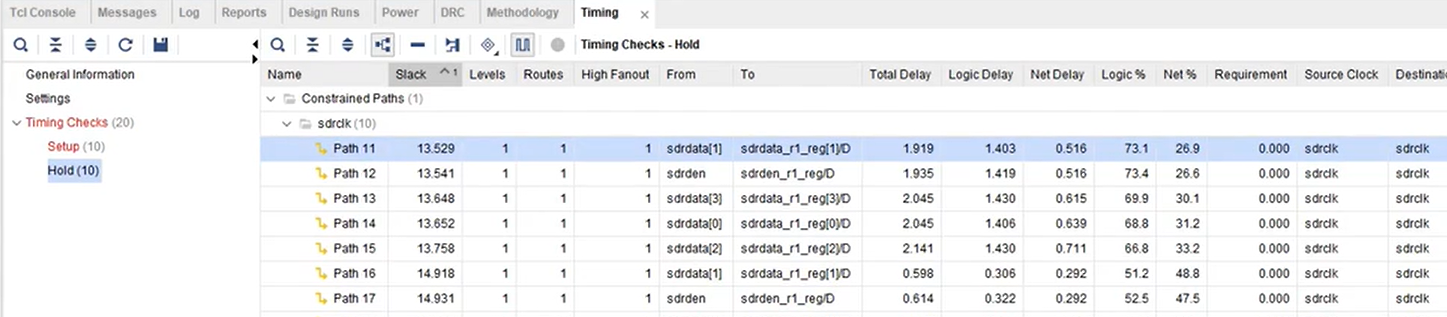

report timing

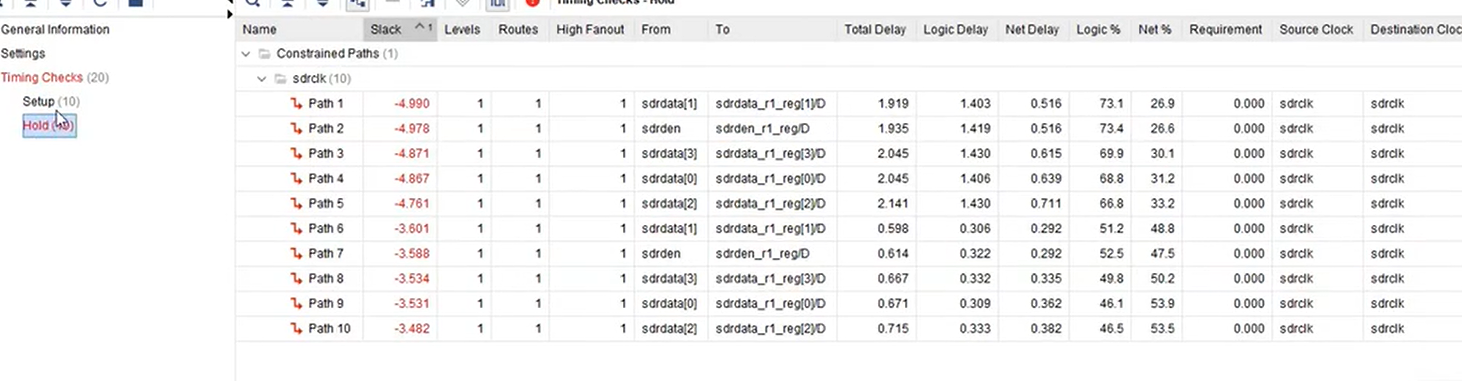

看见hold time 出现违例,setup time 还行

时钟在两个最大最小延时的中间,建立时间余量很大的。

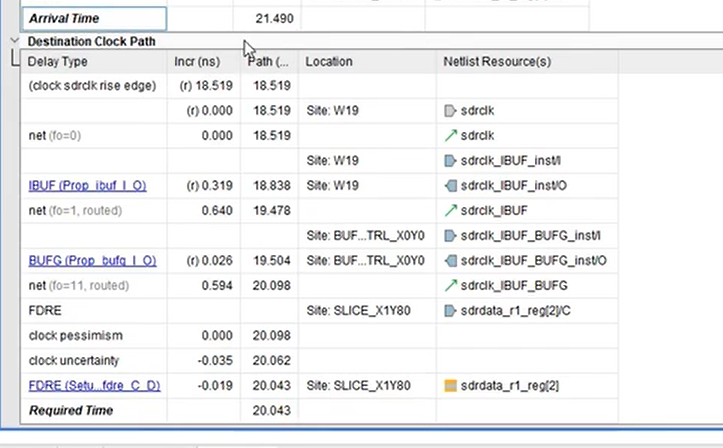

时钟的延时很大,数据基本没有延时

问题出在时钟上,时钟延时太大

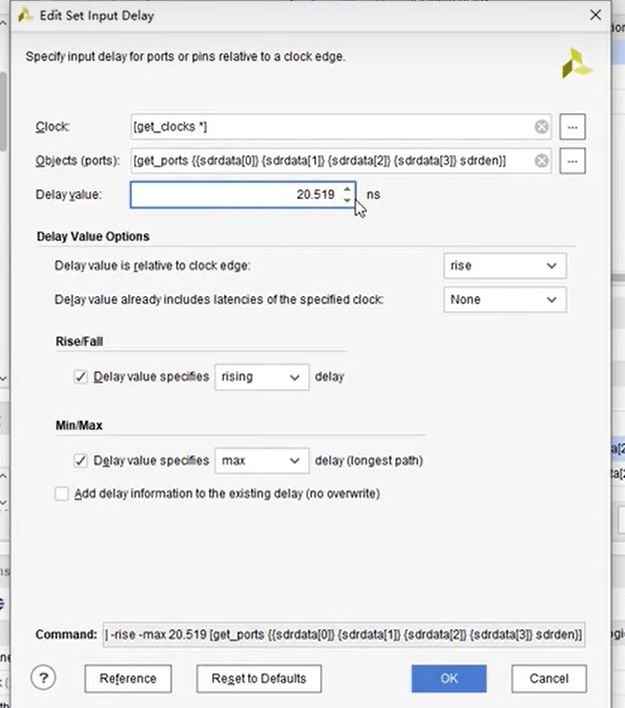

用上一个时钟的上升沿处采集

max input delay=18.519(时钟周期)+2=20.519ns

min input delay=18.519-2=16.519ns

现在变成建立时间余量不够了

时钟到达时间-数据到达时间=建立时间余量,这边明显不对了

所以往前一个周期还是没办法解决问题

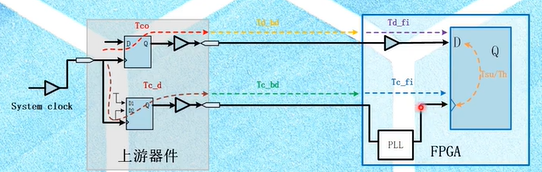

我们就需要进行重新优化设计

我们可以把时钟插入PLL,PLL可以移项,把时钟到达寄存器时钟端的时候可以让相位,采样的沿提前或者拖后 。

并且时钟走过PLL之后PLL还会对从管脚到PLL的这段延时进行补偿

使用PLL之后我们希望用当前的上升沿来进行分析

浙公网安备 33010602011771号

浙公网安备 33010602011771号