时序分析第三讲

保持时间时序分析的讲解

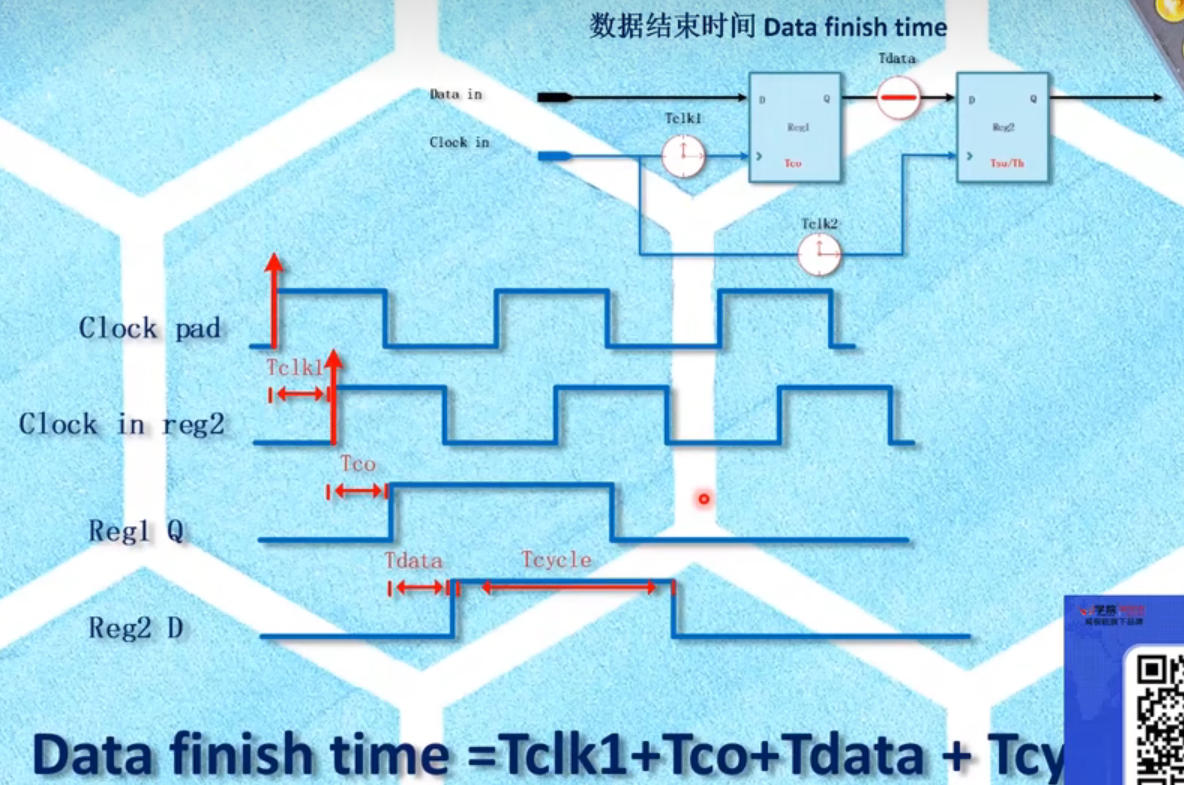

tcycle

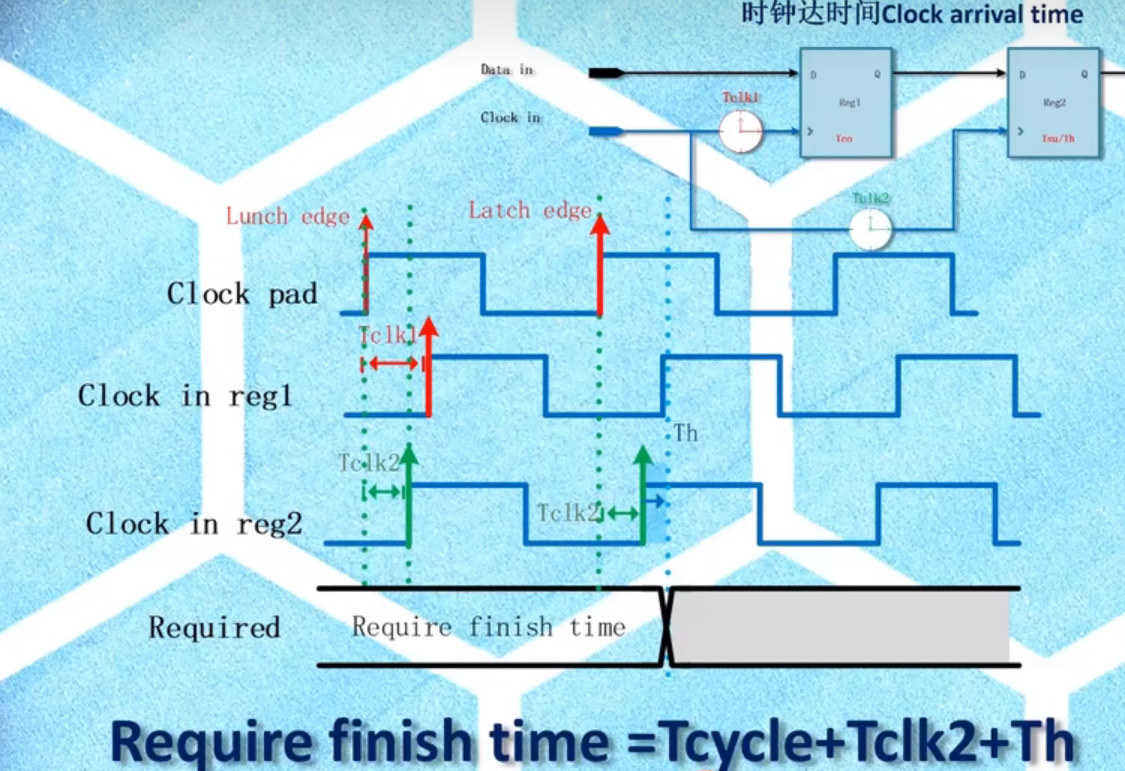

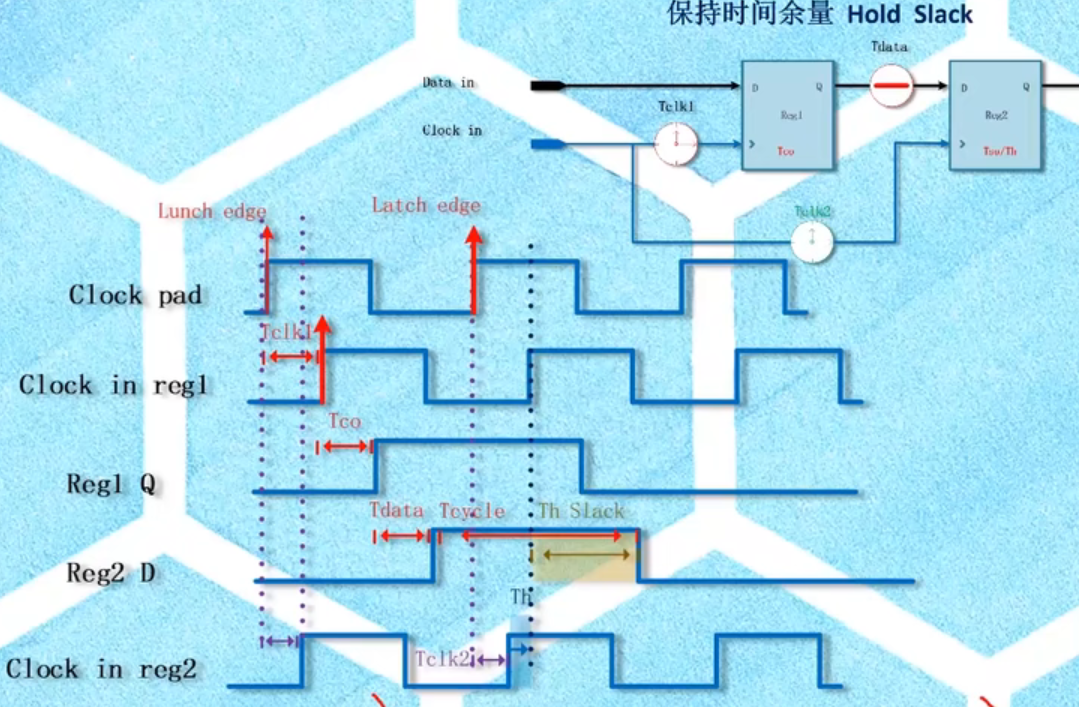

采样沿跟我们数据的结束时间之间的差值就是余量

保持时间的余量跟时钟周期无关

hold slack=TCLK1+TCO+TDATA-TCLK2-TH

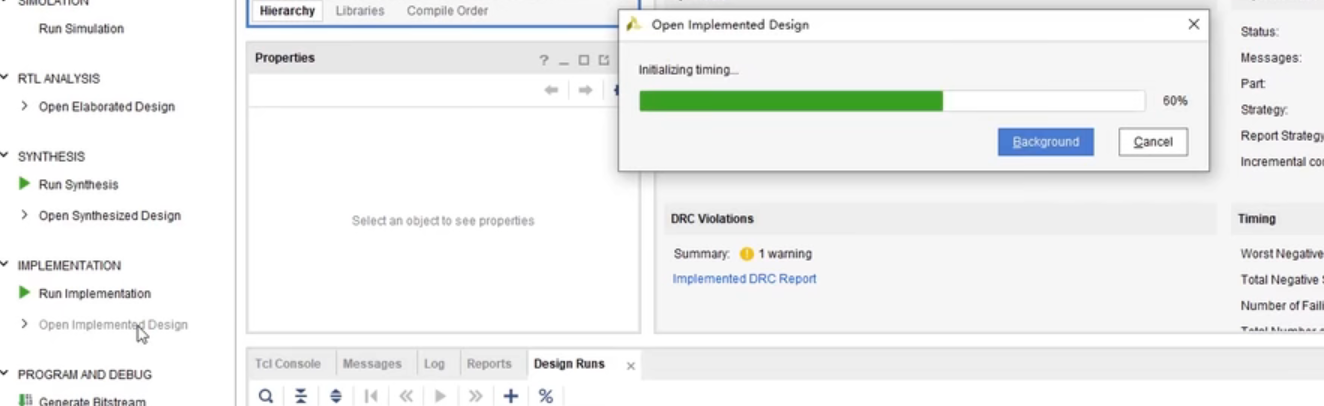

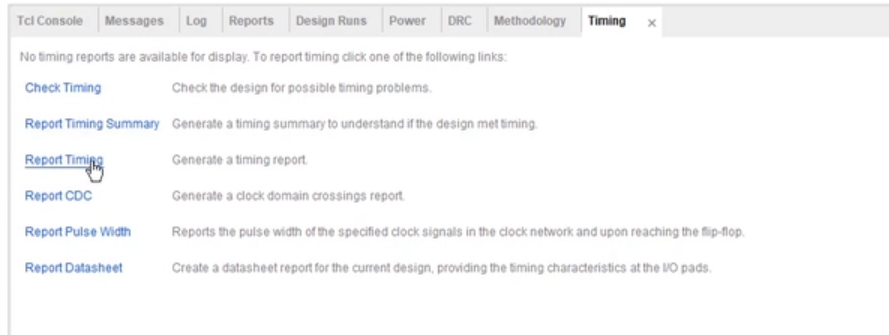

实操

做时序分析的时候最好把管脚绑定好,不然做的数据没有具体的分配,管脚出来的时序分析报告就没有参考意义

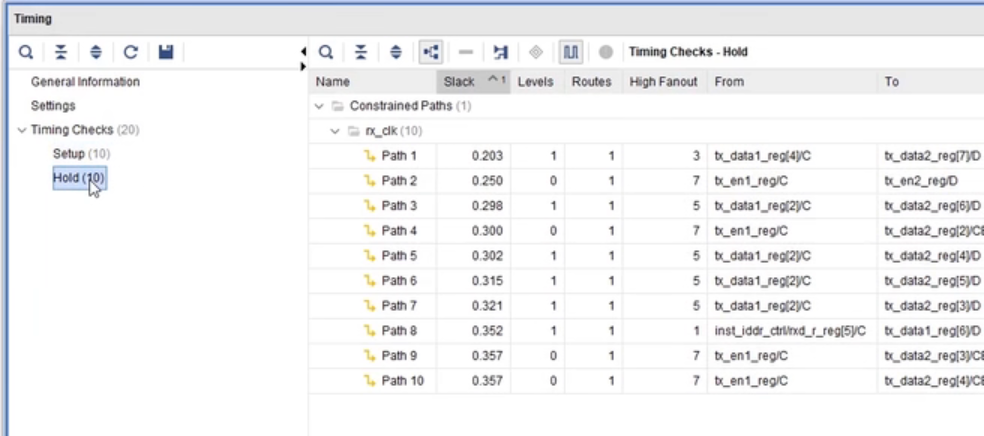

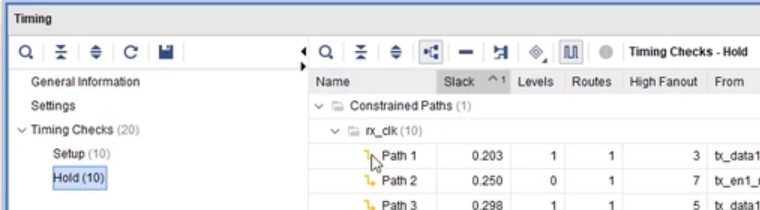

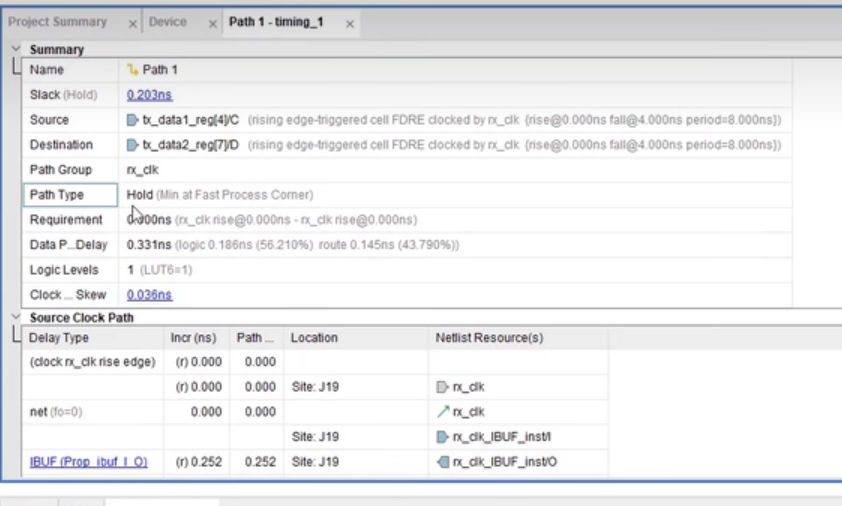

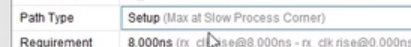

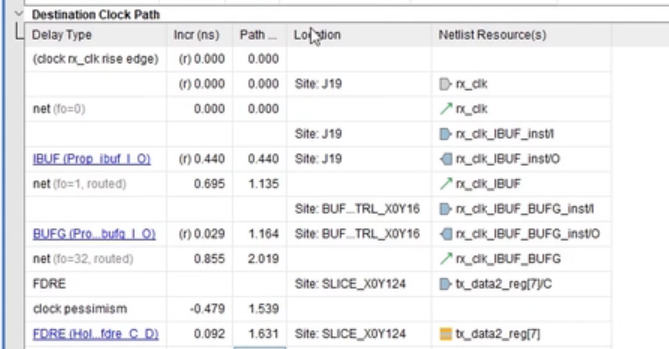

双击打开一个路径

首先我们看路径类型(path type) 有快模型和慢模型。延时最小,电路就处在一个最快的模型

hold slack=TLCK1+TCO+TDATA-TCLK2-TH

为什么选择FAST COMER: TDATA包含了数据核心的或者路径的延时,这个值越大,余量越大。我们希望这个值越小,越容易出问题,所以取最小值的时候。虽然电路是唯一的,它在不同的电压波动,温度波动情况下,这个延时值它并不是一个不变的值,是一个会发生一些变化的值,所以有最大最小值。

另一方面,在建立时间的余量里,这个值越大,建立时间的余量越小

SETUP方面,SLOW COMER,电路最慢的情况,延时最大的情况,也就是TDATA最大值的情况

source clock 到达reg1的clock端 这个时间经历的延时

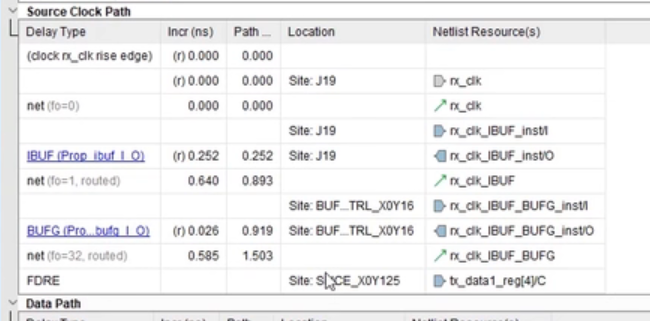

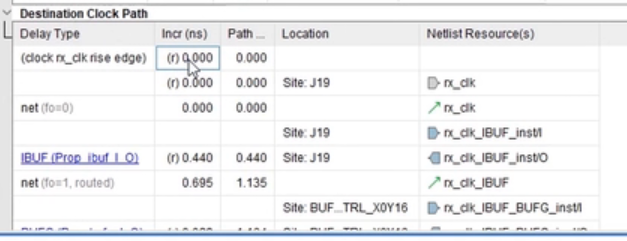

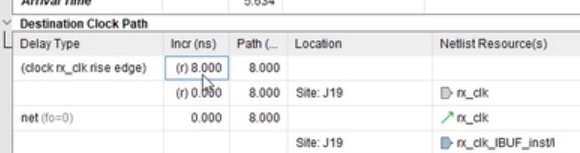

目的时钟,采样时钟 因为hold slack抵消掉了,跟时钟周期无关,所以这边为0

setup slack 与时钟周期有关,所以不为0

约束好时间之后,布局布线就会努力帮我我们布寄存器,使其满足建立时间余量和保持时间余量

约束时钟的意义就是告诉我们我们的 综合,布线工具,让它合理的布线满足你时序的要求

浙公网安备 33010602011771号

浙公网安备 33010602011771号