qflash

要在 3 字节或 4 字节地址模式之间切换,必须使用“进入 4 字节模式 (B7h)”或“退出 4 字节模式 (E9h)”指令。当前地址模式由状态寄存器位(Current Address Mode ) ADS (S16) 指示。

上电后,W25Q256FV 可以在 3 字节地址模式或 4 字节地址模式下运行,具体取决于非易失性状态寄存器位(Power-Up Address Mode) ADP (S17) 设置。如果 ADP=0,设备将工作在 3 字节地址模式;如果 ADP=1,器件将工作在 4 字节地址模式。 ADP 的出厂默认值为 0

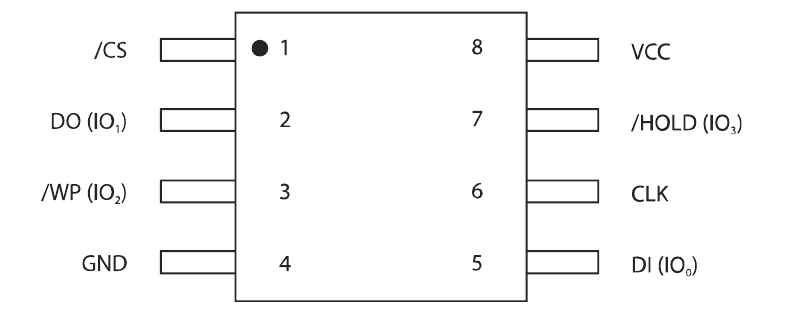

常用封装

-

CS , chip select, 芯片使能引脚. CS拉高时, 芯片处理省电模式, 各数据引脚(D0/D1/D2/D3)处理高阻态. CS拉低时芯片工作, 数据引脚可以传输数据.

-

DO 用于(在CLK下降沿)输出数据或状态. 正常情况下只有DI/DO作为IO引脚, 启用 Quad 模式需要置QE(Quad Enable)位. QE=1时, WP和HOLD分别变为IO2,IO3.

-

WP pin, 低电平有效, 以保护状态寄存器不被写入.

-

GND 接地

-

DI用于(在CLK上升沿)向 Flash 输入指令, 地址 或 数据.

-

CLK, 提供输入输出操作的同步时钟.

-

HOLD pin, 当多个芯片共用 SPI 总线时非常有用. HOLD 为低电平时, DO 引脚变为高阻态, 且此时 DI/CLK 上的信号被忽略. 相当于芯片此时不工作. 假设对一个 SPI FLASH 的页写操作只进行到一半, 此时一个中断来了, 另一个更高优先级的任务要占用 SPI 总线, 此时就可以使用 HOLD 拉低来暂停 SPI FLASH 内部的工作, 等到任务切换回来再让操作继续下去

在I/O模式下,软件需要把命令和数据转化成QSPI Flash协议下的指令,转换之后的指令将被写入Tx FIFO。然后发送逻辑将Tx FIFO中的内容按照QSPI接口规范进行并串转换,最后通过MIO将转换后的数据送到Flash存储器中。在发送逻辑将Tx FIFO中的数据发送出去的同时,接收逻辑会采样所发送的串行数据,进行串并转换后存储到Rx FIFO里面。

如果执行的是读操作,在发送读指令和读地址之后,MIO会在发送逻辑的控制下由输出模式切换成输入模式,从Flash中读出的数据将被存储丰Rx FIFO中。由于Rx FIFO中会同时接收由软件发出的指令,因此我们需要对Rx FIFO中的原始数据进行过滤,从而得到从Flash中读出的有效数据。

浙公网安备 33010602011771号

浙公网安备 33010602011771号