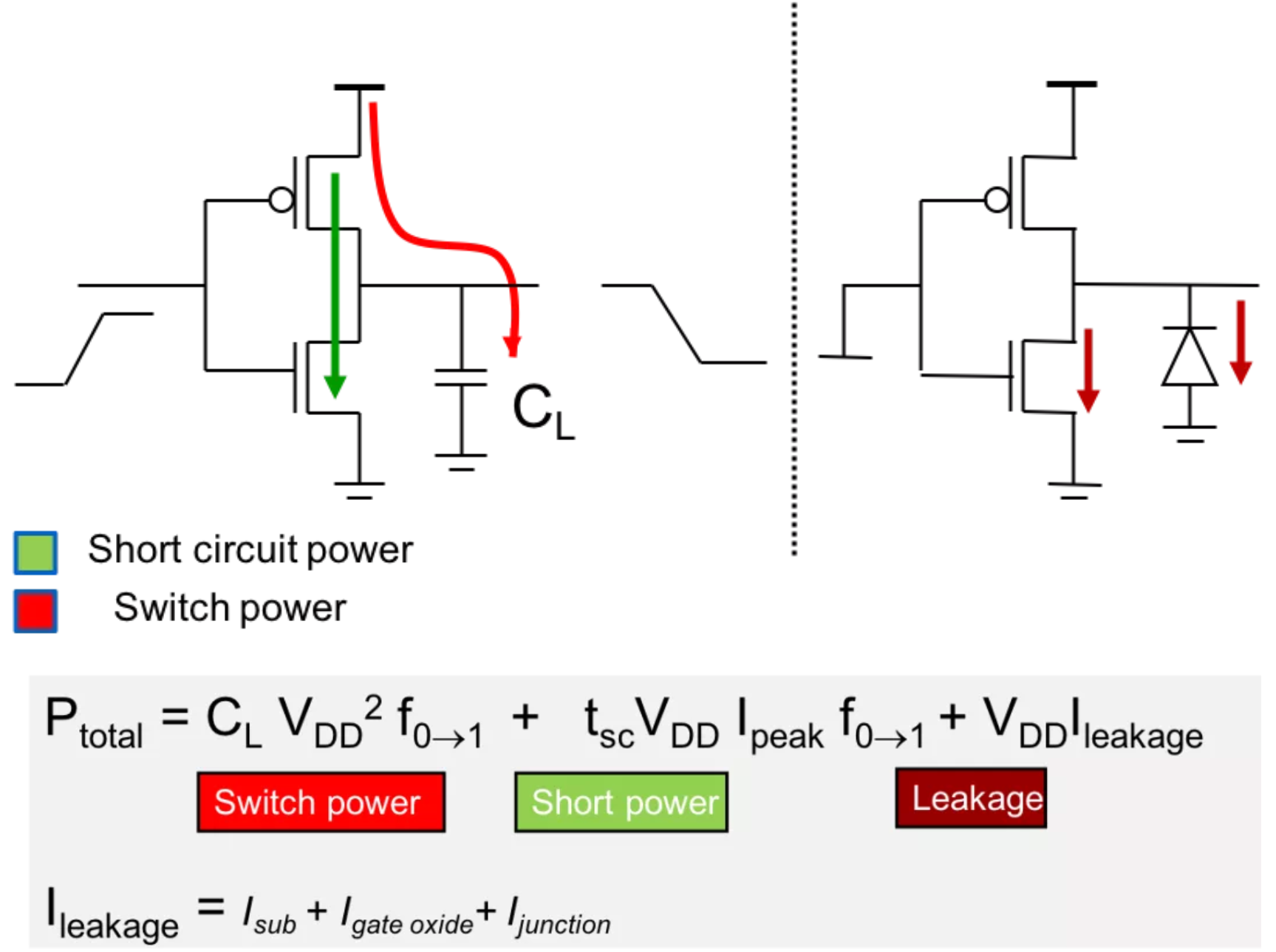

CMOS管功耗 = 动态功耗 + 静态功耗

动态功耗有两种表述,两种表述的区别之处在于:把对管子内部电容充放电消耗的功耗归于谁,第一种表述常见于理论分析,第二种表述常见于EDA工具功耗计算。

第一种表示:

-

动态功耗 = 开关功耗 + 短路功耗

开关功耗:指管子在翻转过程中对『相关电容』进行充放电消耗的功耗,此处『相关电容』包含管子内部结点电容和负载电容。

短路功耗:指管子在翻转过程中,PMOS和NMOS同时导通,从电源VDD到地VSS之间短路通路消耗的功耗。

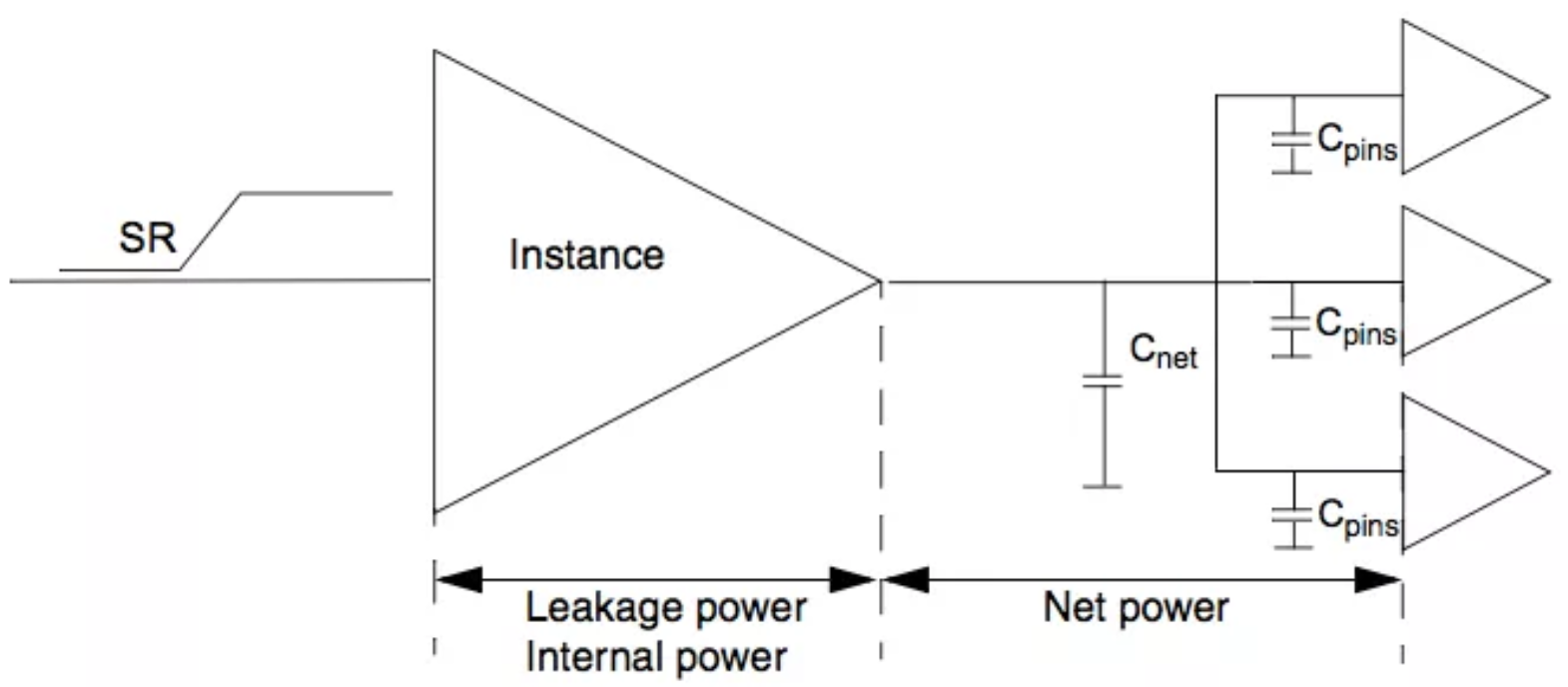

第二种表示:

动态功耗 = 负载功耗 + 内部功耗

负载功耗:指管子在翻转过程中对『负载电容』进行充放电消耗的功耗。

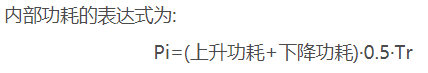

内部功耗:指管子在翻转过程中,对内部结点电容进行充放电消耗的功耗及短路电流消耗的功耗。

EDA工具计算动态功耗时,会分别计算内部功耗和负载功耗。

-

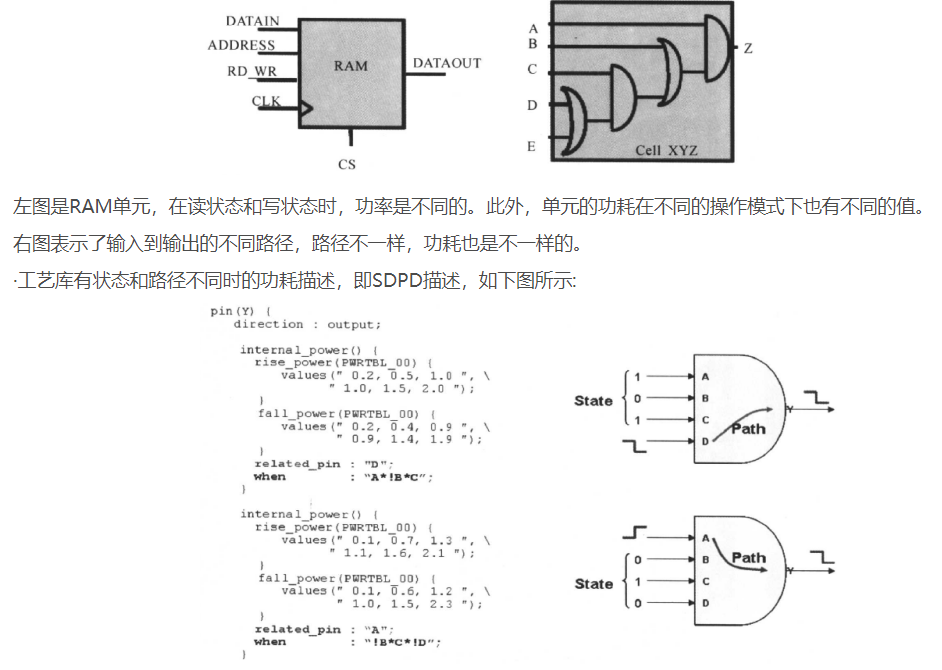

内部功耗:当前方法学将内部功耗模拟成输入transition跟输出负载 (load capacitance) 的函数,foundry会将每个管子的内部功耗定义在library中,常见的是二维表格,index是(input transition, output load cap),偶尔也有三维表格,index是(input transition, output load cap, second output load cap)。

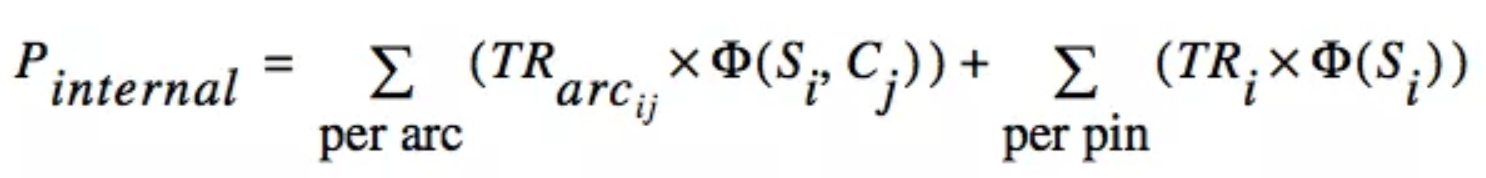

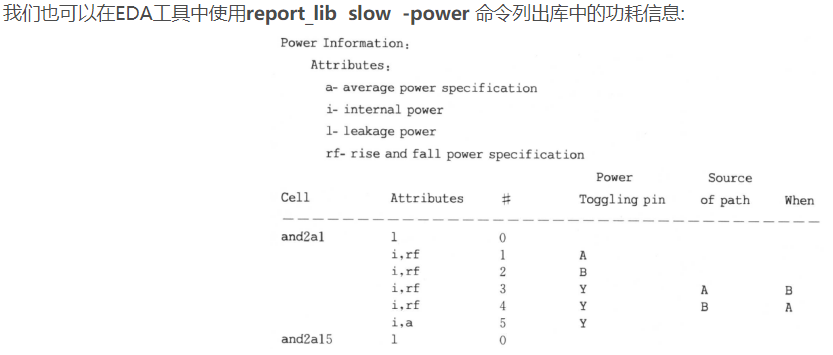

在library中会分别定义cell的rise_power 和fall_power。通常,在90nm之后对每个cell 会根据每个输入pin的状态和每条timing arc分别定义内部功耗,即所谓的:path dependencies internal power。库一定的情况下,每个EDA工具的计算公式应该大差不差,此处以Genus的计算公式为例:

-

TR 指一个arc 或pin上有效的toggle rate. arcij 的有效toggle rate取决于该arc被激活的概率 (probability) 和对应输入pin 的toggle rate。

-

Φ 是从library中查表得到的internal power值。

-

Si 是致输出发生翻转的输入pin的transition。

-

Cj是输出pin的负载电容。

例:以2输入的与门为例,上述library片段中定义了A1 pin到Z pin的内部功耗,假设A1的transition是18ps, Z的load是0.336pf, A1的total rate 是0.5, probability是1,因为在library中transition index没有18ps,需要在12和24ps之间做插值,则该与门的内部功耗为:

toggle_rateA1 × probabilityA1 → Z × ΦA1 → Z(0.0018, 0.336)

=0.5 × rise_power(0.0018, 0.336 ) + 0.5 × fall_power(0.0018, 0.336 )

= 0.5 × 0.0061 + 0.5 × 0.0059

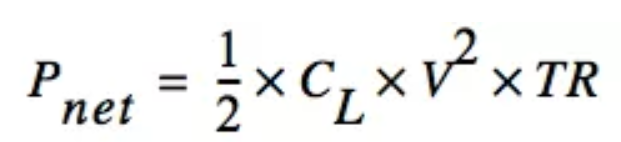

负载功耗:此处的负载包括这个cell 驱动的所有net 和所有sink cell输入pin的电容,其计算公式为:

-

CL 是负载电容 = sum(capacitances of the net, input pins driven by the net). 在genus里可以通过attribute pin_capacitance 和 wire_capacitance 得到对应的值。

-

V 是工作电压。

-

TR 是toggle rate.

3.单元功耗

浙公网安备 33010602011771号

浙公网安备 33010602011771号