优化 --cache

注意:配置成cache的地址段就不能再放入data and code,因为链接的时候,是不包含cache地址段的,如果想使用L1DSRAM或L1P SRAM,则应该相应减小cache段大小。

1:Keep critical code and data on-chip

2:Put non-critical code and data off-chip

#pragma CODE_SECTION(code, “section”); //将代码数据指定段

#pragma DATA_SECTION (symbol, “section”); //将数据指定段

#pragma DATA_ALIGN(InBuffA, CACHE_L2_LINESIZE) //buffer按L2 cacheline对齐,并保证其为cachelines size的整数倍

应用级优化 (application-level optimization)

1) 合理设置cache大小,尽量将DMA用到的buffer开在片内RAM上

2) 将一般性程序代码和数据放到片外RAM,将DSP型代码和数据放到L2RAM。所谓一般性代码是指带有很多条件分支转移的指令,程序执行在空间上有随意 性,不利于流水线的形成,外在片外可以发挥L2CACHE 4 way的优势。DSP型代码是指算法型的代码,放在L2RAM,CPU stall 时间少,可以充分发挥DSP速度快的优势。

3.2 程序级优化(procedural-level optimization)

1)选择合适的数据类型。能用short就不要用int。

2)将同一个函数要处理的数据尽量在内存中连续存放。

3.3避免L1P read miss

这种情况发生在一个循环体中有两个或以上的函数要执行,要利用#pragma DATA_SECTION伪指令将和CMD文件将其在内存中相邻定位,这样不会发生两个程序对应L1P中相同line所造成的冲突缺失。

如果循环体中的两个函数大小超过L1P容量,将这两个函数分别放到两个循环体中。这样做会造成中间数据变量的加大。

3.4避免L1D read miss

利用#pragma DATA_SECTION伪指令将函数要同时处理的数组在内存中相邻存放。最好再用#pragma DATA_MEM_BANK 将数组内存对齐

Tell Compiler more information

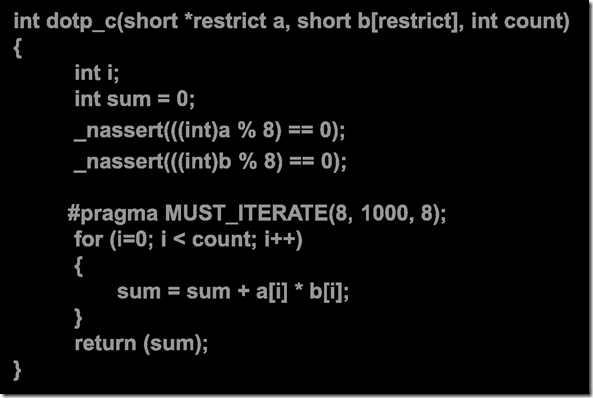

#pragma MUST_ITERATE(min, max, multiple);

放在循环体之前,告知循环次数,改善软件流水

其中multiple参数必须有,循环执行次数必是multiple的整数倍。这个信息对编译器使用软件流水技术非常重要

_nassert((int)x % 8 == 0);

是个断言语句。对条件进行判断,如果为1,通过,为0,则抛出异常

浙公网安备 33010602011771号

浙公网安备 33010602011771号