电源门控单元和器件

多电压域设计

降低功耗的方法

- a) 功耗与电源的二次方成正比,因此降低电源电压是降低功耗的有效手段。但是带来的负面影响是:降低了晶体管的切换速度,因此而降低了晶体管的阈值电压,又会使得噪声容限减小、亚阈值漏电增加

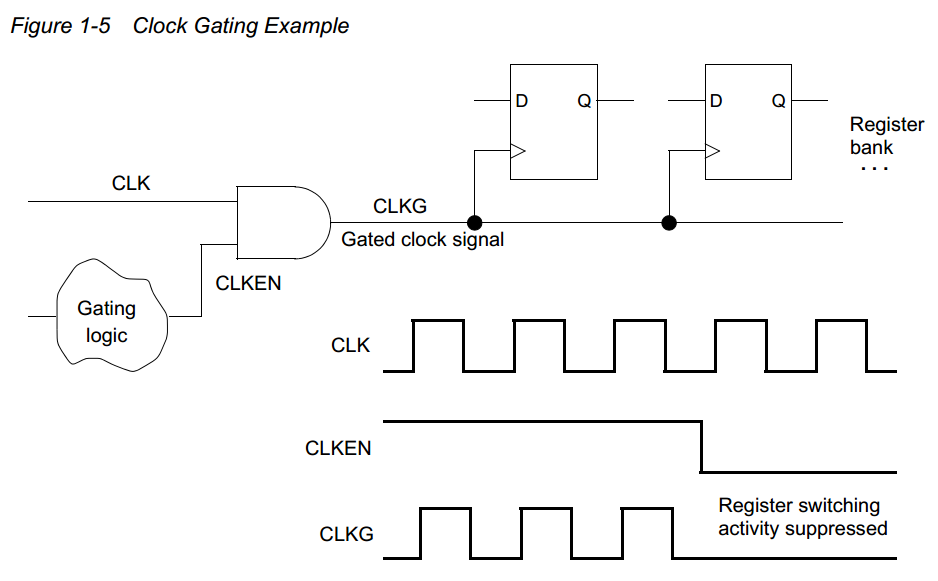

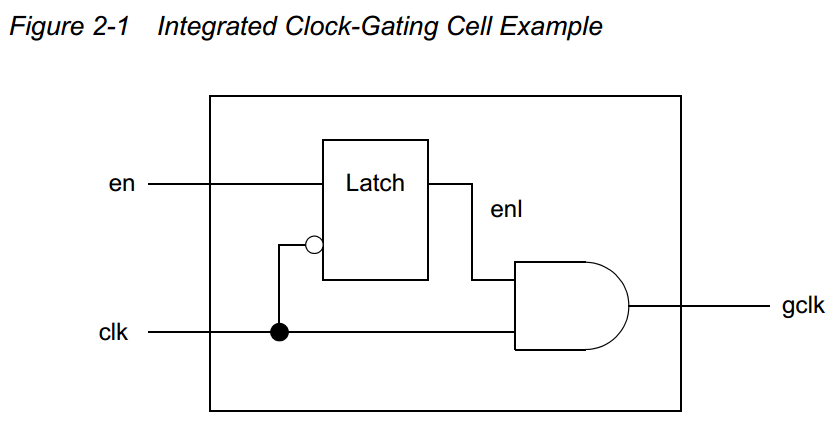

- b)时钟门控

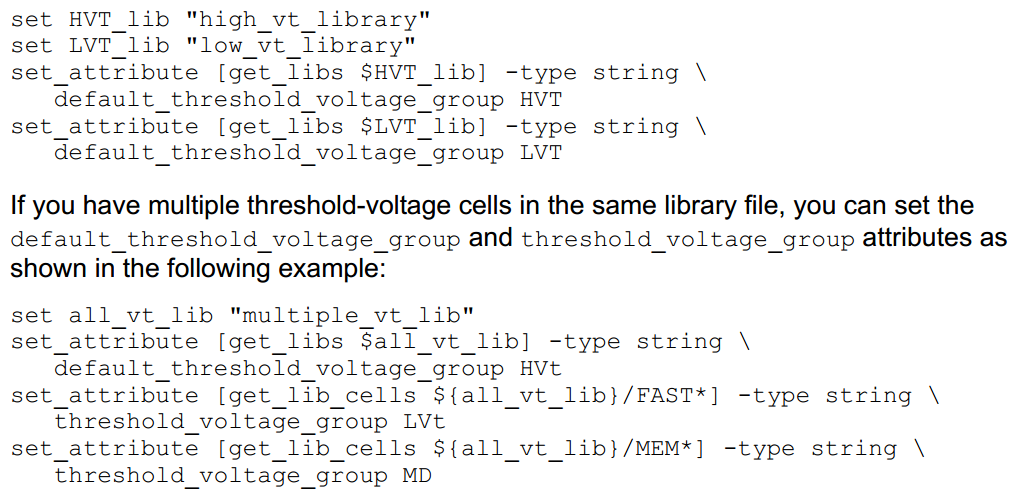

- c)使用多阈值库单元:低阈值单元速度快,但漏电高;高阈值单元速度慢,但漏电低。可以在时序上的关键路径使用低阈值单元提高速度,在非关键路径上使用高阈值单元降低漏电。但是使用高阈值单元会导致信号的翻转变慢,过渡时间变长,从而进一步导致短路功耗增加。

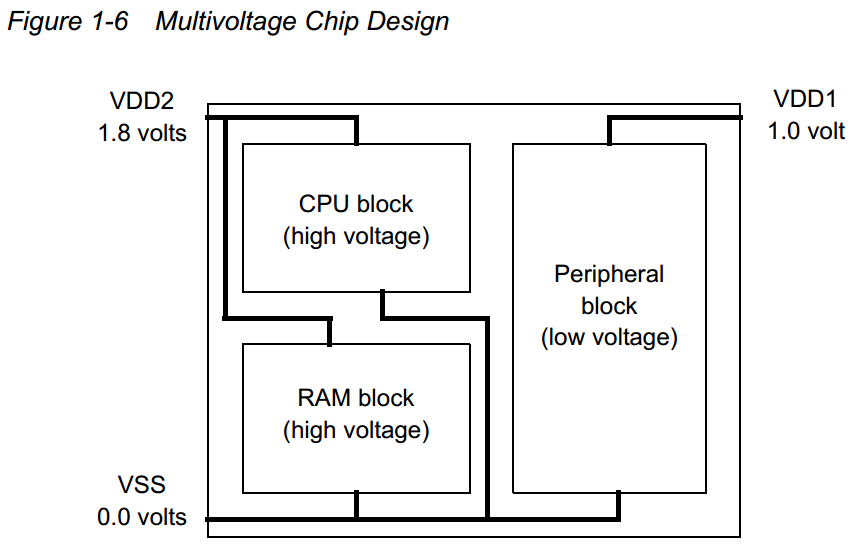

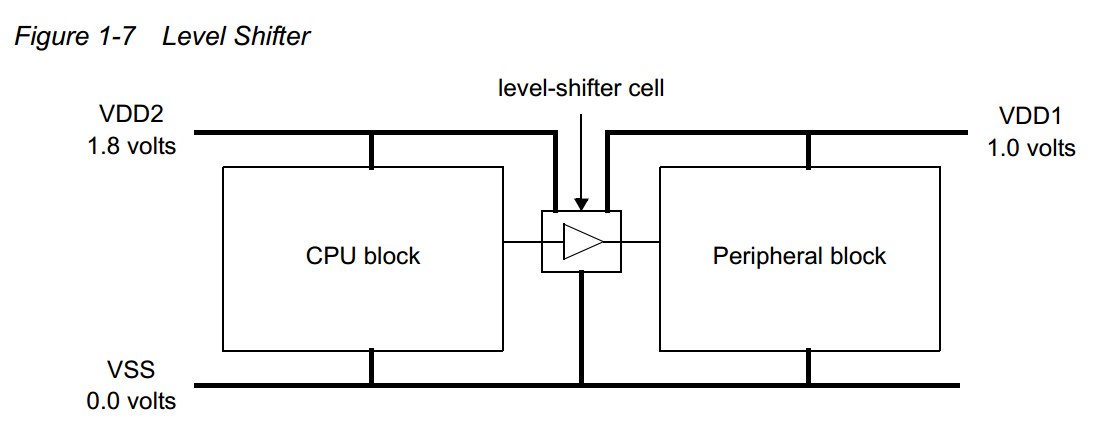

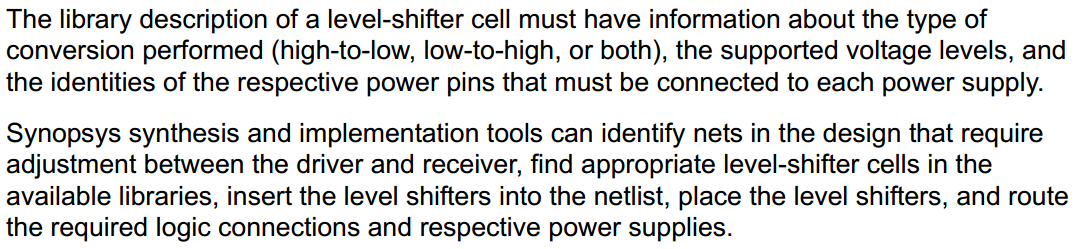

- d)多电压域设计:速度要求高的模块放在高电压域,速度要求不高的放在低电压域,两者之间信号交互需要通过level-shifter 单元转换

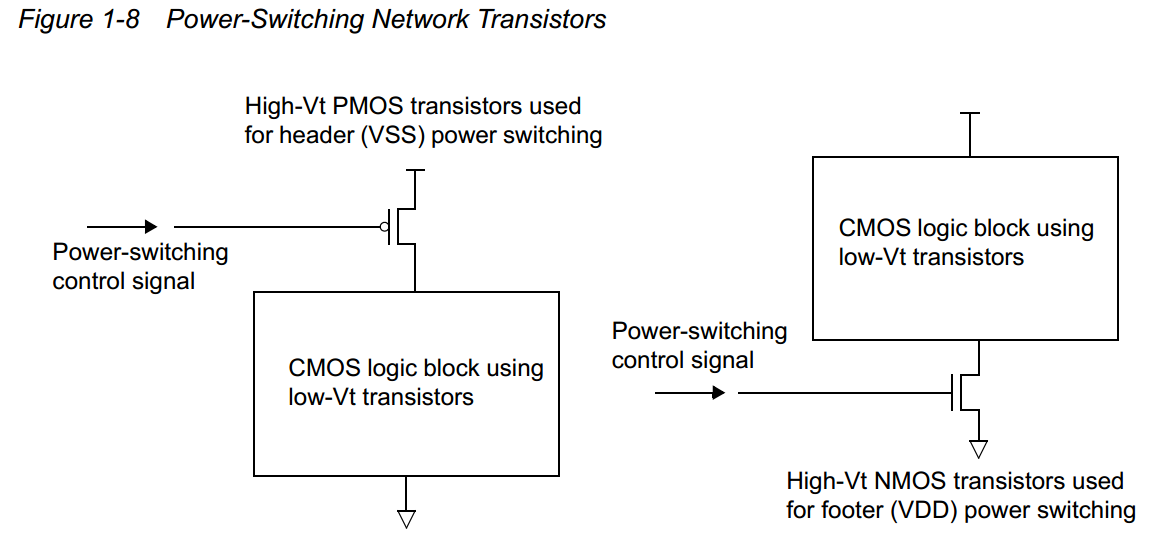

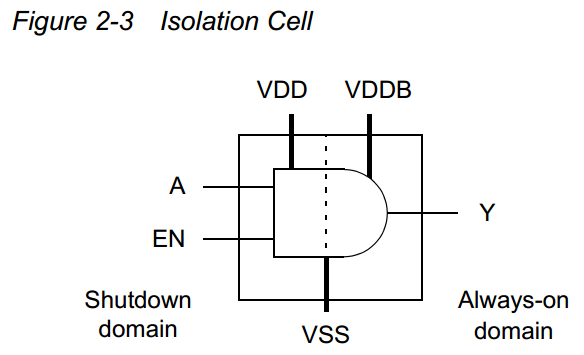

- e)电源门控:可以同时降低动态和静态功耗,存在的挑战有:the need for a power controller, a power-switching network, isolation cells, and retention registers.

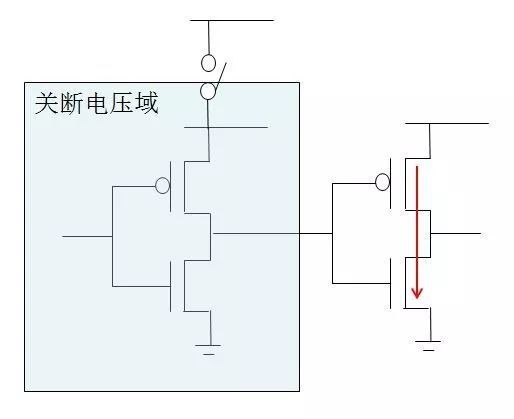

在Power-down模块和Always-on模块之间需要添加隔离单元,其作用是当被门控的模块断电之后可以为不断电模块提供一个稳定的输入驱动,如图所示的隔离单元在左边模块不断电的情况下正常传递信号,当断电时维持固定逻辑“0”

在Power-down模块和Always-on模块之间还需要添加保持寄存器,其作用是在模块断电之前拷贝主寄存器的数据到影子寄存器,在模块重新上电之后再从影子寄存器中恢复数据到主寄存器。

隔离单元

隔离单元是由综合工具插入的附加单元,用于隔离从电路的电源门控域到always on域的总线/导线。隔离列表是由所有需要隔离单元的总线/导线组成的列表。在隔离列表中,我们将net的箝位值指定为逻辑0或逻辑1,因此综合工具将插入隔离单元。

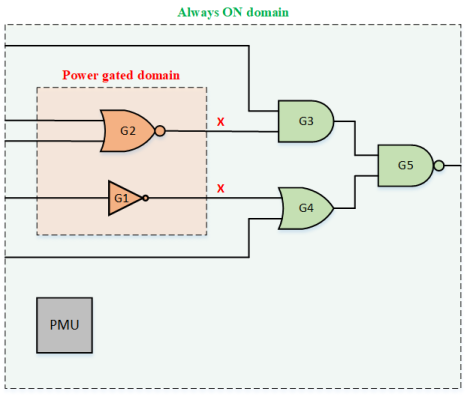

图1:具有可切换(或门控)电源域的简单电路

考虑一个非常简单的电路,如图1所示,其中G1和G2处于电源门控域。现在,在低电源模式下,当电源门控域的电源被切断时,G1和G2的输出变为未知(或“X”)。因此,always on域中的逻辑将受到其影响。为了防止always on域的损坏,我们根据设计将跨越电源域的net箝位到一个值。

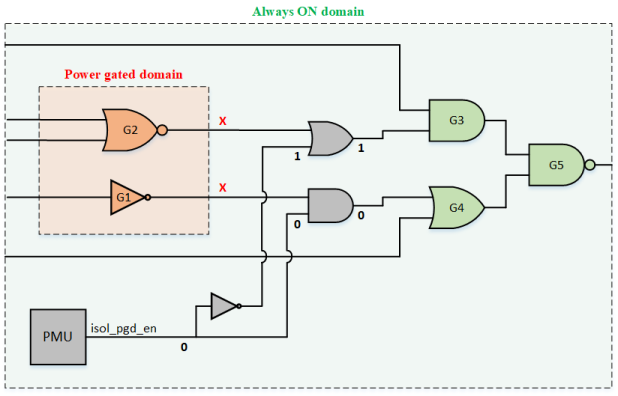

在这里,我们将把G1和G2的输出线放在隔离列表中,并将值分别箝位到逻辑0和逻辑1。综合后的电路将如图2所示。

图2:图1插入隔离电源后的电路

通常,如上图所示,当我们将导线箝位到值0时,综合工具会插入AND门,其一个输入连接到来自设计内部电源管理单元(PMU)的隔离使能信号,类似地,当我们将导线箝位到值1时,综合工具插入OR门,其一个输入连接到隔离使能信号的反相版本。这些由工具插入的“与”和“或”门被称为隔离单元。

由于PMU管理设计中的所有电源门控,因此它在电源门控之前启用隔离使能信号,以确保在电源切断后没有“X”值传播到always on域。在上图中,isol_pgd_en是隔离使能信号,是一个有效的低信号。

电平转换器单元

电平移位器(LS)是多电压设计中使用的特殊标准单元,用于将一个电压电平转换为另一个电压水平。由于多电压设计具有一个以上的电压域,电平移位器是用于将一个信号从一个电压域到另一个电压域的元件。像隔离单元一样,电平移位器是通过综合工具插入的。

低电平至高电平转换单元

低到高LS用于从较低电压域到较高电压域的信号交叉。

它基本上放大了源信号,从而可以在目的域中正确地对其进行解释。假设0.7V信号从0.7V电压域穿越到1.0V电压域。现在,在较低电压域中,它对应于逻辑-1,但在较高电压域中它既不是逻辑-1也不是逻辑-0,因此在没有低到高LS的情况下,信号变得未知(或“X”)。

高电平至低电平转换单元

高到低LS用于从较高电压域到较低电压域的信号交叉。

它基本上衰减了源信号。尽管为从较高电压域到较低电压域交叉的信号设置LS是可选的,因为信号将在目的域中被正确地解释,但通常我们设置LS以避免由于源信号的高电压而对较低电压区域的晶体管施加应力。

双向电平移位器

当使用动态电压缩放或动态电压和频率缩放时,源和目的地之间的电压关系可能随着操作时间而改变。在这种情况下,我们需要能够将低电压信号和高电压信号转换为低电压信号的电平转换器。

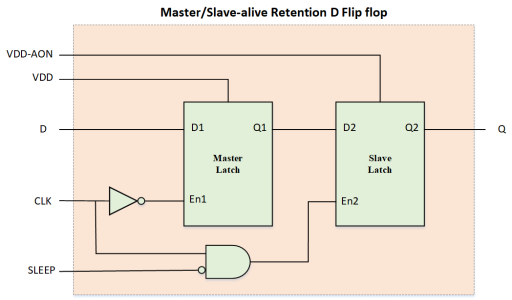

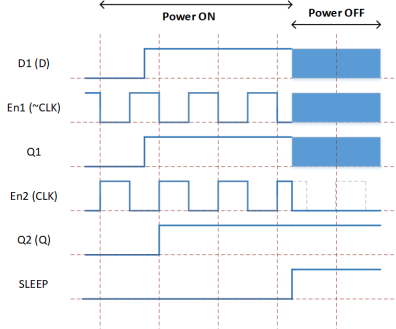

retention cell

retention cell是一种连续单元,当主电源关闭时,它可以保持其内部状态,并能够在通电时恢复状态。retention cell可以通过多种方式实现。最常见的retention cell类型之一是主/从活retention cell。它由一个常规触发器组成,其从锁存器在保留操作期间将数据存储到位。存储数据的锁存器由“始终开启”电源导轨供电,并采用高阈值晶体管来降低泄漏功耗。它有一个“睡眠”信号,控制cell的保留操作。

为什么我们需要retention cell

在某些情况下,控制触发器的状态需要在电源门控(power-gated,PG)模式期间保持,因为PG单元的输出在PG模式中变为“X”。因此,当电源恢复时,逻辑将进入亚稳态。为了避免这种情况,我们可以简单地复位cell,但我们必须从初始默认状态开始

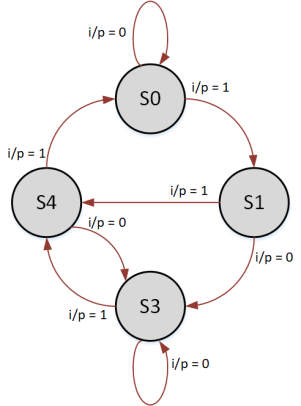

考虑一个简单的FSM,它在电源门控(PG)域中,但输入来自常开(AON)域。FSM有四个状态和一个输入,如图1所示。假设当设备移动到电源门控模式时,我们处于状态S2,因此电源被切断。现在,一旦电源恢复,我们将有一个已知的输入值(因为它来自AON域),但FSM状态将是未知的,因此我们必须复位FSM,并再次从状态S0开始。

因此,每当输出逻辑进入电源门控PG模式时,一旦电源恢复,我们就必须复位该逻辑。因此,为了快速跟踪状态的加电恢复,使用retention cell,因为它可以以PG模式存储状态。

图1:简单FSM的状态转换图

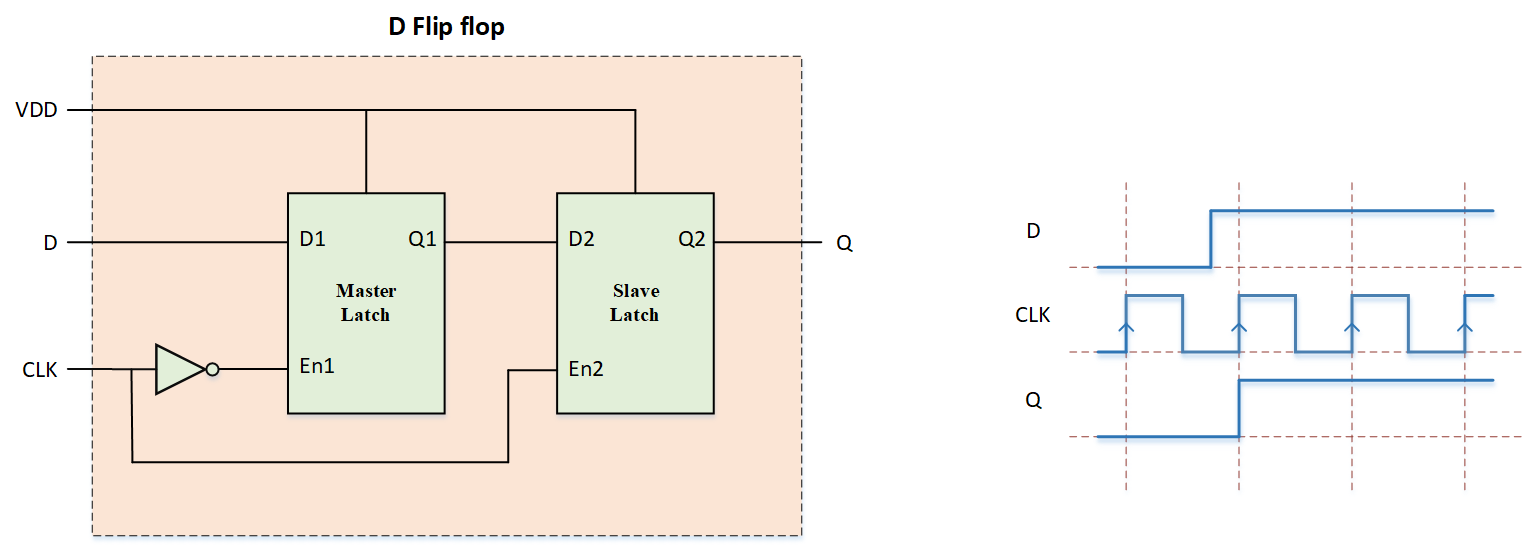

常规正沿触发D–触发器

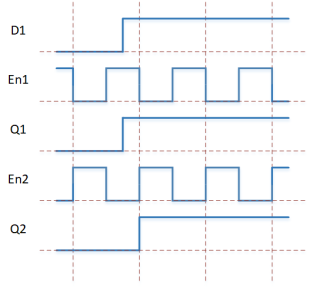

在讨论retention cell之前,让我们先研究一个常规的D–触发器。它有两个锁存器,当它的使能信号为高时,锁存器被使能。

图2:一个规则的正沿触发D触发器和一个时序图,显示了输出如何因输入的变化而变化

所有内部信号的详细信息——

图3:显示图2中所示转换的所有内部信号的时序图

retention cell(主/从激活保留触发器)

图4:主/从激活保持触发器

如图4所示,通过锁存器连接到另一个始终接通的电源导轨(AON)。现在,当单元移动到电源门控模式时,SLEEP信号被断言,VDD电源被切断,因此主锁存器是死的,但从锁存器将继续存储数据。为了防止存储的数据损坏,SLEEP信号确保从锁存器的使能引脚为低电平。为了简单起见,上面没有显示锁存器的复位和置位,但SLEEP信号也确保置位和复位在保持模式期间保持不活动。

图5:时序图显示了保持触发器如何在电源门控期间将其存储值保留在从锁存器中

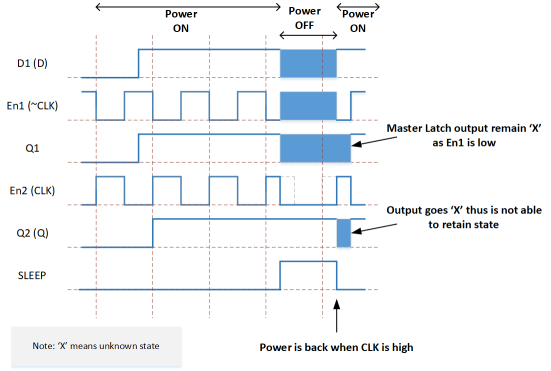

问题——

- 如前所述,在主/从retention cell中,以电源门控PG模式存储数据的锁存器由高Vth晶体管实现,以减少泄漏功耗。由于低Vth晶体管锁存器更快,因此高Vth单元的CLK到Q延迟增加,从而影响性能。

图6:时序图显示了主/从激活保持触发器中的问题(在给定场景中,当电源恢复时,输出变为未知)

- 只有当CLK较低时,此主/从活动保持单元才能检索状态,主要由于以下原因

- 主/从活retention cell的缺点可以通过使用其他类型的retention cell来解决,这有其自身的缺点,如面积增加。

- 所有类型的状态保持单元都需要两种类型的电源——一种是在PG模式下关闭的可切换电源,另一种是AON电源。这在电源routing区域要求中引入了一些complications and penalties 。

f)动态电压频率调节

在运行过程中,为了满足负载要求而动态地改变电源电压和工作频率,称为动态电压和频率调节。

3)统一电压格式(UPF)

使用UPF命令,可以为芯片设计指定电源网络、电源开关、隔离、保持和电源管理等。

库的要求

1)Liberty PG引脚语法

为每个单元的供电引脚指定供电电源。

2)时钟门控单元

集成的时钟门单元将时钟门的各种组合和时序元素集成到单个库单元中。

3)多阈值单元

可以使用属性定义多阈值单元:

4)电平转换器

双向信号不能用电平转换器

5)隔离单元

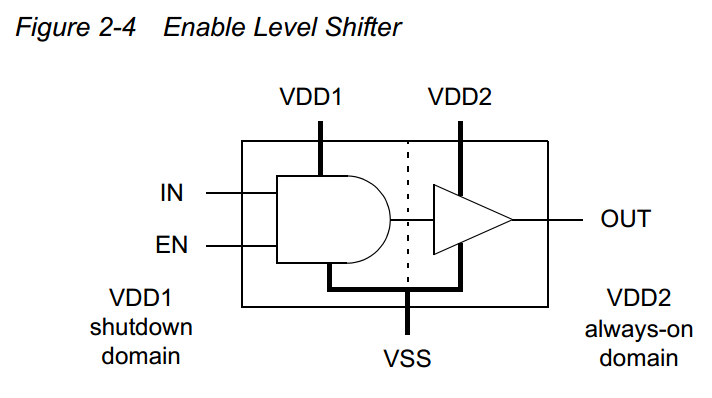

双向信号不能用隔离单元。可以同时执行电平转换和隔离功能的单元称为enable level-shifter单元。

使用隔离单元的原因:

当左边的Voltage Area处于关断状态,右边的Voltage Area却始终处于开启状态,左边的PD关断使电路输出悬空,处于未知状态X,则PMOS管和NMOS管可能同时导通,造成器件短路。

6)电源门控单元

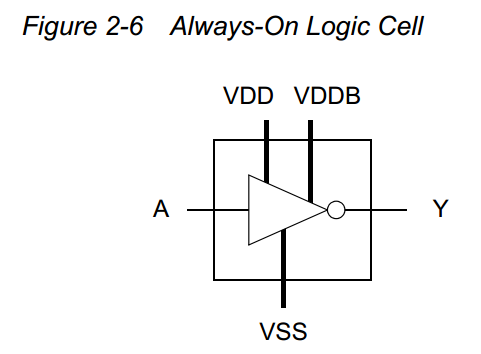

7)常开逻辑单元

作用:在shutdown电压域中需要一直保持active的单元,比如保持寄存器、隔离单元、retention 控制路径、isolation使能路径。比如,一个save或者restore信号穿过shutdown电压域并且需要加缓冲,那么就需要一个常开的buffer。与常规单元相比,它们多了一个备份电源。

8)保持寄存器单元

9)内部有生成电源的MACRO单元

10)将库转到PG Pin库格式

a)使用FRAM View

b)使用Tcl命令

c)使用针对低功耗库规格的命令

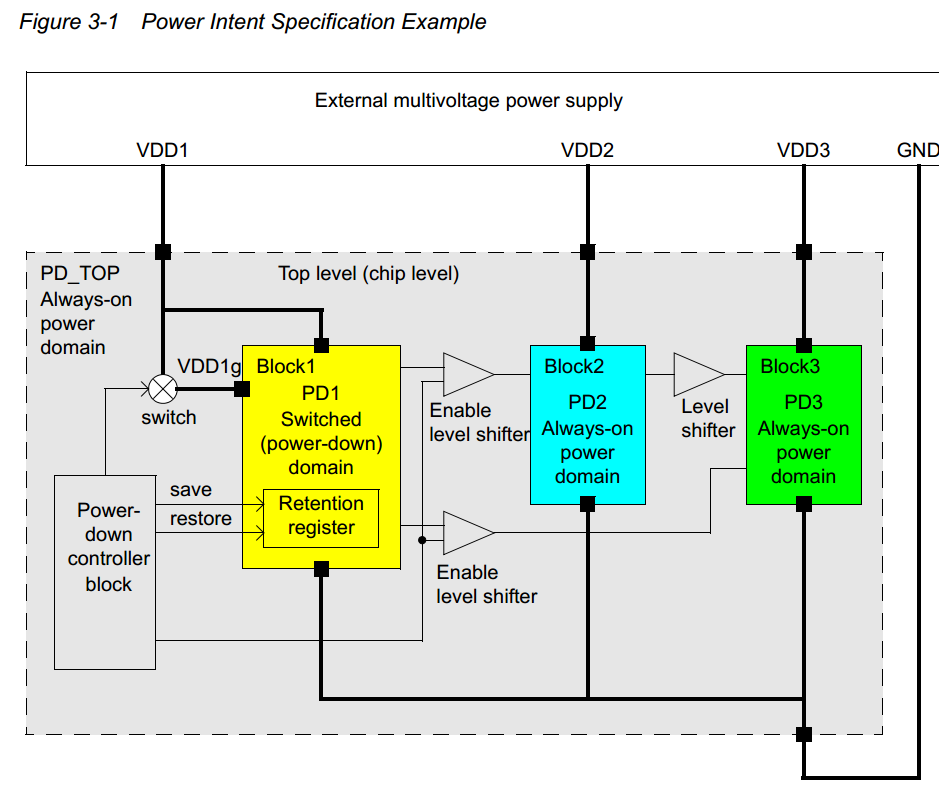

电源意图规范

统一电源格式(UPF)提供了一种统一的方式来指定整个设计过程中的电源实现意图,包括综合、物理实现和验证。这种一致性使得在给定设计中存在特定的低功耗特性时,更容易执行综合、仿真、逻辑等价性检查和设计验证

1)电源意图的概念

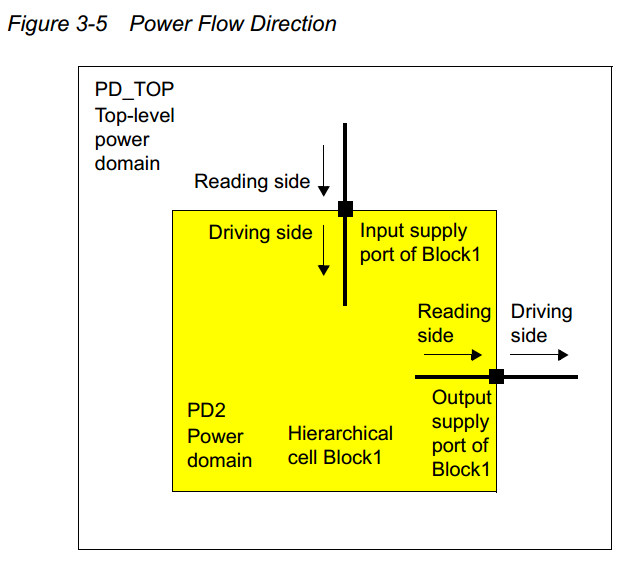

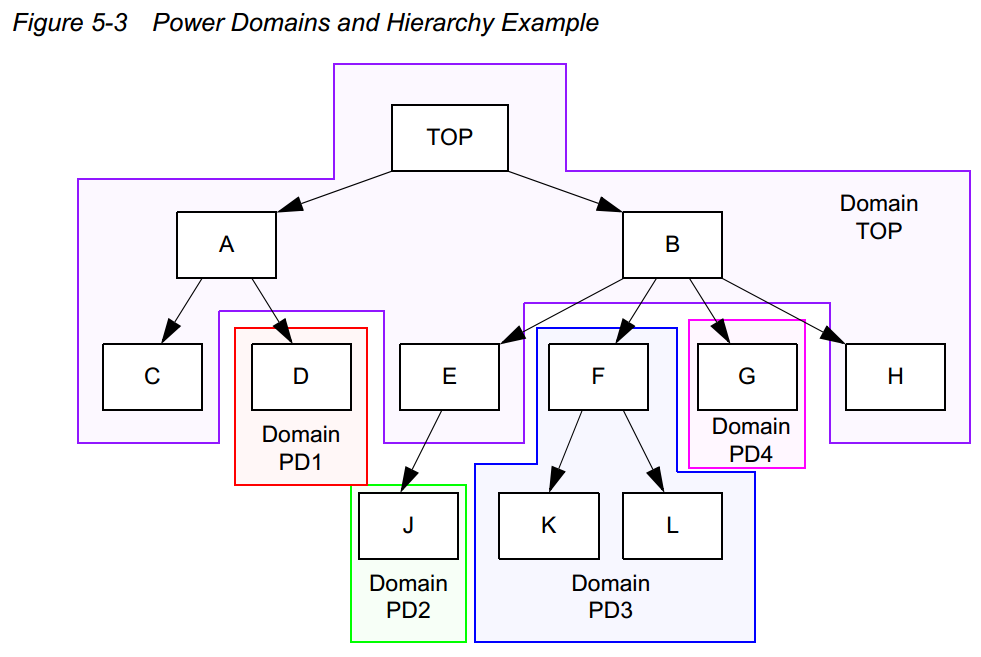

a)power domain:一块电压域中所有的单元共享同一组电源,通常被实现为物理芯片布局中的一个连续电压区域。每个电压域带一个scope属性和一个extent属性,scope是这个电压域被定义的逻辑层次,而extent则是属于这个电压域的逻辑元素集合。

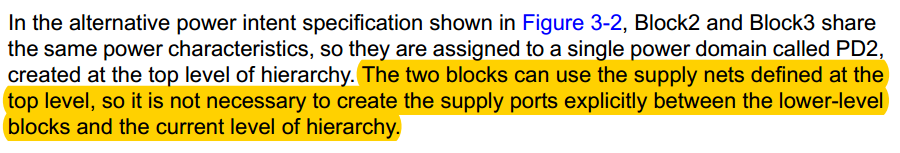

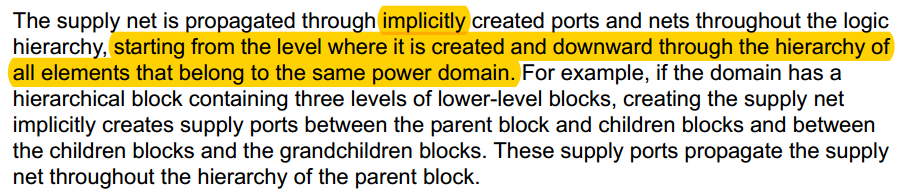

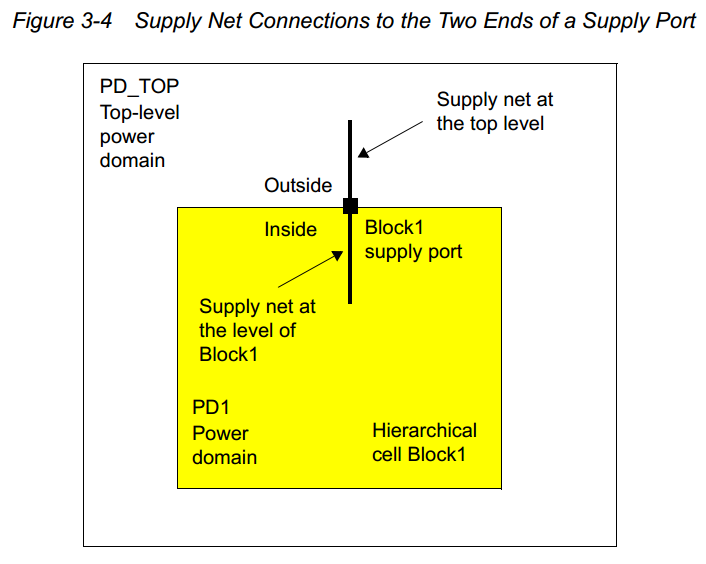

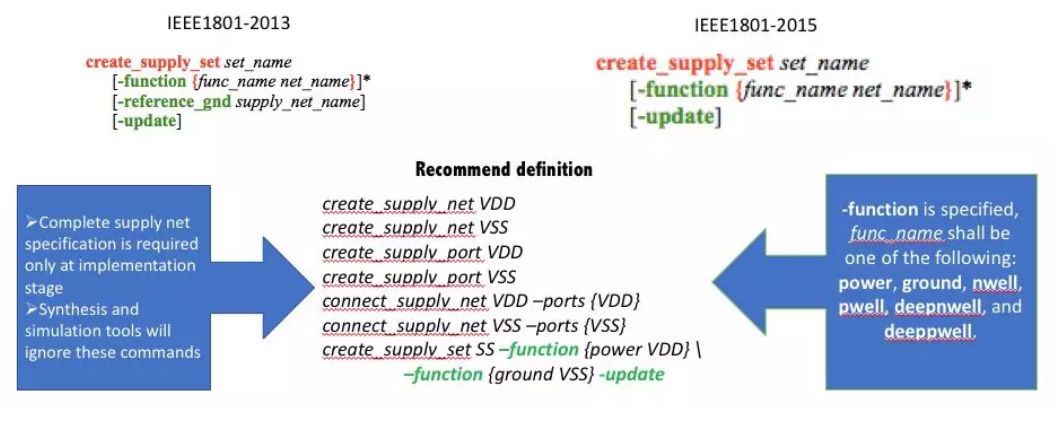

b)supply net和supply port:设计中的每个scope在它定义的层次级别上都有supply net和supply port。supply net是在给定的电源区域内承载电源电压或接地的导体,一个supply net穿过多个电压域被称为“reused”。supply port是设计层次结构的两个相邻层次之间、层次结构的父块和子块之间的电源连接点。从设计层次结构的一个层次跨越到下一个层次的supply net通过一个supply port。

c)supply set:它是supply net的一个抽象集合,supply set是domain-independent的,这意味着supply set中的电源地可以被它所定义的scope中的所有power domain共用。

d)supply set handle :

e)power switch:是一个针对于supply net开关电源的器件。一个switch有一个输入的supply net,和一个可以被开启或者关闭的输出的supply net,以及至少一个输入信号控制开关。

f)level shifter:电平移位器将信号从第一个域的电压摆幅转换为第二个域的电压摆幅。

g)isolation cell:电平移位器在电压域关闭期间生成一个已知的逻辑值。

h)retention registers:在具有电源开关的电源域中,在关机期间必须保留数据的任何寄存器都必须实现为保留寄存器。保留寄存器有一个单独的、始终在线的供应网络,有时称为备份供电,它在域的主供电关闭时保持保留寄存器中的数据稳定。

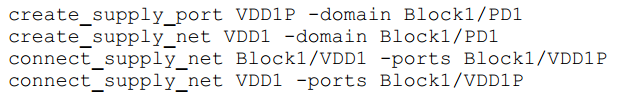

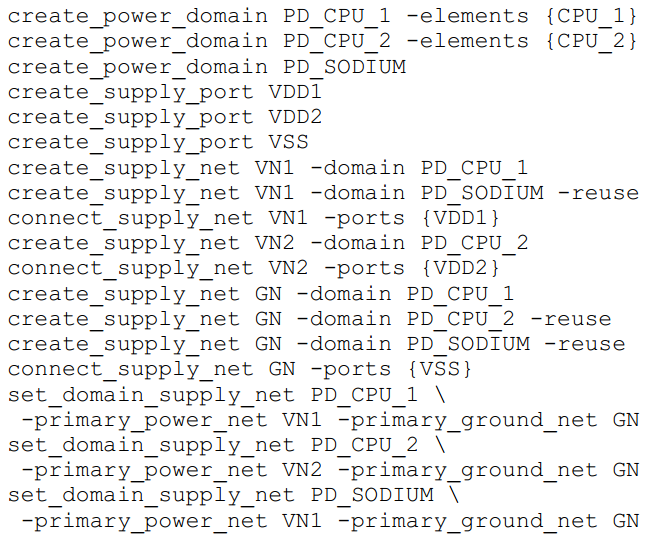

示例1:

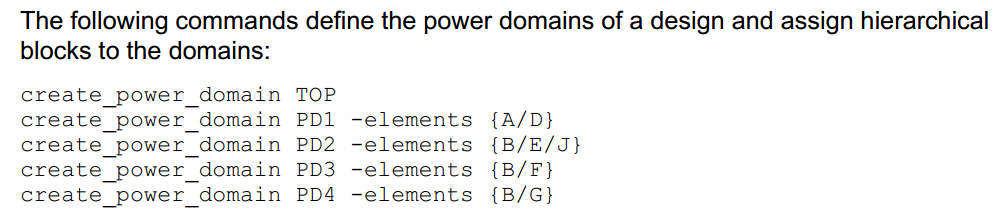

创建电压域:

访问某个电压域、电压端口、电压网络的方法:

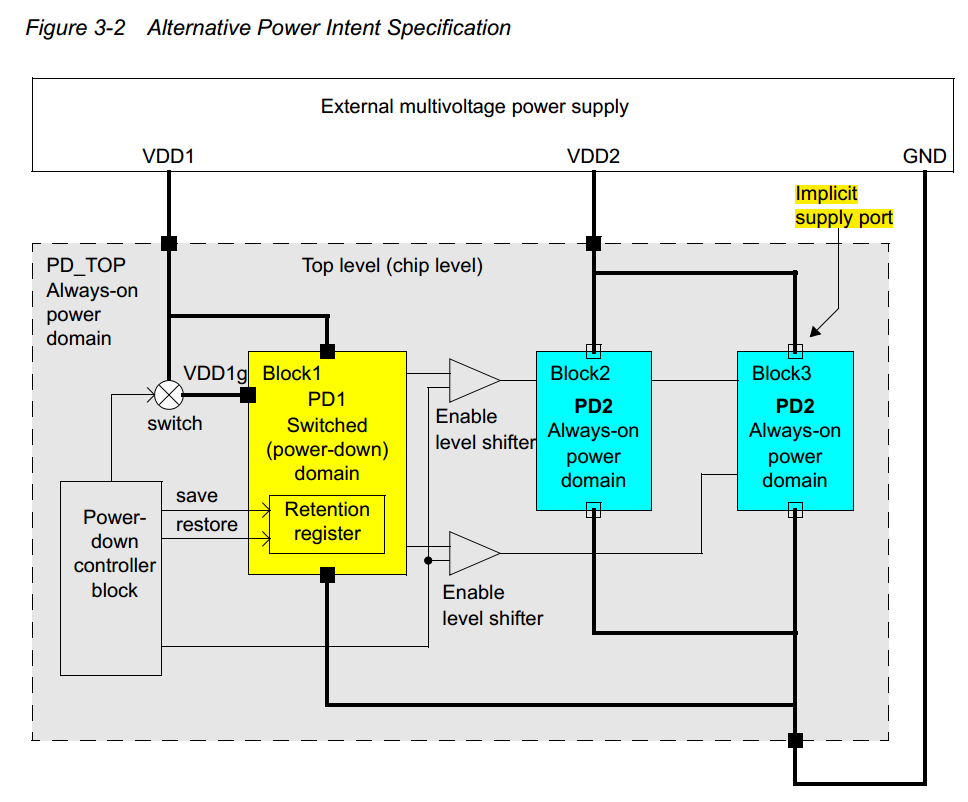

示例2:

创建电压域:

Synopsys 多电压流程

power-related cells 是在综合时加入的,而power switch则是在PR时加入的

3)UPF Commands Supported by Synopsys Tools

a)Basic Power Network Commands

基本电源命令定义设计的电压域和每个域的电源端口、电源网络和电源开关。

-create_power_domain

-create_supply_port

-create_supply_net

-connect_supply_net

电源端口在两端只能连接一次,VCS和Formality对power流动的方向施加限制。

-set_domain_supply_net

The set_domain_supply_net command specifies the primary power net and primary ground net for an existing power domain. They are the default power nets connected to the logic elements (or inferred cells) of the power domain. At the gate level, the power and ground pins of inferred gates are connected to the primary power and ground nets unless specified otherwise by the connect_supply_net, set_retention, or set_isolation command.

指定primary power net 和 primary groud net,它们是逻辑单元的power pin和ground pin默认连接的nets。

-create_power_switch

b)Level Shifter Commands

-set_level_shifter

c)Power Supply Checking, Reporting, and Collection Commands

生成报表

-report_power_domains

-report_supply_nets

-report_supply_ports

-get_power_domains

-get_supply_nets

-get_supply_ports

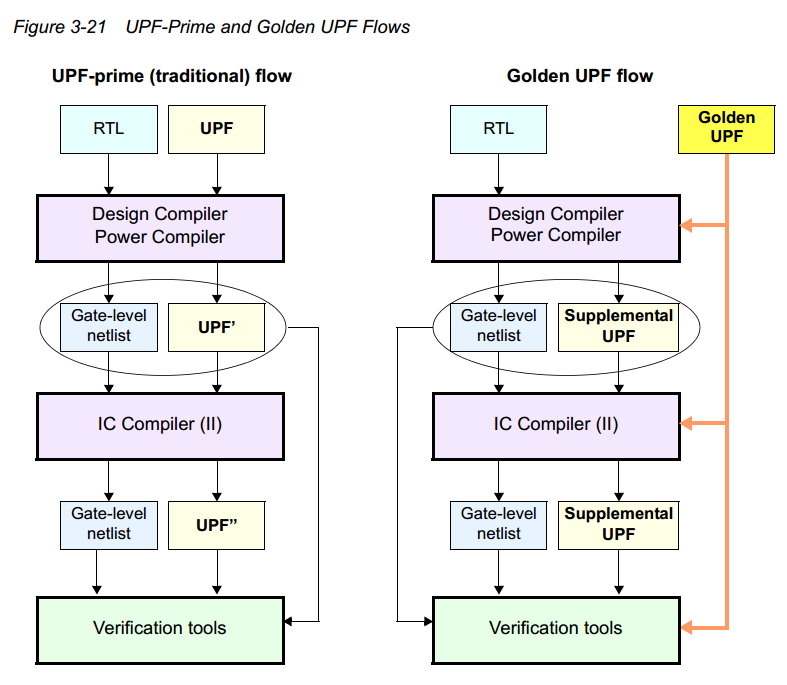

d)Golden UPF flow

4)Supply set

一个supply set 包含某个instance 或power domain 所有的supply nets

4、UPF脚本示例

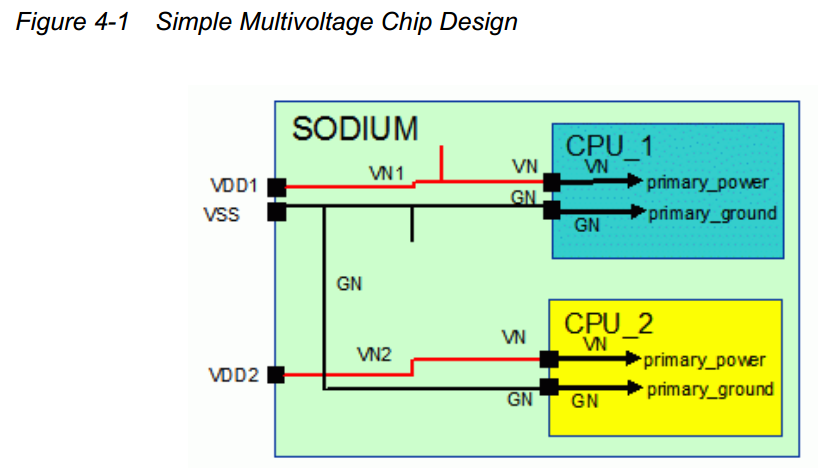

1)双电压域

可以看到,上述例子并没有显式地去创建CPU_1的电源端口VN和GN以及CPU_2的电源端口VN和GN,因为供电网络PDSODIUM/VN1和PD_CPU_1/VN1都是在SODIUM这个scope中创建的,因此它们会自动创建端口进行跨层次连接。还少一个 create_supply_net VN2 -domain PD_SODIUM -reuse

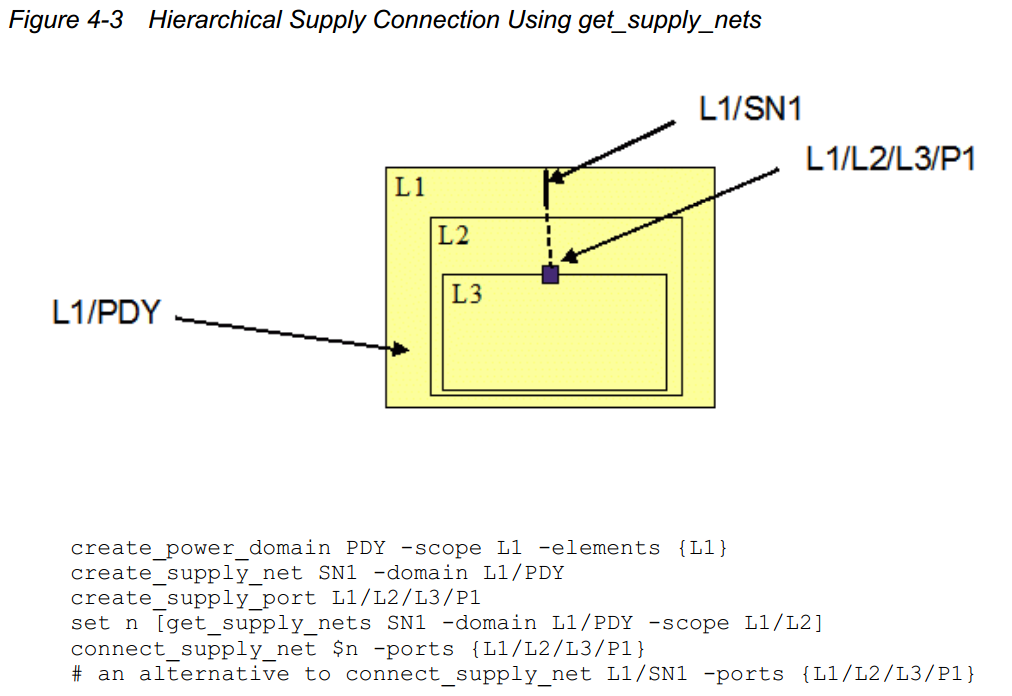

2)Hierarchy and the get_supply_nets Command

5、特定工具的使用建议

1)Logic Synthesis Using Design Compiler

DC可以基于UPF命令和UPF指定的电源状态自动插入level shifters,isolation cells,rentention registers。

DC的输入文件包括RTL和用户编写的UPF,综合之后会生成一个新的UPF,新的UPF包含了一些综合过程中与电源管理单元相关的连接,如level shifters,isolation cells,rentention registers。

基本流程:

a)电压域和层次

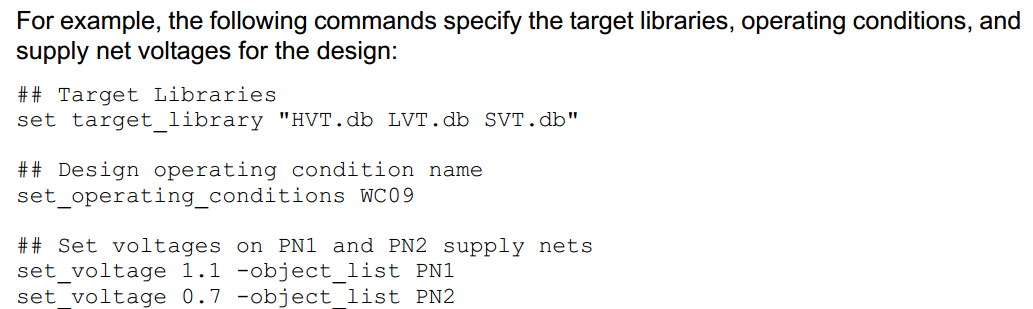

2)指定工作电压

3)编译

在运行编译之前,将auto_insert_level_shifters_on_clocks变量设置为时钟名称列表或全部,这样编译器就会给时钟也插level shifters

通常Isolation cell和Level Shifter一起连用,AND和OR门都可以组成一个isolation cell。Isolation可以放在input端,output端或者第三方Voltage Area中,但是考虑到power-on rail的走线,isolation cell自身的功耗,一般还是放在input端比较好,因为放在input端不需要always-on的power。

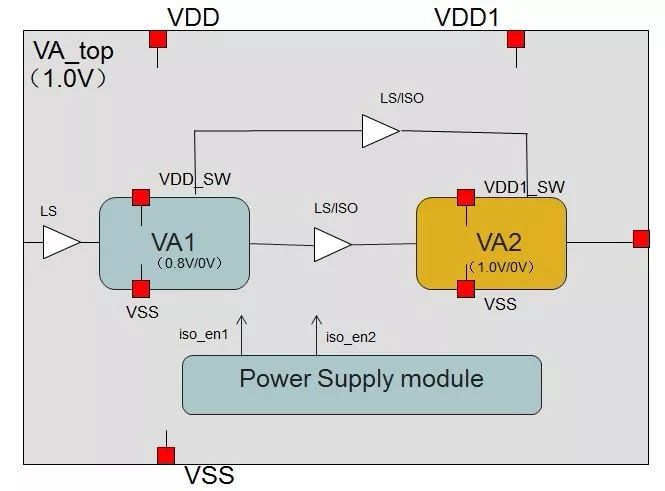

结合图表来看UPF文件描述:

set_isolation iso_va1 指定isolation cell的添加rule,相当于前缀名称

-domain VA1 指定添加isolation cell的voltage area

-applies_to output 指定isolation cell在voltage area的input还是output

-diff_supply_only true 指定cell port上是否允许有其他supply

-loacation parent 指定level shifter的放置位置,parent代表放在driver pin的父module

-isolation_signal ip/iso_en1 指定isolation cell的isolation 控制信号

-calmp_value 1 指定isolation cell的输出值

set_isolation iso_va2

-domain VA2

-applies_to output

-loacation parent

-sink ss_pd1

-isolation_signal iP/iso_en2

-clamp_value1

浙公网安备 33010602011771号

浙公网安备 33010602011771号