SOC设计中的时钟结构

PLL结构

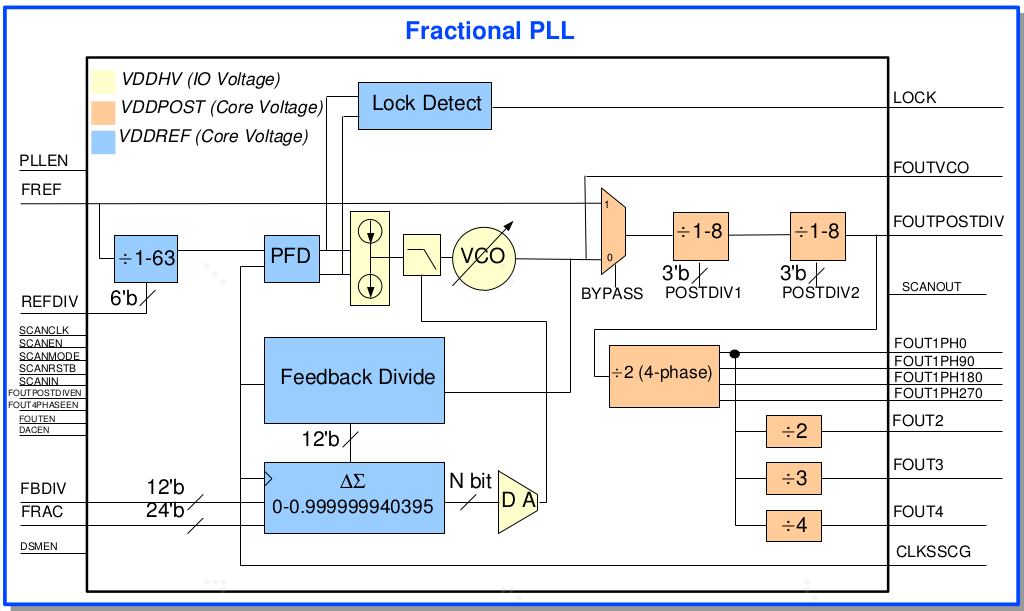

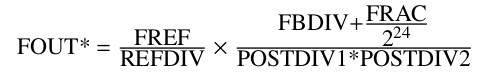

分数PLL结构

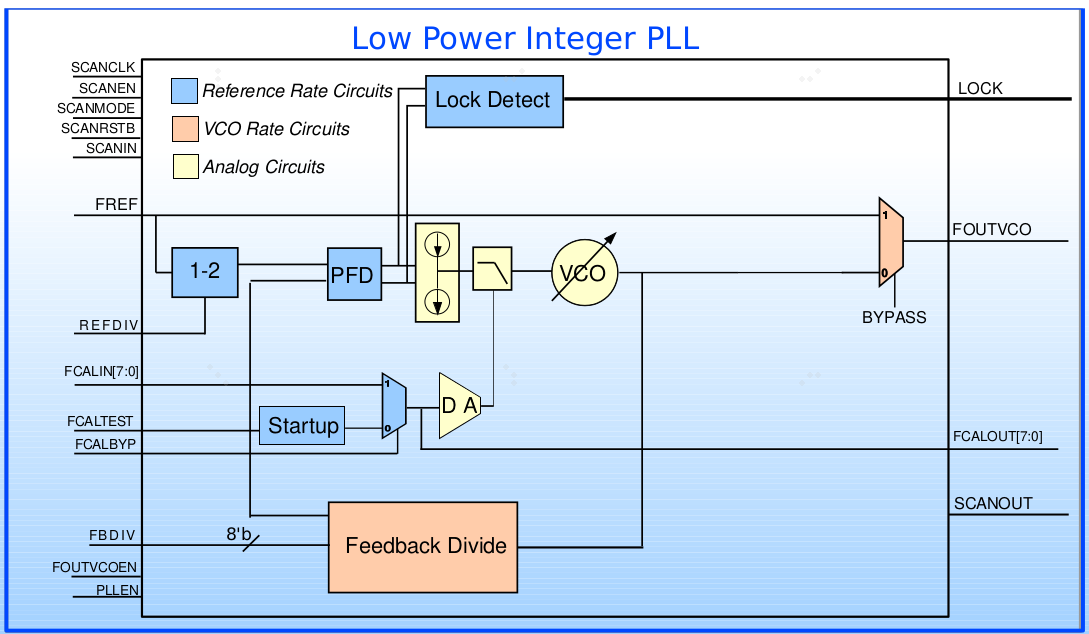

整数PLL结构

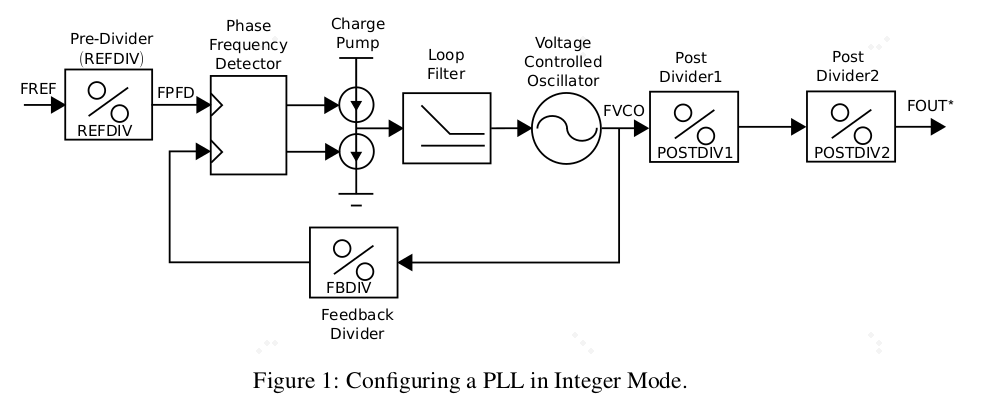

这是一个通用方程式,请参考具体的数据表。

FOUT 是 PLL 输出端口的前缀。 重要的是确保 FBDIV 在 PLL 启用时被编程为有效设置。 某些 PLL 可能会将 FBDIV=0 映射到更高的值,这可能会阻止 PLL 锁定。

**注意:如果 PLL 具有多个串联的后分频器,则在启用第二个后分频器之前应最大化第一个后分频器的值。

例如, 4分频:

• 推荐:设置POSTDIV1=4,POSTDIV2=1

• 不推荐但可以接受:设置 POSTDIV1=2、POSTDIV2=2

• 不可接受:POSTDIV1=1,POSTDIV2=4

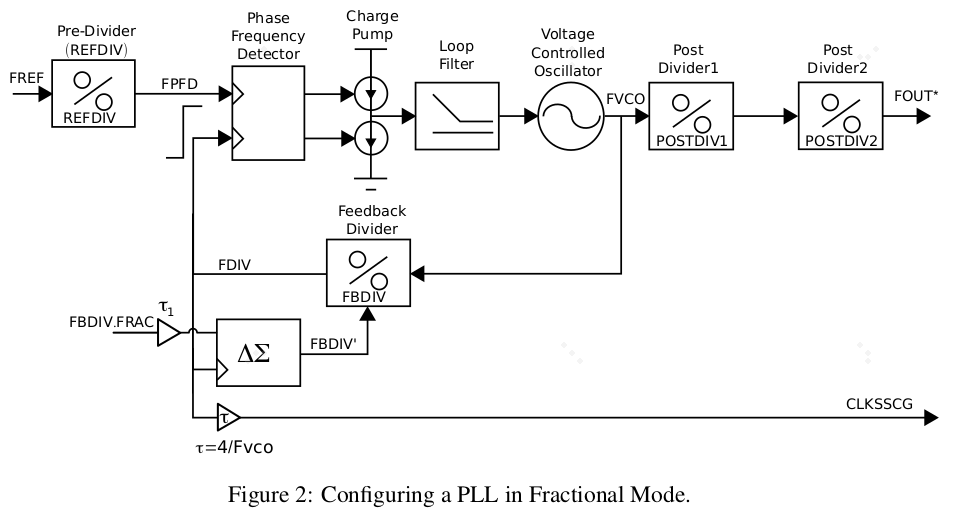

这是一个通用方程式,请参考具体的数据表。

**注意:如果 PLL 具有多个串联的后分频器,则在启用第二个后分频器之前应最大化第一个后分频器的值。

例如,4分频:

• 推荐:设置POSTDIV1=4,POSTDIV2=1

• 不推荐但可以接受:设置 POSTDIV1=2、POSTDIV2=2

• 不可接受:POSTDIV1=1,POSTDIV2=4

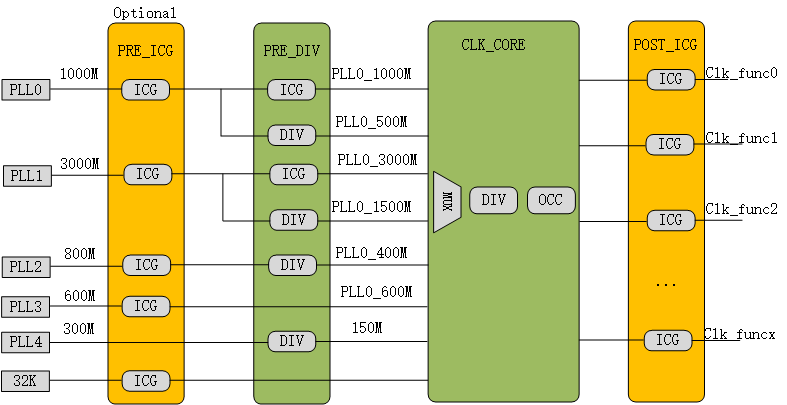

时钟结构

时钟结构

PRE_ICG:源头时钟进来后第一级gating

PRE_DIV:源头时钟做前处理(包括gate或者div),产生root时钟给后面选择。其中DIV表示源头时钟做分频,产生不同频率的root时钟供后面选择;ICG表示源头时钟不分频,产生gating后的root时钟供后面选择。

CLK_CORE:主要功能产生模块,其中MUX(cgm_mux2_free)为无毛刺时钟切换,DIV为时钟分频器。ICG(cgm_gate)为门控时钟对,OCC用于DFT。

POST_ICG:输出时钟最后一级gating.

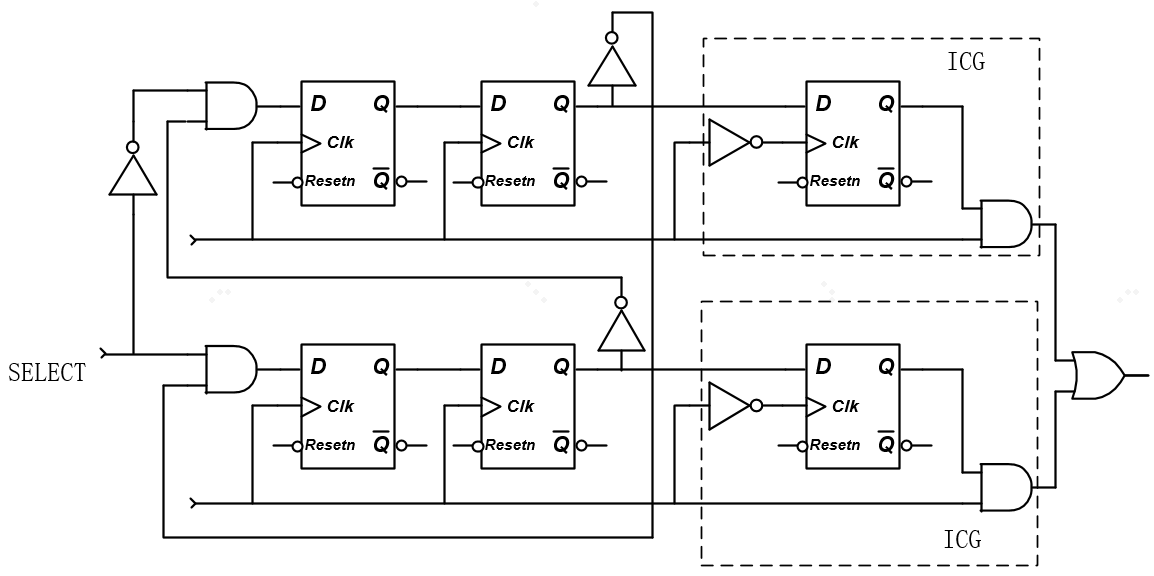

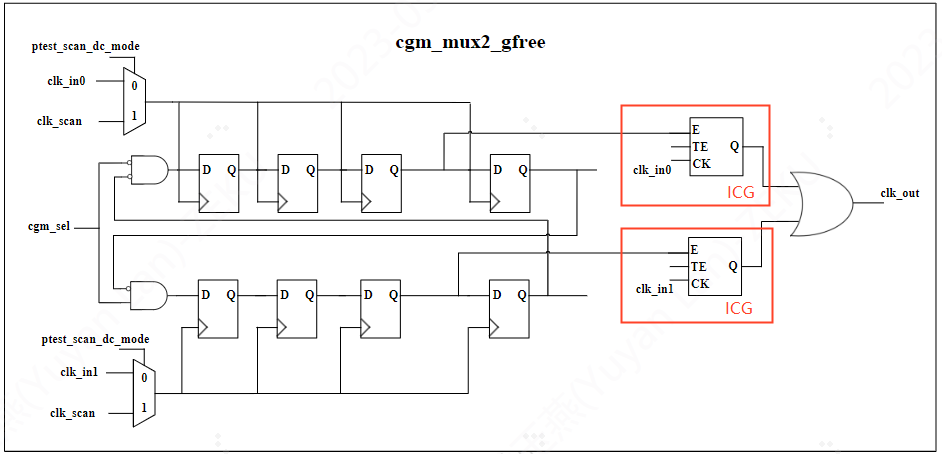

glitch free mux

glitch free clk mux

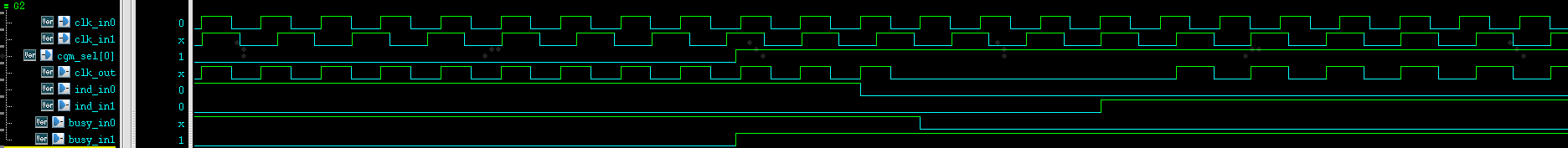

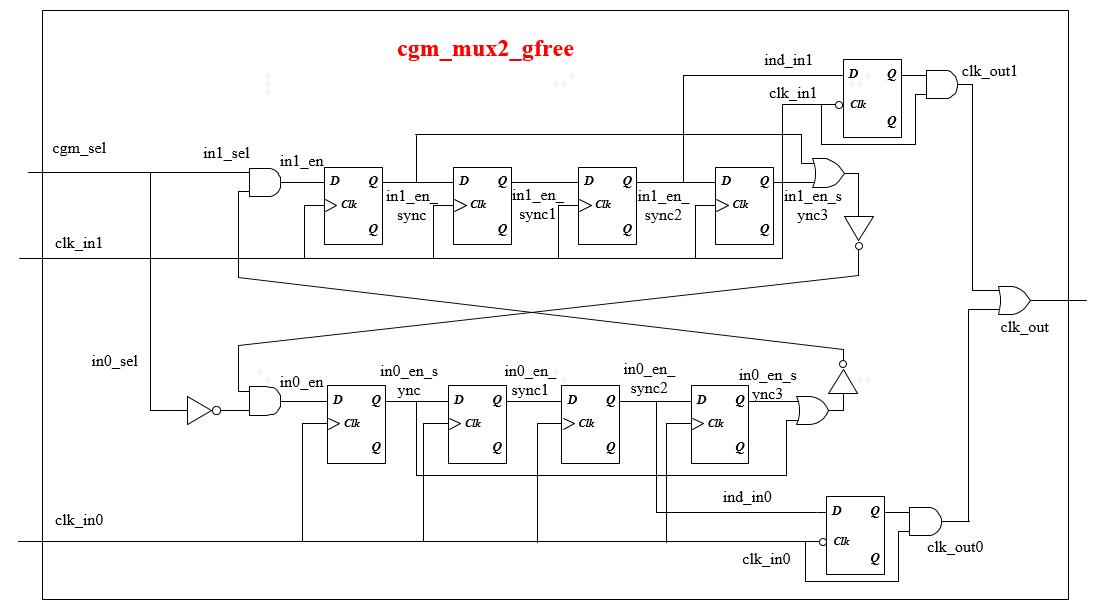

clk_in0转换为clk_in1,cgm_sel拉高后,先经过clk_in0同步三拍,clk_out保持clk_in0三拍后拉低,再经过clk_in0的三拍同步之后,clk_out切换到clk_in1。切换时,两路时钟都需要打开,否则无法切换。

当cgm_sel由0变为1时,in0_en先变为0,经过clk_in0同步后in0_en_sync2变为0,clk_out变为0,输出时钟被关断一段时间,in0_en_sync3变为0,经过取反以后为1和cgm_sel做与以后,in1_en变为1,in1_en经过clk_in1同步后,in1_en_sync2变为1,时钟被切换为clk_out1

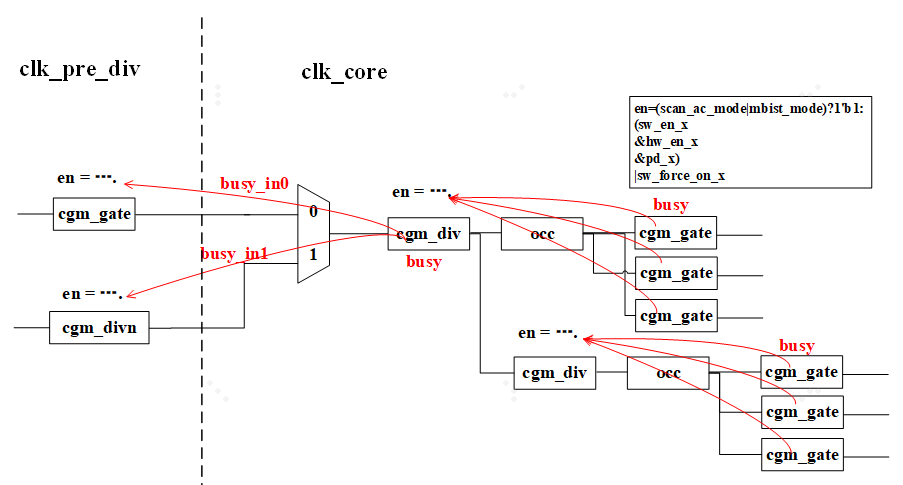

auto clk gate

auto clk gate

clock cell 模块(gating/div/mux)都有busy输出,busy为高电平表示当前模块在active状态,clk_in时钟不可以关掉,busy为低电平时表示当前模块为idle状态,clk_in时钟可以关掉,降低功耗。

首先利用寄存器配置各个模块的软件enable或者force enable 信号,例如dma的enable信号:

assign en_dma_dsp = (sw_en_dma_dsp) | sw_force_en_dma_dsp | dma_func_n_clk_en;

利用后级模块的enable信号,对应xgm_gate的cgm_en输入信号,利用cgm_en输入信号生成对应模块的cgm_busy信号,然后将后级所有模块的busy做与操作反馈给前级模块的en的信号。当后级所有模块都不工作时,busy为低电平,关闭前级模块; 当后级有任何一个模块工作时,busy 为高电平,需要打开前级模块。 特别地,图中的hw_en_x表示来自ip或bus的busy状态。以cgm_en→cgm_busy→cgm_en的形式一级一级由后级向前级模块传递。

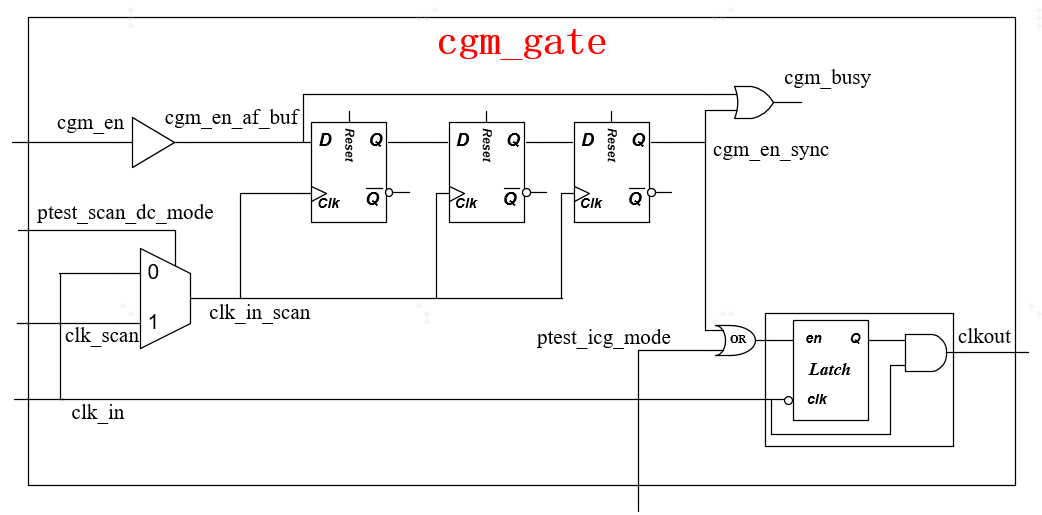

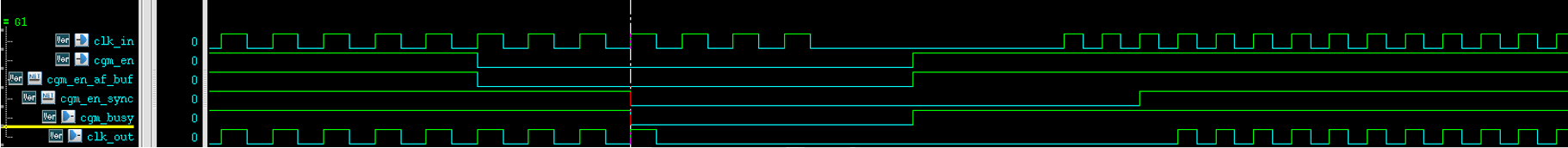

cgm_gate

cgm_gate

cgm_en在模块内部做了三级同步,晚三拍生效

div

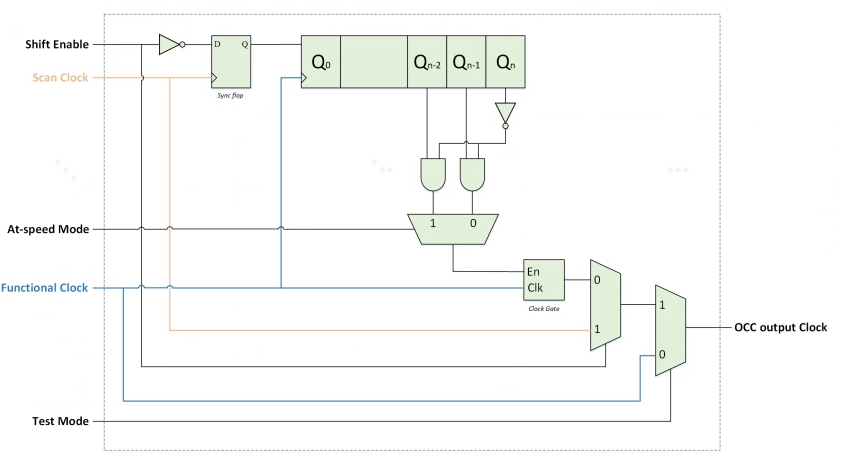

occ

On-chip Clock Controllers (OCC) 也称为扫描时钟控制器(Scan Clock Controllers ,SCC)。OCC是插入SOC的逻辑,用于在ATE(自动测试设备)上进行硅测试期间控制时钟。由于at-speed testing 需要捕获模式 capture mode下的两个时钟脉冲,其频率等于function时钟频率,因此在没有OCC的情况下,我们需要通过I/O pad提供这些高速脉冲。但这些pad在其所能支持的最大频率方面有局限性;另一方面,OCC使用内部PLL时钟来生成用于测试的时钟脉冲。在stuck-at testing期间,OCC确保在捕获阶段只生成一个时钟脉冲。类似地,在at-speed testing期间,OCC确保在捕获阶段生成两个时钟脉冲,其频率等于功能时钟的频率。

因此, scan friendly设计中的所有测试时钟都通过OCC进行route,OCC控制 scan mode (both in stuck-at and at-speed testing)下的时钟操作,并在功能模式下bypass功能时钟。下面是一个非常基本的OCC设计,目的是判断OCC是如何工作的。实际OCC实现会更先进,对时钟故障的鲁棒性更强。

图1:基本OCC结构示意图(具有n位移位寄存器)

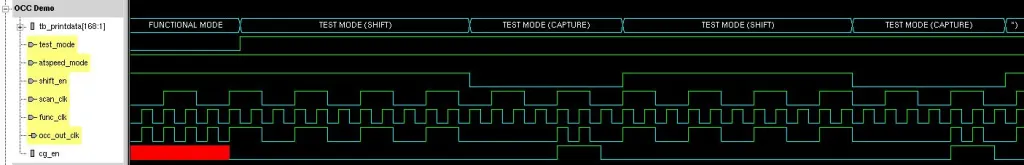

当电路处于 functional mode (Test Mode = 0)时,OCC控制系统bypass functional clock (参见图1)。但在移位阶段(Shift Enable =1),扫描时钟在OCC的输出端传播。在捕获阶段capture phase (Shift Enable = 0),移位寄存器开始移位“1”并启用时钟门,以允许单脉冲或双脉冲,具体取决于测试类型。OCC在stuck-at testing (At-speed Mode = 0)中产生一个时钟脉冲,在at-speed testing (At-speed Mode = 1)中产生两个时钟脉冲。该OCC(具有5位移位寄存器)在at-speed testing中的行为如图2所示。两个捕获脉冲出现在functional clock的5个正沿之后(因为我们使用的是5位移位寄存器)。

注:一旦Shift Enable被断言为低,n位移位寄存器就根据 functional clock的正沿数量来决定延迟,之后 functional clock在OCC的输出端传播。

module occ #(

parameter SHIFT_REG_BITS = 5)(

input logic test_mode,

input logic atspeed_mode,

input logic shift_en,

input logic scan_clk,

input logic func_clk,

output logic occ_out_clk

)

logic cg_en;

logic cg_out_clk;

logic sync_flop;

logic [SHIFT_REG_BITS-1:0]shift_reg;

always @(func_clk or cg_en) begin

cg_out_clk = func_clk&cg_en;

end

always_ff @(posedge scan_clk) begin

sync_flop <= ~shift_en;

end

always_ff @(posedge func_clk) begin

shift_reg <= shift_reg << 1;

shift_reg[0] <= sync_flop;

end

assign occ_out_clk = test_mode ? (shift_en ? scan_clk : cg_out_clk) : func_clk;

assign cg_en = atspeed_mode ? (~shift_reg[SHIFT_REG_BITS-1] & shift_reg[SHIFT_REG_BITS-3]) :

(~shift_reg[SHIFT_REG_BITS-1] & shift_reg[SHIFT_REG_BITS-2]);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号