AXI DMA寄存器描述

通用寄存器

DMAC_CfgReg

DMAC_CfgReg: dmac全局配置寄存器,该寄存器用于使能DW_axi_dmac,必须在任何通道活动开始之前执行此操作。该寄存器还包含全局中断使能。

bit[1]:INT_ENR该位用于全局启用中断生成。0:表示关闭DW_axi_dmac中断。1:表示打开DW_axi_dmac中断逻辑。

bit[0]: DMAC_EN,此位用于使能DW_axi_dmac。0: DW_axi_dmac禁用1: DW_axi_dmac启用

注意:如果此位DMAC_EN位在任何通道仍处于活动状态时被清除,则此位仍然返回1,表示仍有通道处于活动状态,直到DW_axi_dmac硬件终止所有通道上的所有活动,此时此位返回0(0)。

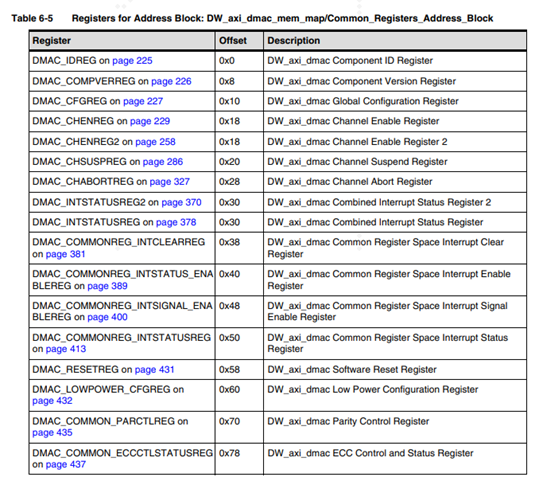

DMAC_ChEnReg

- Exists: DMAX_NUM_CHANNELS <= 8

- DMAC_ChEnReg:dmac Channel Enable Register,这是DW_axi_dmac通道使能寄存器。如果软件想要建立一个新的通道,它可以读取这个寄存器来找出哪些通道目前是不活动的,然后用要求的优先级启用一个不活动的通道。

- 当DW_axi_dmac全局使能位(DMAC_CfgReg.DMAC_EN)为0时,DMAC_ChEnReg的所有位都被清除为0。当DMAC_CfgReg.DMAC_EN为0,对DMAC_ChEnReg寄存器的写操作被忽略,而读操作总是回读0。

- 仅当相应的通道写使能位DMAC_ChEnReg.CH_EN_WE在同一个从接口写传输上被断言有效时,通道使能位DMAC_ChEnReg.CH_EN才能被写入。

- 例如,写入十六进制 XXXX01X1 会将 1 写入 DMAC_ChEnReg [0],而 DMAC_ChEnReg [7:1] 保持不变。 写入十六进制 XXXX00XX 会使 DMAC_ChEnReg [7:0] 保持不变。

- 也即是说,只有DMAC_ChEnReg.CHx_EN_WE为1时或者写入DMAC_ChEnReg.CHx_EN时,DMAC_ChEnReg.CHx_EN_WE同时写入1,DMAC_ChEnReg.CHx_EN才能被写入。

- 仅当相应的通道写使能位DMAC_ChEnReg. CH_SUSP_WE在同一个从接口写传输上断言时,DMAC_ChEnReg.CH_SUSP通道暂停位才能被写入。

- 例如,写入十六进制 01X1XXXX 会将 1 写入 DMAC_ChEnReg [16],而 DMAC_ChEnReg [23:17] 保持不变。 写入十六进制 00XXXXXX 会使 DMAC_ChEnReg [23:16] 保持不变。

- 也即是说,只有DMAC_ChEnReg.CH_SUSP_WE为1时或者写入DMAC_ChEnReg.CHx_SUSP时,DMAC_ChEnReg.CH_SUSP_WE同时写入1,DMAC_ChEnReg.CH_SUSP才能被写入。

- 仅当相应的通道写启用位DMAC_ChEnReg.CH_ABORT_WE在同一个从接口写传输上断言时,通道中止位DMAC_ChEnReg.CH_ABORT才能被写入。

- 也即是说,只有DMAC_ChEnReg.CHx_ABORT_WE为1时或者写入DMAC_ChEnReg.CH_ABORT时,DMAC_ChEnReg.CH_ABORT_WE同时写入1,DMAC_ChEnReg.CH_ABORT才能被写入。

- CHx_ABORT:通道 x 中止请求。 软件将该位设置为 1 以请求通道中止。 如果此位设置为 1,则 DW_axi_dmac 会立即禁用该通道。

- 中止通道可能会导致 AXI 协议违规,因为 DW_axi_dmac 无法确保在主接口上启动的所有 AXI 传输都已完成。

- 不建议中止通道,并且仅应在特定通道因无响应而挂起的情况下使用,相应的 AXI 从接口和软件想要在不复位整个 DW_axi_dmac 的情况下禁用通道。 建议首先尝试禁用通道,然后仅选择通道中止。

- ■ 0:无通道中止请求。 ■ 1:请求通道中止。 一旦通道中止(当它将 CHx_Status.CH_ABORTED 位设置为 1 时),DW_axi_dmac 会将此位清除为 0。

- ■ 0x1 (ENABLE_CHx_ABORT):通道x 中止请求 ■ 0x0 (DISABLE_CHx_ABORT):没有请求通道 x 中止

- CHx_SUSP:Channel-x 暂停请求。 软件将该位设置为 1 以请求通道暂停。 如果这 位设置为 1,DW_axi_dmac 将优雅地暂停来自源的所有 DMA 数据传输,直到该位被清除。不保证当前 dma 事务将完成。

- 该位还可与 CHx_Status.CH_SUSPENDED 结合使用,以在不丢失任何数据的情况下完全禁用通道。 在这种情况下,软件首先将 CHx_SUSP 位设置为 1 并轮询 CHx_Status.CH_SUSPENDED 直到它设置为 1。然后软件可以将 CHx_EN 位清零以禁用通道。

- ■ 0:无通道暂停请求。 ■ 1:请求通道暂停。 软件可以将 CHx_SUSP 位清零,DW_axi_dmac 设置 CH8_Status.CH_SUSPENDED 位为 1 后,退出通道挂起模式。 注意:当通道被禁用时,CH_SUSP 被清除。

- ■ 0x1 (ENABLE_CHx_SUSP):请求暂停通道-x ■ 0x0 (DISABLE_CHx_SUSP):无通道暂停请求

- CHx_EN:该位用于启用 DW_axi_dmac Channel-x。

- ■ 0:DW_axi_dmac 通道 x 被禁用 ■ 1:启用 DW_axi_dmac 通道x在到目标的 DMA 传输的最后一个 AMBA 传输完成后,“DMAC_ChEnReg.CHx_EN”位由硬件自动清除以禁用通道。

- 因此,软件可以轮询此位以确定此通道何时可用于新的 DMA 传输。 值: ■ 0x1 (ENABLE_CHx):DW_axi_dmac:启用通道x ■ 0x0 (DISABLE_CHx):DW_axi_dmac:通道 x 已禁用

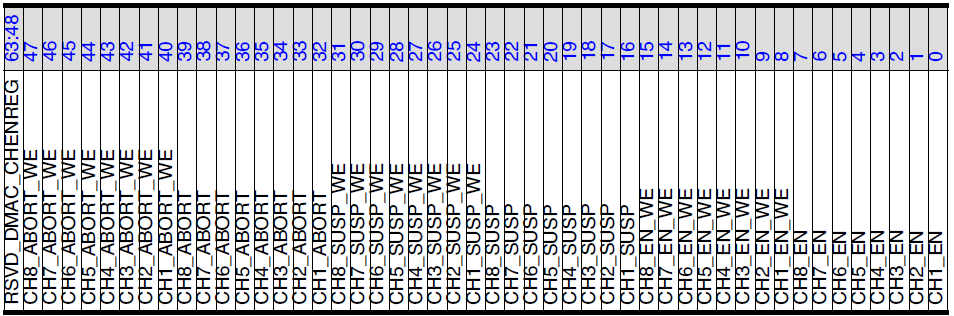

DMAC_ChEnReg2

Exists: DMAX_NUM_CHANNELS > 8

DW_axi_dmac 通道启用寄存器。 如果软件想要建立一个新通道,它可以读取该寄存器以找出当前哪些通道处于非活动状态,然后启用具有所需优先级的非活动通道。

当 DW_axi_dmac 全局使能位 (DMAC_CfgReg.DMAC_EN) 为 0 时,该寄存器的所有位都清零。当 DMAC_CfgReg.DMAC_EN 为 0 时,忽略对 DMAC_ChEnReg 寄存器的写入,读取始终读回 0。

通道使能位 DMAC_ChEnReg.CH_EN 仅在相应的通道写使能位 DMAC_ChEnReg.CH_EN_WE 在同一从接口写传输上被置位时才被写入。

例如,写入十六进制 0000_XXXX_0001_XXX1 会将 1 写入 DMAC_ChEnReg [0],而 DMAC_ChEnReg [15:1] 和 DMAC_ChEnReg [47:32] 保持不变。

. 写十六进制 0000_XXXX_0000_XXXX 使 DMAC_ChEnReg [15:0] 和 DMAC_ChEnReg [47:32] 保持不变。

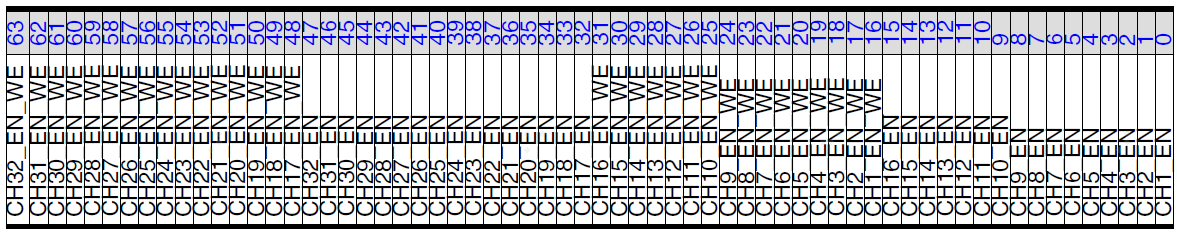

DMAC_ChSuspReg

Exists: DMAX_NUM_CHANNELS > 8

DW_axi_dmac 通道暂停寄存器。 通道暂停位, DMAC_ChSuspReg.CH_SUSP,仅当相应的通道写使能位 DMAC_ChSuspReg.CH_SUSP_WE 在同一从接口写传输上被断言时才被写入。

例如,写入十六进制 0000_XXXX_0001_XXX1 会将 1 写入 DMAC_ChSuspReg [0],而 DMAC_ChSuspReg [15:1] 和 DMAC_ChSuspReg [47:32] 保持不变。

写十六进制 0000_XXXX_0000_XXXX 使 DMAC_ChSuspReg [15:0] 和 DMAC_ChSuspReg [47:32] 保持不变.

CHx_SUSP:Channel-x请求暂停。软件将此位设置为1以请求通道暂停。如果该位设置为1,DW_axi_dmac将优雅地挂起来自源的所有DMA数据传输,直到清除该位为止。不能保证当前的dma传输将会完成。

该位也可以与CHx_Status.CH_SUSPENDED一起使用以完全禁用通道而不丢失任何数据。在这种情况下,软件首先将CHx_SUSP位设置为1,然后轮询CHx_Status.CH_SUSPENDED直到设置为1。然后软件可以清除CHx_EN位到0以禁用通道。

0:无通道挂起请求。1:请求通道暂停。当DW_axi_dmac设置CHx_Status.CH_SUSPENDED位为1后,软件可以将CHx_SUSP位清零,退出通道暂停模式。备注:禁用通道时清除CH SUSP。

CHx_SUSP_WE:该位用作通道 x暂停位的写使能。 该寄存器位的回读值始终为 0。 值: ■ 0x1 (ENABLE_WR_CHx_SUSP):允许写入相应的 CHx_SUSP 位 ■ 0x0 (DISABLE_WR_CHx_SUSP):禁止写入 CHx_SUSP 位

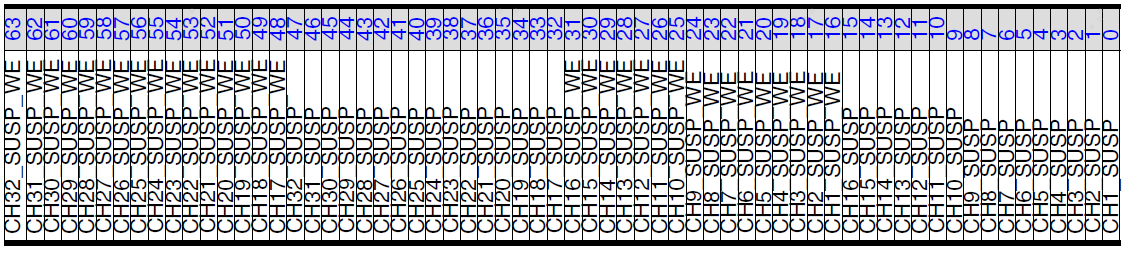

DMAC_ChAbortReg

DW_axi_dmac 通道中止寄存器。 仅当相应的通道写使能位 DMAC_ChAbortReg.CH_ABORT_WE 在同一从接口写传输上被置位时,通道中止位 DMAC_ChAbortReg.CH_ABORT 才会被写入。

CHx_ABORT:通道中止请求。软件将此位设置为1以请求通道中止。如果该位设置为1,DW_axi_dmac将立即禁用通道。中止通道可能会导致违反AXI协议,因为DW_axi_dmac不能确保在主机接口上发起的所有AXI传输都已完成。

不建议中止通道,并且只应该在以下情况下使用:由于相应的AXI从接口没有响应而导致特定通道挂起,软件希望在不复位整个DW_axi_dmac的情况下禁用该通道。建议先尝试通道禁用,然后只选择通道中止。

.0:无通道中止请求。•1:请求通道中止。

CHx_ABORT_WE:该位用于写使能 Channel-x Abort 位。 该寄存器位的回读值始终为 0。 值: ■ 0x1 (ENABLE_WR_CHx_ABORT):启用写入 CHx_ABORT 位 ■ 0x0 (DISABLE_WR_CHx_ABORT):禁止写入 CHx_ABORT 位

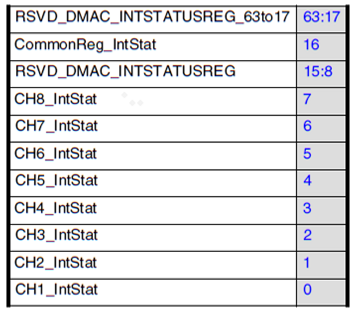

DMAC_INTSTATUREG2

DW_axi_dmac 组合中断状态寄存器 2

DMAC 中断状态寄存器捕获每个通道的组合通道中断和组合公共寄存器块中断。 如果 DMA 通道数大于 8,则存在该寄存器。Exists: DMAX_NUM_CHANNELS > 8

DMAC_INTSTATUREG

DW_axi_dmac 组合中断状态寄存器

DMAC 中断状态寄存器捕获每个通道的组合通道中断和组合公共寄存器块中断。 如果 DMA 通道数小于等于 8,则存在该寄存器。Exists: DMAX_NUM_CHANNELS <= 8

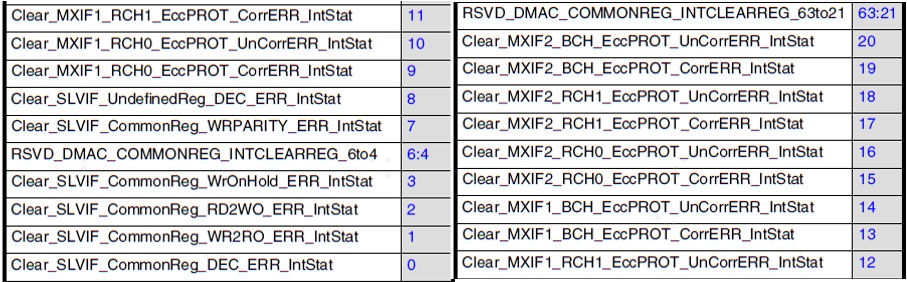

DMAC_COMMONREG_INTCLEARREG

DW_axi_dmac 公共寄存器空间中断清除寄存器 向特定字段写入 1 会清除 DMAC 通用寄存器中断状态寄存器 (DMAC_CommonReg_IntStatusReg) 中的相应字段。

- Clear_MXIF2_BCH_EccPROT_UnCorrERR_IntStat:bit20,AXI 主接口 2 写入响应通道 ECC 保护相关的不可纠正错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_BCH_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_BCH_EccPROT_UnCorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_BCH_EccPROT_UnCorrERR_IntStatinterrupt

- ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF2_BCH_EccPROT_CorrERR_IntStat:bit19,AXI 主接口 2 写入响应通道 ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_BCH_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_BCH_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_BCH_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF2_RCH1_EccPROT_UnCorrERR_IntStat:bit18,AXI 主接口 2 读取通道(其他控制信号)ECC 保护相关的不可纠正错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_RCH1_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_RCH1_EccPROT_UnCorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_RCH1_EccPROT_UnCorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF2_RCH1_EccPROT_CorrERR_IntStat:bit17,AXI 主接口 2 读取通道(其他控制信号)ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_RCH1_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_RCH1_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_RCH1_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF2_RCH0_EccPROT_UnCorrERR_IntStat:bit16,AXI 主接口 2 读取通道(数据)ECC 保护相关的不可纠正错误中断清除位。 该位用于清除相应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_RCH0_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_RCH0_EccPROT_UnCorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_RCH0_EccPROT_UnCorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF2_RCH0_EccPROT_CorrERR_IntStat:bit15,AXI 主接口 2 读取通道(数据)ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF2_RCH0_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF2_RCH0_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF2_RCH0_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_BCH_EccPROT_UnCorrERR_IntStat:bit14,AXI 主接口 1 写入响应通道 ECC 保护相关的不可纠正错误中断清除位。 该位用于清除相应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_BCH_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF1_BCH_EccPROT_UnCorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_BCH_EccPROT_UnCorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_BCH_EccPROT_CorrERR_IntStat:bit13,AXI 主接口 1 写入响应通道 ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_BCH_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF1_BCH_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_BCH_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_RCH1_EccPROT_UnCorrERR_IntStat:bit12,AXI 主接口 1 读取通道(其他控制信号)ECC 保护相关的不可纠正错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_RCH1_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1 (CLEAR_MXIF1_RCH1_EccPROT_UnCorrERR): 清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_RCH1_EccPROT_UnCorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_RCH1_EccPROT_CorrERR_IntStat:bit11,AXI 主接口 1 读取通道(其他控制信号)ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_RCH1_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF1_RCH1_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_RCH1_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_RCH0_EccPROT_UnCorrERR_IntStat:bit10,AXI 主接口 1 读取通道(数据)ECC 保护相关的不可纠正错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_RCH0_EccPROT_UnCorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF1_RCH0_EccPROT_UnCorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_RCH0_EccPROT_UnCorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_MXIF1_RCH0_EccPROT_CorrERR_IntStat:bit9,AXI 主接口 1 读取通道(数据)ECC 保护相关的可纠正错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg中的MXIF1_RCH0_EccPROT_CorrERR_IntStat)。

- ■ 0x1(CLEAR_MXIF1_RCH0_EccPROT_CorrERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的MXIF1_RCH0_EccPROT_CorrERR_IntStat中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_UndefinedReg_DEC_ERR_IntStat:bit8,从接口未定义寄存器解码错误中断清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_UndefinedReg_DEC_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_UndefinedReg_DEC_ERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的SLVIF_UndefinedReg_DEC_ERR中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_CommonReg_WRPARITY_ERR_IntStat:bit7,从接口通用寄存器写入奇偶校验错误中断 清除位。 该位用于清除对应通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_CommonReg_WRPARITY_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_CommonReg_WRPARITY_ERR):清除中断寄存器中的SLVIF_CommonReg_WRPARITY_ERR中断 DMAC_CommonReg_IntStatusReg ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_CommonReg_WrOnHold_ERR_IntStat:bit3,从接口公共寄存器写入保持错误中断清除位。 该位用于清除相应通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_CommonReg_WrOnHold_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_CommonReg_WrOnHold_ERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的SLVIF_CommonReg_WrOnHold_ERR中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_CommonReg_RD2WO_ERR_IntStat:bit2,从接口公共寄存器读取到只写错误中断清除位。 该位用于清除相应通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_CommonReg_RD2WO_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_CommonReg_RD2WO_ERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的SLVIF_CommonReg_RD2WO_ERR中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_CommonReg_WR2RO_ERR_IntStat:bit1,从接口公共寄存器写入只读错误中断清除位。 该位用于清除相应通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_CommonReg_WR2RO_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_CommonReg_WR2RO_ERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的SLVIF_CommonReg_WR2RO_ERR中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

- Clear_SLVIF_CommonReg_DEC_ERR_IntStat:bit0,从接口公共寄存器解码错误中断清除位。 该位用于清除对应的通道中断状态位(DMAC_CommonReg_IntStatusReg.SLVIF_CommonReg_DEC_ERR_IntStat)。

- ■ 0x1(CLEAR_SLVIF_CommonReg_DEC_ERR):清除中断寄存器DMAC_CommonReg_IntStatusReg中的SLVIF_CommonReg_DEC_ERR中断 ■ 0x0 (No_ACTION):无效信号。 不采取行动。

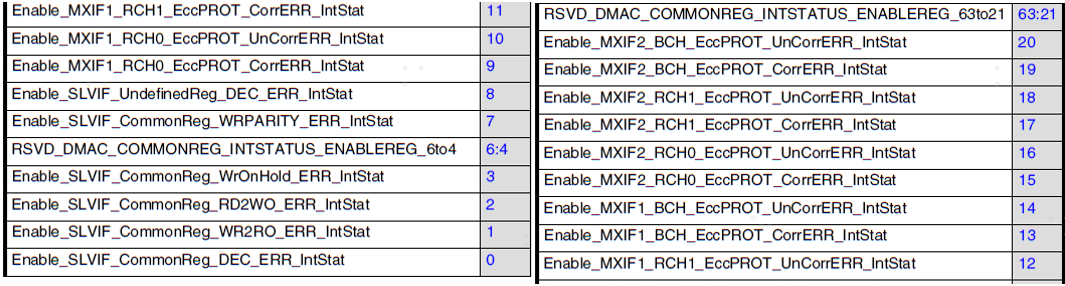

DMAC_COMMONREG_INTSTATUS_ENABLEREG

DW_axi_dmac 通用寄存器空间中断使能寄存器,■ 向特定字段写入1 可在DMAC 通用寄存器中断状态寄存器(DMAC_CommonReg_IntStatusReg) 中生成相应的中断状态。

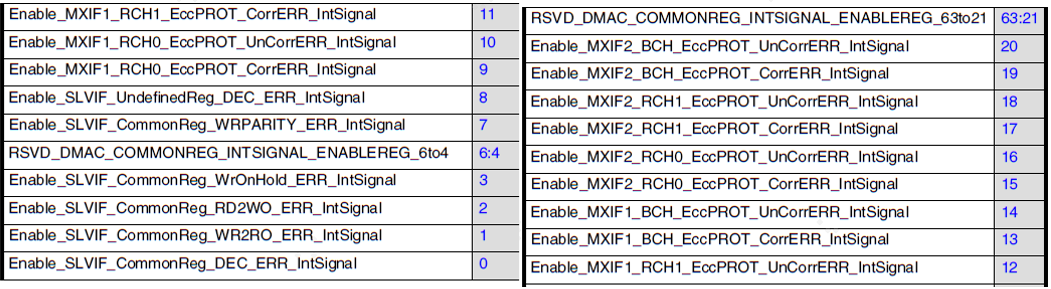

DMAC_COMMONREG_INTSIGNAL_ENABLEREG

DW_axi_dmac 通用寄存器空间中断信号使能寄存器 ■ 描述:向特定字段写入1 将在DMAC 公共寄存器中断状态寄存器(DMAC_CommonReg_IntStatusReg) 中传播相应的中断状态以产生port level中断。

Enable_MXIF2_BCH_EccPROT_UnCorrERR_IntSignal:AXI 主接口 2 写入响应通道 ECC 保护相关的不可纠正错误中断状态位。 该位用于使能相应的通道中断状态位 (DMAC_CommonReg_IntStatusReg 中的 MXIF2_BCH_EccPROT_UnCorrERR_IntStat)生成端口级中断。

Enable_MXIF2_BCH_EccPROT_UnCorrERR_IntSignal:AXI 主接口 2 写入响应通道 ECC 保护相关的不可纠正错误中断状态位。 该位用于使能相应的通道中断状态位 (DMAC_CommonReg_IntStatusReg 中的 MXIF2_BCH_EccPROT_UnCorrERR_IntStat)生成端口级中断。

■ 0x1(ENABLE_MXIF2_BCH_EccPROT_UnCorrERR_IntStat):DMAC_CommonReg_IntStatusReg 中的 MXIF2_BCH_EccPROT_UnCorrERR_IntStat 位在port level启用

■ 0x0(DISABLE_MXIF2_BCH_EccPROT_UnCorrERR_IntStat ): MXIF2_BCH_EccPROT_UnCorrERR_IntStat 信号输入 DMAC_CommonReg_IntStatusReg 在port level被禁用

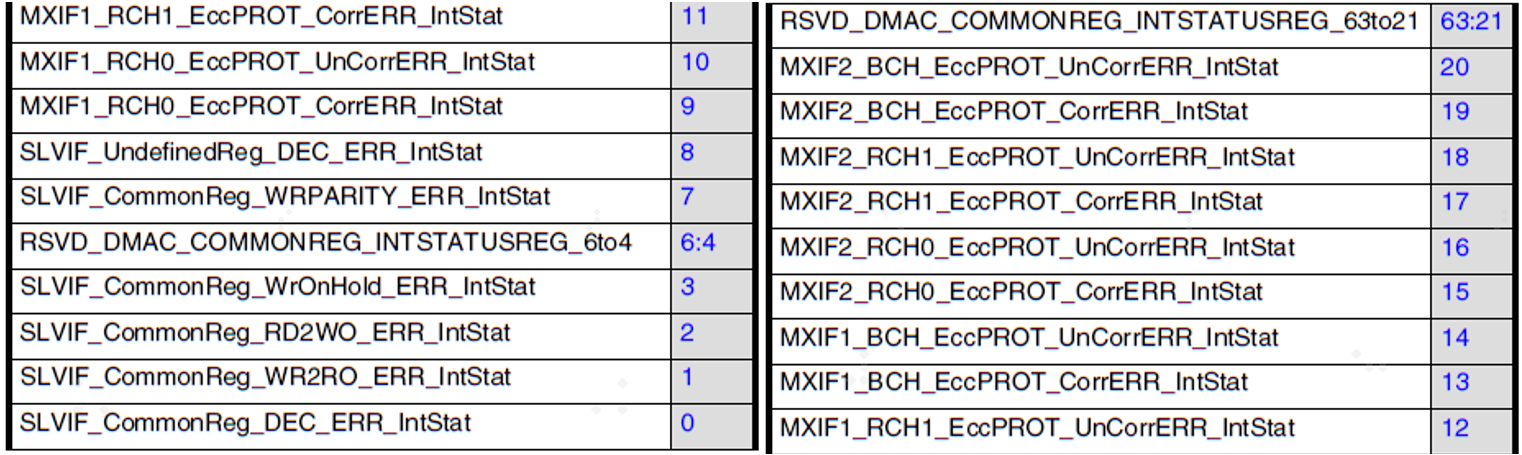

DMAC_COMMONREG_INTSTATUSREG

DW_axi_dmac 通用寄存器空间中断状态寄存器 该寄存器捕获从接口访问错误。 ❑ 解码错误。 ❑ 写入只读寄存器。 ❑ 只读寄存器。 ❑ 暂停写作。 ❑ 未定义的地址。 ❑ 公共寄存器空间 - 写奇偶校验错误

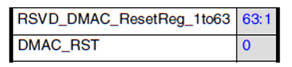

DMAC_RESETREG

DW_axi_dmac 软件复位寄存器 该寄存器用于启动对 DW_axi_dmac 的软件复位。

DMAC 复位请求位 软件向该位写入 1 以复位 DW_axi_dmac 并轮询该位以将其视为 0。DW_axi_dmac 复位除从机总线接口模块之外的所有模块并将该位清除为 0。 注意:不允许软件向该位写入 0。

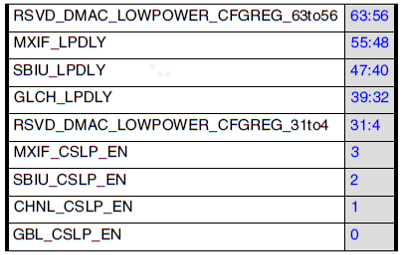

DMAC_LOWPOWER_CFGREG

DW_axi_dmac 低功耗配置寄存器,该寄存器包含配置 Context Sensitive 低功耗功能的字段。 应在启用通道之前对该寄存器进行编程。

MXIF_LPDLY:定义要编程到 AXI 主接口低功耗延迟计数器的负载值。 编程值必须大于或等于 0x4。 如果编程值小于 0x4,则寄存器值复位为 DMAX_MXIF_LPDLY。

写入该寄存器字段的最大值限于 (2**DMAX_MXIF_LPDLY_WIDTH)-1,否则该字段的高位(8-DMAX_MXIF_LPDLY_WIDTH)复位为0x0。 复位后的值:“(DMAX_MXIF_CSLP_EN==1) ? DMAX_MXIF_LPDLY : 0x0”

SBIU_LPDLY:定义要编程到 SBIU 低功耗延迟计数器的负载值。 编程值必须大于或等于 0x4。 如果编程值小于 0x4,则寄存器值复位为 DMAX_SBIU_LPDLY。

编程到该寄存器字段的最大值限制为 (2**DMAX_SBIU_LPDLY_WIDTH)-1,否则该字段的高位 (8-DMAX_SBIU_LPDLY_WIDTH) 将复位为 0x0。 复位后的值:“(DMAX_SBIU_CSLP_EN==1)?DMAX_SBIU_LPDLY:0x0”

GLCH_LPDLY:定义要编程到全局和 DMA 通道低功耗延迟计数器中的加载值。 编程值必须大于或等于 0x4。 如果编程值小于 0x4,则寄存器值复位为 DMAX_GLCH_LPDLY。

写入该寄存器字段的最大值限于 (2**DMAX_GLCH_LPDLY_WIDTH)-1,否则该字段的高位(8-DMAX_GLCH_LPDLY_WIDTH)复位为0x0。 复位后的值:“(DMAX_CSLP_EN==1)? DMAX_GLCH_LPDLY:0x0"

MXIF_CSLP_EN:AXI 主接口上下文相关低功耗功能使能。

SBIU_CSLP_EN:SBIU Context Sensitive Low Power feature enable。

CHNL_CSLP_EN:DMA Channel Context Sensitive Low Power feature enable

GBL_CSLP_EN:Global Context Sensitive Low Power feature enable。

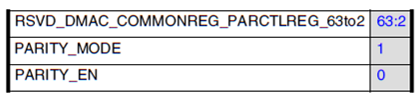

DMAC_COMMON_PARCTLREG

DW_axi_dmac 奇偶校验控制寄存器,该寄存器包含启用/禁用奇偶校验保护功能的字段和选择偶数或奇数奇偶校验模式的字段。

PARITY_MODE:奇偶校验模式,为奇偶校验保护功能选择偶数或奇数奇偶校验方案。

■ 0x0 (Even_PARITY_MODE):偶奇偶校验用于公共/通道特定空间中的寄存器;■ 0x1 (Odd_PARITY_MODE):奇奇偶校验用于公共/通道特定空间中的寄存器。复位后的值:DMAX_DEF_PARITY_MODE。

PARITY_EN:该字段用于启用/禁用奇偶校验保护功能。 ■ 0x0 (Disable_PARITY):公共/通道寄存器空间中寄存器的奇偶校验被禁用 ■ 0x1 (Enable_PARITY):启用公共/通道寄存器空间中寄存器的奇偶校验

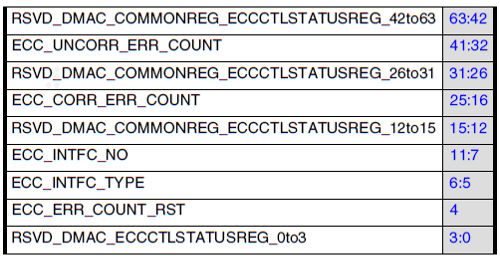

DMAC_COMMON_ECCCTLSTATUREG

DW_axi_dmac ECC 控制和状态寄存器

该寄存器包含的字段:

❑ 复位ECC 保护可纠正和不可纠正计数器。 ❑ 有助于复用不同 DMA 通道 FIFO 存储器接口、不同 DMA 通道 UID 存储器接口、不同 AXI 主接口通道的上述计数器值的字段。 ❑ ECC 保护可纠正和不可纠正计数器状态。

Exists: DMAX_ECC_DIAG_EN == 1

ECC_UNCORR_ERR_COUNT:ECC Uncorrectable Error count,此字段提供自ECC错误计数复位或软复位或dmac_resetn以来检测到的不可纠正错误的数量。

ECC_CORR_ERR_COUNT:ECC Correctable Error count,此字段提供自ECC错误计数复位或软复位或dmac_resetn以来检测到的可纠正错误的数量。

ECC_INTFC_NO:ECC Protected Interface Number,用于提供特定接口类型的接口号,复用可纠正和不可纠正的错误计数器。 该字段的编码如下:

■ 当 ECC_INTFC_TYPE = 0x0 或 0x1 时 该字段值可以从 1 到 DMAX_NUM_CHANNELS 不等。 如果非法值被编程到该字段,即值超出配置的通道数,则计数器将返回全零。

■ 当 ECC_INTFC_TYPE = 0x2 时 然后该字段值可以如下所述更改:

- ECC_INTFC_NO[11:10] = 2'b00

- ECC_INTFC_NO[9] = DMAX_NUM_MASTER_IF-1。

AXI Master Interface Number 可以在 0 到 DMAX_NUM_MASTER_IF-1 之间变化。 如果将非法值编程到该字段,即超出配置的 AXI 主接口数量的值,则计数器将返回全零。

- ECC_INTFC_NO[8:7] = 该字段用于选择 AXI 主接口的特定通道。 2'b00: AXI Read Data Channel - RCH0 (Read data ECC counter),

2'b01: AXI Read Data Channel - RCH1 (Read Data Channel other signals), 2'b10: AXI Write Response Channel - BCH

如果将非法值编程到该字段,则计数器将返回全零。

ECC_INTFC_TYPE:ECC 保护接口类型 这用于选择通过 ECC 保护的所需接口。该字段用于为 FIFO 内存接口、AXI 内存接口等接口类型多路复用可纠正、不可纠正错误计数器。 如果保留值被编程,则计数器将返回全零。

■ 0x0 (ECC_CH_MEMIF):通道 FIFO 内存接口 ■ 0x1 (ECC_UID_MEMIF):通道 UID 内存接口 ■ 0x2 (ECC_AXI_MXIF):AXI 主接口 ■ 0x3 (RSV_ECC_INTFC):保留

ECC_ERR_COUNT_RST:ECC 错误计数复位,该位用于复位 ECC 保护可纠正和不可纠正计数器。 所有内部 ECC 错误计数器清零后,该位自动清零。

■ 0x0 (ECC_COUNT_NORST):不复位 ECC 错误计数器 ■ 0x1 (ECC_COUNT_RST):复位 ECC 错误计数器

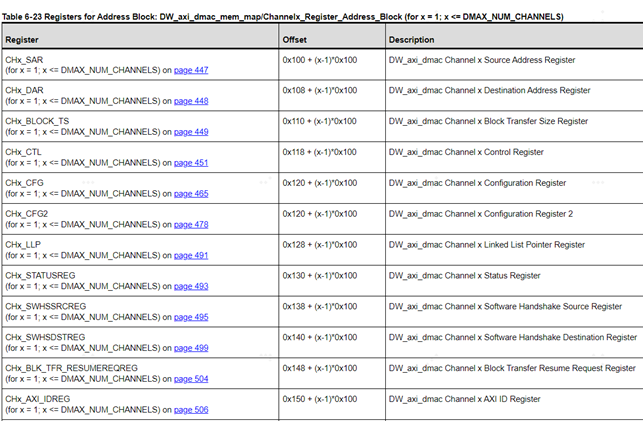

通道专属寄存器

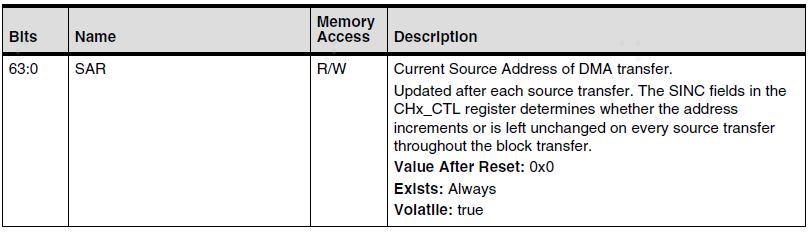

CHx_SAR

DW_axi_dmac通道x的源地址寄存器,起始源地址在DMA通道启用之前由软件编程,或者在DMA传输开始之前由LLI更新。当DMA传输正在进行时,这个寄存器将被更新以反映当前AXI传输的源地址。偏移量:0x100 + (x-1)*0x100。

当前DMA传输的源地址,在每次源传输后更新。CHx_CTL寄存器中的SINC字段决定了在整个块传输的每次源传输中,地址是增加还是保持不变。

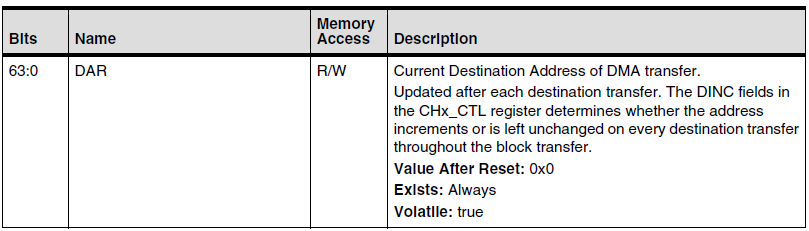

CHx_DAR

DW_axi_dmac通道x的目的地址寄存器,起始目的地址在DMA通道被启用之前由软件编程,或者在DMA传输开始之前由LLI更新。当DMA传输正在进行时,这个寄存器将被更新以反映当前AXI传输的目的地址。偏移量:0x108 + (x-1)*0x100。

DMA传输的当前目的地址,每次目标传输后更新。CHx_CTL寄存器中的DINC字段决定在整个块传输的每次目标传输中,地址是增加还是保持不变。

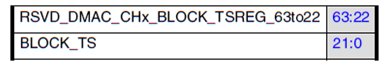

CHx_BLOCK_TS

DW_axi_dmac通道x块传输大小寄存器,当DW_axi_dmac是流控制器时,DMAC在为块大小启用通道之前使用这个寄存器。偏移量:0x110 + (x-1)*0x100。

写入BLOCK_TS字段的数字表示在DMA块传输中要传输的宽度为CHx_CTL.SRC_TR_WIDTH的数据总数,块传输大小Block Transfer Size= BLOCK_TS+1。

当传输开始时,读回的值是已经从源外设读取的数据项的总数,而不管谁是流控制器。当源或目标外设被指定为流控制器时,传输开始前的值在DMAX_CHx_MAX_BLK_SIZE处饱和,但实际的块大小可以更大。

CHx_CTL

DW_axi_dmac通道x控制寄存器,这个寄存器包含了控制DMA传输的字段。除了基于LLI的多块传输之外,应该在启用通道之前对该寄存器进行编程。

当启用基于LLI的多块传输时,CHx_CTL寄存器将从LLI的相应位置加载,并且可以在DMA传输中逐个块地更改它。软件不允许通过DW_axi_dmac从机接口直接更新该寄存器。

在基于LLI的多块传输过程中,对该寄存器的任何写入都被忽略。偏移量:0x118 + (x-1)*0x100

- SHADOWREG_OR_LLI_VALID:影子寄存器内容/链表项有效。指示从内存中获取的影子寄存器或链表项的内容是否有效。0:表示影子寄存器内容/LLI无效。1: Last Shadow Register/LLI有效。

- 基于LLI的多块传输:CHx_CTL寄存器从LLI加载。因此,软件不允许通过DW_axi_dmac从机接口直接更新这个寄存器。

- 该字段可以被软件用来动态扩展LLI。注意到此位为0,DW_axi_dmac丢弃LLI并生成ShadowReg_Or_LIl_Invalid_ERR中断,如果相应的通道错误中断屏蔽位设置为0。

- 在LLI预取的情况下,即使对于预取的LLI, ShadowReg_Or_LLI_Invalid_ERR位被认为是0,也不会生成ShadowReg_Or_LLI_Invalid_ERR中断。在这种情况下,DW_axi_dmac在完成当前块传输后再次尝试LLI获取操作,并仅当ShadowReg_Or_Lil_Valid位仍然为0时才生成ShadowReg_Or_Lll_Invalid_ERR中断。

- 此错误条件导致DW_axi_dmac优雅地停止相应的通道。DW_axi_dmac 等待直到软件写入(任何值)到 CHx_BLK_TFR_ResumeReqReg 用于在尝试另一个 LLI 读取操作之前指示有效的 LLI 可用性。 当启用 LLI 写回选项时,该位被清零并在块传输完成后写回相应的 LLI 位置。 因此,对于基于 LLI 的多块传输,如果启用 LLI 回写选项,软件可能会操纵/重新定义任何描述符,并将 ShadowReg_Or_LII_Valid 位设置为 0。

- 基于LLI的多块传输:CHx_CTL寄存器从LLI加载。因此,软件不允许通过DW_axi_dmac从机接口直接更新这个寄存器。

-

- 基于影子寄存器的多块传输:在影子寄存器获取阶段注意到这个位为0,DW_axi_dmac丢弃影子寄存器内容,并生成ShadowReg_Or_LLI_Invlid_ERR中断。在这种情况下,软件必须在更新影子寄存器并将ShadowReg_Or_LLi_Valid位设置为1之后向CHx_BLK_TFR_ResumeReqReg写入(任何值),以指示DW_axi_dmac影子寄存器内容是有效的,下一个块传输可以恢复。

- DW_axi_dmac在复制影子寄存器内容后将该位清除为0。只有ShadowReg_Or_LLI_Valid位为0时,软件才能对影子寄存器进行重编程。软件需要在块完成中断服务例程中读取这个寄存器(如果中断被启用)/持续轮询这个寄存器(如果中断没有被启用),以确保在更新影子寄存器之前这个位为0。

- 如果启用了基于影子寄存器的多块传输,当ShadowReg_Or_LLI_Valid位为1时,软件试图写入影子寄存器,DW_axi_dmac会产生SLVIF_ShadowReg_WrOnValid_ERR中断。

- 基于影子寄存器的多块传输:在影子寄存器获取阶段注意到这个位为0,DW_axi_dmac丢弃影子寄存器内容,并生成ShadowReg_Or_LLI_Invlid_ERR中断。在这种情况下,软件必须在更新影子寄存器并将ShadowReg_Or_LLi_Valid位设置为1之后向CHx_BLK_TFR_ResumeReqReg写入(任何值),以指示DW_axi_dmac影子寄存器内容是有效的,下一个块传输可以恢复。

-

- 0x1 (VALID):表示shadowreg/LLI内容有效,0x0 (INVALID):表示shadowreg/LLI内容无效。

- SHADOWREG_OR_LLI_LAST:最后一个影子寄存器/链表项。指示从内存中获取的影子寄存器内容或链表项是否是最后一个。0:不是最后一个影子寄存器/LLI1:最后一个影子寄存器/LLI。

- 基于LLI的多块传输:DW_axi_dmac使用这个位来决定当前是否需要另一个LLI获取。

- 如果此位为0,DW_axi_dmac将从当前LLI的LLP字段所指向的地址中获取下一个LLI。

- 如果这个位是1,DW axi dmac就会知道当前块是dma传输的最后一块,一旦与当前块相对应的AMBA传输完成,DW axi dmac就会结束dma传输。

- 基于Shadow Reg的多块传输:DW_axi_dmac使用这个位来决定当前DMA传输中是否需要另一个Shadow Register获取。

- 如果该位为0,DW_axi_dmac就知道当前块中有一个或多个块要传输,因此一个或多个影子寄存器集内容是有效的,需要获取。

- 如果这个位是1,DW_axi_dmac就会理解当前块是dma传输中的最后一个块,并且在与当前块相对应的AMBA传输完成后就会结束dma传输。

- 0x1 (LAST_ITEM):表示shadowreg/LLI内容是最后一个,0x0 (NOT LAST ITEM):表示shadowreg/LLI内容不是最后一个

- 基于LLI的多块传输:DW_axi_dmac使用这个位来决定当前是否需要另一个LLI获取。

- IOC_BlkTfr:块传输完成时中断。

- 该位用于控制基于影子寄存器或链表的多块传输的块传输完成中断的生成。向该寄存器字段写入1可以启用CHx_IntStatusReg.BLOCK_TFR_DONE_IntStat字段,如果在CHx_IntStatus_EnableReg寄存器中启用了中断生成,并且在CHx_IntSignal_EnableReg寄存器中启用了中断生成,则断言外部中断输出。

- 注意:如果源和目的没有同时使用基于链表或影子寄存器的多块传输(例如,源和目的使用连续地址或基于自动重载的多块传输),则该字段的值不能按块修改。此外,在通道启用之前编写的值用于DMA传输中的所有块。

- 0x1(Enable_BLKTFR_INTR):启用 CHx_IntStatusReg.BLOCK_TFR_DONE_IntStat字段; 0x0(DISABLE_BLKTFR_INTR):禁用 CHx_IntStatusReg.BLOCK_TFR_DONE_IntStat字段

- DST_STAT_EN: 目的地址状态使能。从CHx_DSTATAR寄存器内容指向的通道x的目标外设获取状态的使能逻辑,并将该状态信息存储在CHx_DSTAT寄存器中。如果DMAX_CHx_LLI_WB_EN设置为1,且源外设或目标外设使用基于链表的多块传输,则该值在每个块传输结束时被写回链表的CHx_DSTAT位置。

- 0x1 (Enable_STAT_FETCH):启用Destination的状态获取,并将值存储在CH1_DSTAT寄存器中.0x0 (NO_STAT_FETCH):不获取目的设备的状态

- SRC_STAT_EN:源地址状态使能。从CHx_SSTATAR寄存器的内容指向的通道x的源外设获取状态的使能逻辑,并将其存储在CHx_SSTAT寄存器中。如果DMAX_CHx_LLI_WB_EN设置为1,且源外设或目标外设使用基于链表的多块传输,则该值在每个块传输结束时被写回链表的CHx_SSTAT位置。

- 0x1 (Enable_STAT_FETCH):启用Source的状态获取,并将值存储在CH1_SSTAT寄存器中.0x0 (NO_STAT_FETCH):不获取源设备的状态

- AWLEN:目的地突发长度,用于目标数据传输的突发长度。指定的突发长度用于目标数据传输,直到可能的范围;其余的传输使用小于或等于DMAX_CHX_MAX_AMBA_BURST_LENGTH的最大可能值。

- AWLEN的最大值受DMAX_CHx_MAX_AMBA_BURST_LENGTH的限制。

- 注意:AWLEN设置可能不适用于endto-block传输、传输结束(仅适用于非内存外设)和4K边界跨越期间。

- AWLEN_EN:目的突发长度使能,如果这个位设置为1,DW_axi_dmac使用CHx_CTL.AWLEN的值作为AXI的目标数据传输的突发长度,直到可能的范围;其余传输使用最大可能的突发长度。

- 如果此位设置为0,DW_axi_dmac将使用任何小于或等于DMAX_CHx_MAX_AMBA_BURST_LENGTH的值作为目标数据传输的AXI Burst长度。

- 0x1 (Enable):目的数据传输的AXI Burst Length为CH1_CTL. AWLEN的值。0x0(Disable):目的数据传输的AXI Burst Length为小于等于DMAX_CH1_MAX_AMBA_BURST_LENGTH的任意值。

- ARLEN : Source Burst Length,用于源数据传输的 AXI 突发长度。 指定的突发长度用于源数据传输直到可能的程度; 剩余传输使用小于或等于 DMAX_CHx_MAX_AMBA_BURST_LENGTH 的最大可能值。ARLEN 的最大值受 DMAX_CHx_MAX_AMBA_BURST_LENGTH 限制.

- ARLEN_EN:Source Burst Length Enable,如果该位设置为 1,DW_axi_dmac 使用 CHx_CTL.ARLEN 的值作为源数据传输的 AXI Burst 长度,直到可能为止; 剩余的传输使用最大可能的突发长度。

- 如果此位设置为 0,则 DW_axi_dmac 使用任何可能的值 小于或等于 DMAX_CHx_MAX_AMBA_BURST_LENGTH 作为源数据传输的 AXI 突发长度。

- ■ 0x1(启用):AXI 突发长度为 CH1_CTL.ARLEN(直到 在可能的范围内)用于源数据传输 ■ 0x0(禁用):AXI 突发长度是任何可能的值 <=用于源数据传输的DMAX_CH1_MAX_AMBA_BURST_LENGTH

- AW_PROT R/W AXI“aw_prot”信号,复位后的值:0x0

- AR_PROT R/W AXI“ar_prot”信号 重置后的值:0x0

- NonPosted_LastWrite_En:非上传最后写启用,该位决定在整个块传输过程中是否可以使用已发布的写操作。

- 0:在整个块传输过程中可以使用已发送的写操作。1:已发布的写操作可以一直使用到块的末尾(在块内部),并且块中的最后一次写操作必须是非发布的。这是为了将块完成中断的生成同步到到达终点的最后一个写数据内存/外设。

- 0x1 (Enable):块中的最后一次写必须是非发布的,0x0 (Disable):在整个块传输过程中可以使用已发布的写操作。

- AW_CACHE:AXI 'aw_cache' signal,Value After Reset: 0x0

- AR_CACHE:AXI 'ar_cache' signal,Value After Reset: 0x0

- DST_MSIZE:目标突发传输长度。数据项的数量,每个数据项宽度为CHx_CTL.DST_TR,每次从相应的硬件或软件握手发出目标突发传输请求时写入目的地接口。注意:此值与AXI无关。

-

- ■0x0 (DATA_ITEM_1):突发事务中从 Destination 读取的 1 个 数据项 ■ 0x1 (DATA_ITEMS_4):在突发事务中从目标读取的 4 个数据项

- ■ 0x2 (DATA_ITEMS_8):突发事务中从目标读取的 8 个数据项 ■ 0x3 (DATA_ITEMS_16):在突发事务中从目标读取的 16 个数据项

- ■ 0x4 (DATA_ITEMS_32):在突发事务中从目标读取的 32 个数据项 ■ 0x5 (DATA_ITEMS_64):突发事务中从目标读取的 64 个数据项

- ■ 0x6 (DATA_ITEMS_128):在突发事务中从目标读取的 128 个数据项 ■ 0x7 (DATA_ITEMS_256):在突发事务中从目标读取的 256 个数据项

- ■ 0x8 (DATA_ITEMS_512):在突发事务中从目标读取的 512 数据项 ■ 0x9 (DATA_ITEMS_1024):在突发事务中从 目标读取的 1024 数据项

- DST_MSIZE的最大值受DMAX_CHX_MAX_MSIZE的限制。注意:此值与AXI信号无关。

-

- SRC_MSIZE:源突发传输长度。每个宽度为CHx_CTL.SRC_TR_WIDTH的数据项的数量,每次从相应的硬件或软件握手接口发出源突发传输请求时从源读取的数据宽度。

- ■0x0 (DATA_ITEM_1):突发事务中从 源读取的 1 个 数据项 ■ 0x1 (DATA_ITEMS_4):在突发事务中从源读取的 4 个数据项

- ■ 0x2 (DATA_ITEMS_8):突发事务中从源读取的 8 个数据项 ■ 0x3 (DATA_ITEMS_16):在突发事务中从源读取的 16 个数据项

- ■ 0x4 (DATA_ITEMS_32):在突发事务中从源读取的 32 个数据项 ■ 0x5 (DATA_ITEMS_64):突发事务中从源读取的 64 个数据项

- ■ 0x6 (DATA_ITEMS_128):在突发事务中从源读取的 128 个数据项 ■ 0x7 (DATA_ITEMS_256):在突发事务中从源读取的 256 个数据项

- ■ 0x8 (DATA_ITEMS_512):在突发事务中从源读取的 512 数据项 ■ 0x9 (DATA_ITEMS_1024):在突发事务中从源读取的 1024 数据项

- DST_TR_WIDTH:目标传输宽度,映射到AXI总线awsize,该值必须小于或等于DMAX_M_DATA_WIDTH。

- ■ 0x0 (BITS_8):目标传输宽度为 8 位 ■ 0x1 (BITS_16):目标传输宽度为 16 位 ■ 0x2 (BITS_32):目标传输宽度为 32 位 ■ 0x3 (BITS_64):目标传输宽度为 64 位

- ■ 0x4 (BITS_128):目标传输宽度为 128 位 ■ 0x5 (BITS_256):目标传输宽度为 256 位 ■ 0x6 (BITS_512):目标传输宽度为 512 位

- 复位后的值:{(DMAX_CH(x)_DTW_ENC < 7) ? DMAX_CH(x)_DTW_ENC:2}

- SRC_TR_WIDTH:源传输宽度。映射到AXI总线arsize,该值必须小于或等于DMAX_M_DATA_WIDTH。

- ■ 0x0 (BITS_8):源传输宽度为 8 位 ■ 0x1 (BITS_16):源传输宽度为 16 位 ■ 0x2 (BITS_32):源传输宽度为 32 位 ■ 0x3 (BITS_64):源传输宽度为 64 位

- ■ 0x4 (BITS_128):源传输宽度为 128 位 ■ 0x5 (BITS_256):源传输宽度为 256 位 ■ 0x6 (BITS_512):源传输宽度为 512 位

- 复位后的值:{(DMAX_CH(x)_STW_ENC < 7) ? DMAX_CH(x)_STW_ENC:2}

- DINC:目的地址增量。指示是否在每次目的传输时增加目的地址。如果设备正在向一个固定地址的源外设FIFO写数据,那么将该字段设置为“No change”。0:增量1:无变化

- 注意:增量使地址与下一个CHx_CTL.DST_TR_WIDTH边界对齐。

- ■ 0x0(递增):目标地址在每次源传输时递增 ■ 0x1 (FIXED):目标地址是固定的

- SINC:源地址增量。指示是否在每次源传输时增加源地址。如果设备从一个固定地址的源外设FIFO获取数据,那么将该字段设置为“No change”。.0:增量.1:没有变化

- 注意:增量使地址与下一个CHx_CTL.SRC_TR_WIDTH 边界对齐。

- ■ 0x0(递增):源地址在每次源传输时递增 ■ 0x1 (FIXED):目标地址是固定的

- DMS:目的地址主机选择。标识访问目标设备(外设或内存)的主机接口层。0: AXI主机1,1: AXI主机2

- SMS:源地址主机选择。标识访问源设备(外设或内存)的主机接口层。0: AXI主机1,1: AXI主机2。

- CHx_SSTAT:DW_axi_dmac通道x源状态寄存器。Channelx源状态寄存器在每个块传输完成后,硬件可以从CHx_SSTATAR寄存器的内容所指向的地址检索源状态信息。

- 然后将此状态信息存储在CHx_SSTAT寄存器中,并在下一个块开始之前将其写入LLI的CHx_SSTAT寄存器位置。

- 只有当DMAX_CHx_LLI_WB_EN = 1并且为通道的源外设或目标外设启用了基于链表的多块传输时,才执行源状态回写到LLI的CHx_SSTAT寄存器位置。

- 如果DMAC_CHx_SRC_STAT_EN设置为False,则该寄存器不存在;在这种情况下,回读值总是0。偏移量:0x160 + (x-1)*0x100。

- CHx_SSTATAR:DW_axi_dmac通道x源状态获取寄存器。在完成每个块传输后,硬件可以从用户定义的地址(CHx_SSTATAR寄存器的内容指向该地址)检索源状态信息。

- 可以选择系统内存中提供64位值的任何位置,以指示源传输的状态。如果DMAC_CHx_SRC_STAT_EN设置为False,则该寄存器不存在;在这种情况下,回读值总是0。偏移量:0x170 + (x-1)*0x100

- 源状态获取地址,硬件可以从CHx_SSTATAR这里获取源状态信息的指针,获取的状态信息被存储在CHx_SSTAT寄存器中.

- 如果DMAX_CHx_LLi_WB_EN = 1,并为通道的源或目标外设启用基于链表的多块传输,则在下一个块开始之前被写到LLI的CHx_SSTAT寄存器位置。

- 源外设应该在CHx_SSTATAR所指向的位置更新源状态信息(如果有的话),以利用此功能。此状态与DW axi dmac的任何内部状态无关。

- CHx_DSTATAR:DW_axi_dmac通道x目的状态获取寄存器。在完成每个块传输后,硬件可以从用户定义地址(CHx_DSTATAR寄存器的内容指向的地址)检索目标状态信息。

- 可以选择系统内存中的任何位置,该位置将提供一个64位值来指示目标传输的状态。如果DMAC_CHx_SRC_STAT_EN设置为False,则该寄存器不存在;在这种情况下,回读值总是0。偏移量:0x178 + (x-1)*0x100

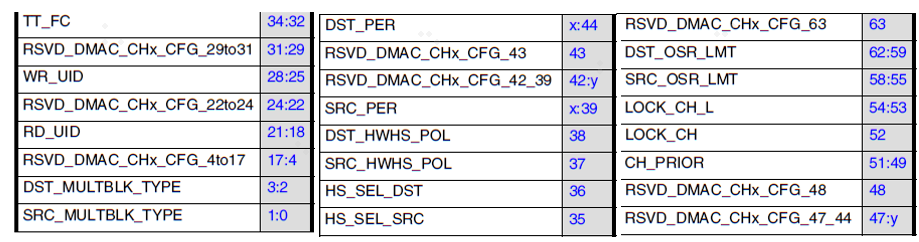

CHx_CFG

DW_axi_dmac 通道 x 配置寄存器

■ 说明:该寄存器包含配置DMA 传输的字段。 应在启用通道之前对该寄存器进行编程。

通道配置寄存器的位 [63:32] 对于多块传输的所有块保持固定,并且只能在通道被禁用时进行编程。即使通道被使能,通道配置寄存器的位 [3:0] 也可以进行编程.

Software 清除这些位以结束多块传输。 对于基于 Contiguous-Address 和 Auto-Reloading 的多块传输(如果源和目标外设都没有使用基于 Shadow-Register 或 Linked-List 的多块传输),如果相应的多块类型选择位即 CHx_CFG.SRC_MLTBLK_TYPE 和/或 CHx_CFG.DST_MLTBLK_TYPE 位在块传输结束时被视为 2'b00,DW_axi_dmac 知道前一个块是传输中的最后一个块并完成 DMA 传输操作。

- DST_OSR_LMT:目标未完成请求限制 ■ 支持的最大未完成请求是 16。 ■ 源未完成请求限制 = DST_OSR_LMT + 1

- SRC_OSR_LMT:源未完成请求限制 ■ 支持的最大未完成请求是 16。 ■ 源未完成请求限制 = DST_OSR_LMT + 1

- LOCK_CH_L:Channel Lock Level,该位表示CHx_CFG.LOCK_CH位适用的持续时间。

- ■ 00:完成 DMA 传输 ■ 01:通过 DMA 块传输 ■ 1x:保留 如果配置参数 DMAX_CHx_LOCK_EN 设置为 False,则该字段不存在; 在这种情况下,回读值始终为 0。

- ■ 0x0 (DMA_transfer_CH_LOCK):通道锁定的持续时间适用于整个 DMA 传输 ■ 0x1 (BLOCK_TRANFER_CH_LOCK):通道锁定的持续时间是针对当前块传输的

- LOCK_CH:Channel Lock 位,当通道被授予主总线接口的控制权并且如果 CHx_CFG.LOCK_CH 位被断言,则在 CHx_CFG.LOCK_CH_L 指定的持续时间内没有其他通道被授予主总线接口的控制权。

- 向主总线接口仲裁器表明该通道想要在 CHx_CFG.LOCK_CH_L 中指定的持续时间内独占访问主总线接口。

- 如果配置参数 DMAX_CHx_LOCK_EN 设置为 False,则该字段不存在; 在这种情况下,回读值始终为 0。锁定通道会锁定相应主接口上的 AXI 读取地址、写入地址和写入数据通道。

- 注意:通道锁定功能仅支持块传输和 DMA 传输级别的内存到内存传输。 硬件不检查通道锁定设置的有效性,因此软件必须注意仅在块传输或 DMA 传输级别为内存到内存传输启用通道锁定。 通道锁定的非法编程可能会导致不可预知的行为。

- 值: ■ 0x0 (NO_CHANNEL_LOCK):传输期间通道未锁定 ■ 0x1 (CHANNEL_LOCK):通道被锁定并被授予对主总线接口的独占访问权限

- CH_PRIOR:Channel Priority,DMAX_NUM_CHANNELS-1的优先级最高,0最低。 此字段必须在以下范围内编程: 0: DMAX_NUM_CHANNELS-1,超出此范围的编程值将导致错误行为。

- DST_PER:如果 CHx_CFG.HS_SEL_DST 字段为 0,则将硬件握手接口 (0 -DMAX_NUM_HS_IF-1) 分配给 Channelx 的目的地; 否则,该字段将被忽略。 然后通道可以通过分配的硬件握手接口与连接到该接口的目标外设进行通信。

- 注意:对于正确的 DW_axi_dmac 操作,只应将一个外设(源或目标)分配给同一握手接口。 如果配置参数 DMAX_NUM_HS_IF 设置为 0,则该字段不存在。

- x = 44 如果 DMAC_NUM_HS_IF 为 1; x = ceil(log2(DMAC_NUM_HS_IF)) + 43 如果 DMAC_NUM_HS_IF 大于 1 ;bit 47 :(x+1) 不存在,读取时返回 0。

- SRC_PER:如果 CHx_CFG.HS_SEL_DST 字段为 0,则将硬件握手接口 (0 -DMAX_NUM_HS_IF-1) 分配给 Channelx 的源; 否则,该字段将被忽略。 然后通道可以通过分配的硬件握手接口与连接到该接口的源外设进行通信。

- 注意:对于正确的 DW_axi_dmac 操作,只应将一个外设(源或目标)分配给同一握手接口。 如果配置参数 DMAX_NUM_HS_IF 设置为 0,则该字段不存在。

- x = 39 如果 DMAC_NUM_HS_IF 为 1; x = ceil(log2(DMAC_NUM_HS_IF)) + 38 如果 DMAC_NUM_HS_IF 大于 1 ;bit 42 :(x+1) 不存在,读取时返回 0。

- DST_HWHS_POL:目标硬件握手接口极性。 ■ 0:高电平有效 ■ 1:低电平有效

- ■ 0x0 (ACTIVE_HIGH):用于目标外设的握手接口的极性为高电平有效 ■ 0x1 (ACTIVE_LOW):用于目标外设的握手接口的极性为低电平有效

- SRC_HWHS_POL:源硬件握手接口极性。 ■ 0:高电平有效 ■ 1:低电平有效

- ■ 0x0 (ACTIVE_HIGH):用于源外设的握手接口的极性为高电平有效 ■ 0x1 (ACTIVE_LOW):用于源外设的握手接口的极性为低电平有效

- HS_SEL_DST:目标软件或硬件握手选择。 该寄存器选择哪个握手接口(硬件或软件)对于该通道上的目标请求是活动的。

- ■ 0:硬件握手接口。 忽略软件发起的交易请求。 ■ 1:软件握手接口。 忽略硬件启动的事务请求。

- 如果目标外设是内存,则忽略该位。

- ■ 0x0 (HARDWARE_HS):硬件握手接口用于目标外设 ■ 0x1 (SOFTWARE_HS):软件握手接口用于目标外设

- HS_SEL_SRC:源软件或硬件握手选择。 该寄存器选择哪个握手接口(硬件或软件)对于该通道上的源请求是活动的。

- ■ 0:硬件握手接口。 忽略软件发起的传输请求。 ■ 1:软件握手接口。 忽略硬件启动的事务请求。

- 如果源外设是内存,则忽略该位。

- ■ 0x0 (HARDWARE_HS):硬件握手接口用于源外设 ■ 0x1 (SOFTWARE_HS):软件握手接口用于源外设

- TT_FC: 传输类型和流量控制。支持以下传输类型。

- Memory to Memory ; Memory to Peripheral ; Peripheral to Memory; Peripheral to Peripheral

- 可以将流控制分配给DW_axi_dmac、源外设或目标外设。

- 0x0 (MEM_TO_MEM_DMAC): 传输类型为memory to memory,流控制器为DW_axi_dmac; 0x1 (MEM_TO_PER_DMAC): 传输类型为memory to peripheral ,流控制器为 DW_axi_dmac

- 0x2 (PER_TO_MEM_DMAC): 传输类型为peripheral to memory ,流控制器 为DW_axi_dmac; 0x3 (PER_TO_PER_DMAC): 传输类型为peripheral to peripheral ,流控制器 为DW_axi_dmac

- 0x4 (PER_TO_MEM_SRC): 传输类型为peripheral to Memory ,流控制器 为Source peripheral 0x5 (PER_TO_PER_SRC): 传输类型为peripheral to peripheral ,流控制器 为Source peripheral

- 0x6 (MEM_TO_PER_DST): 传输类型为memory to peripheral ,流控制器 为Destination peripheral 0x7 (PER_TO_PER_DST): 传输类型为peripheral to peripheral ,流控制器 为Destination peripheral

- WR_UID:定义 AXI Write Channel 支持的 AXI Unique ID 的数量。 编程的值必须小于或等于 DMAX_CH(x)_WR_UID。 否则,它受限于值 DMAX_CH(x)_WR_UID。 复位后的值:DMAX_CH(x)_RST_WR_UID

- RD_UID:定义 AXI Read Channel 支持的 AXI Unique ID 的数量。 编程的值必须小于或等于 DMAX_CH(x)_RD_UID。 否则,它受限于值 DMAX_CH(x)_RD_UID。 复位后的值:DMAX_CH(x)_RST_RD_UID

- DST_MULTBLK_TYPE:目标多块传输类型。 这些位定义用于目标外设的多块传输类型。 ■ 00:连续 ■ 01:重新加载 ■ 10:影子寄存器 ■ 11:链表

- 如果选择的类型是连续的,则 CHx_DAR 寄存器加载前一个块的结束目标地址的值 + 1 在每个块的末尾进行多块传输。 然后启动新的块传输。

- 如果选择的类型是 Reload,CHx_DAR 寄存器在多块传输的每个块结束时从 DAR 的初始值重新加载。 然后启动新的块传输。

- 如果选择的类型是影子寄存器,如果 CHx_CTL.ShadowReg_Or_LLI_Valid 位在多块传输的每个块末尾设置为 1,则从其影子寄存器的内容加载 CHx_DAR 寄存器。 然后启动新的块传输。

- 如果选择的类型是链表,如果 CTL.ShadowReg_Or_LLI_Valid 位在多块传输的每个块末尾设置为 1,则从链表加载 CHx_DAR 寄存器。 然后启动新的块传输。

- 多块传输中,基于为源和目标外设编程的多块传输类型,CHx_CTL 和 CHx_BLOCK_TS 寄存器从它们的初始值或从它们的影子寄存器的内容(如果 CHx_CTL.ShadowReg_Or_LLI_Valid 位设置为 1)或从链表(如果 CTL.ShadowReg_Or_LLI_Valid 位设置为 1)在每个结束时加载 ,

- 源和目标外设上的连续传输不是有效的多块传输配置。

- 如果配置参数不存在该字段 DMAX_CHx_MULTI_BLK_EN 未选中; 在这种情况下, 回读值始终为 0。

- ■ 0x0 (CONTINGUOUS):用于目标传输的连续多块传输类型 ■ 0x1 (RELOAD):重新加载用于目标传输的多块传输类型

- ■ 0x2 (SHADOW_REGISTER):用于目标传输的基于影子寄存器的多块传输类型 ■ 0x3 (LINKED_LIST):用于目标传输的基于链表的多块传输类型

- SRC_MULTBLK_TYPE:源多块传输类型。 这些位定义用于源外设的多块传输类型。 ■ 00:连续 ■ 01:重新加载 ■ 10:影子寄存器 ■ 11:链表

- 如果选择的类型是连续的,则 CHx_SAR 寄存器加载前一个块的结束源地址的值 + 1 在每个块的末尾进行多块传输。 然后启动新的块传输。

- 如果选择的类型是 Reload,CHx_SAR 寄存器在多块传输的每个块结束时从 SAR 的初始值重新加载。 然后启动新的块传输。

- 如果选择的类型是影子寄存器,如果 CHx_CTL.ShadowReg_Or_LLI_Valid 位在多块传输的每个块末尾设置为 1,则从其影子寄存器的内容加载 CHx_SAR 寄存器。 然后启动新的块传输。

- 如果选择的类型是链表,如果 CTL.ShadowReg_Or_LLI_Valid 位在多块传输的每个块末尾设置为 1,则从链表加载 CHx_SAR 寄存器。 然后启动新的块传输。

- 基于为源和目标外设编程的多块传输类型的多块传输块。CHx_CTL 和 CHx_BLOCK_TS 寄存器从它们的初始值或从它们的影子寄存器的内容(如果 CHx_CTL.ShadowReg_Or_LLI_Valid 位设置为 1)或从链表(如果 CTL.ShadowReg_Or_LLI_Valid 位设置为 1)在每个结束时加载 ,

- 源和目标外设上的连续传输不是有效的多块传输配置。

- 如果配置参数不存在该字段 DMAX_CHx_MULTI_BLK_EN 未选中; 在这种情况下, 回读值始终为 0。

- ■ 0x0 (CONTINGUOUS):用于源传输的连续多块类型 ■ 0x1 (RELOAD):重新加载用于源传输的多块类型

- ■ 0x2 (SHADOW_REGISTER):用于源传输的基于影子寄存器的多块类型 ■ 0x3 (LINKED_LIST):用于源传输的基于链表的多块类型

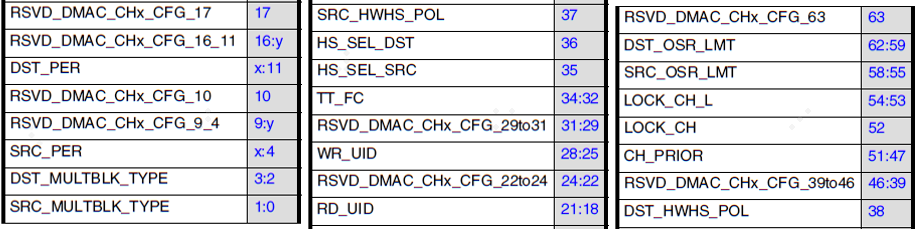

CHx_CFG2

- x:4 SRC_PER: 如果CHx_CFG. HS_SEL_SRC字段为0,将硬件握手接口(0-DMAX_NUM_HS_IF-1)传输请求信号分配给Channelx源;否则,该字段将被忽略。然后,通道可以通过指定的硬件握手接口与连接到该接口的源外设通信。

- 注意:对于正确的DW_axi_dmac操作,只能给同一个握手接口分配一个外设(源或目的)。如果配置参数DMAX_NUM_HS_IF设置为0,则该字段不存在。如果DMAC_NUM_HS_IF为1,则x = 4

- 如果DMAC_NUM_HS_IF大于1,x = ceil(log2(DMAC_NUM_HS_IF)+ 3,

- bit9:(x+1)不存在,读取时返回0。

- 36 HS_SEL_DST:目的软件或硬件握手选择。该寄存器选择(硬件或软件)握手接口对该通道上的目标请求是活动的。0:硬件握手接口。忽略软件启动的传输请求。1:软件握手接口。忽略硬件发起的传输请求。如果目标外设是内存,则忽略此位

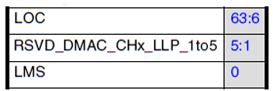

CHx_LLP(对于 x = 1;x <= DMAX_NUM_CHANNELS)

- DW_axi_dmac 通道 x 链表指针寄存器 这是链表指针寄存器。 如果启用了基于链表的块链接,则在启用通道之前,必须将该寄存器编程为指向内存中的第一个链表项 (LLI)。 该寄存器在 dma 传输的 LLI 更新阶段用链表指针的新值更新。

- ■ 偏移量:0x128 + (x-1)*0x100 ■ 存在:DMAX_NUM_CHANNELS >= x

- LOC:LLI块的起始地址存储器, 如果启用块链接,则下一个 LLI 的内存中起始地址。 不存储起始地址的六个 LSB,因为假定该地址与 64 字节边界对齐。

- LLI 访问始终使用与数据总线宽度相同的突发大小 (arsize/awsize),除此之外不能更改或编程为任何其他内容。 根据数据总线宽度选择突发长度 (awlen/arlen),以便访问不会跨越一个完整的 64 字节 LLI 结构。

- 如果突发长度不受其他设置限制,DW_axi_dmac 将在一个 AXI 突发中获取整个 LLI(40 字节)。

- LMS:LLI master Select,该位标识存储下一个链表项的内存设备所在的AXI层/接口。

- ■ 0:AXI 主机 1 ■ 1:AXI Master 2 如果配置参数 DMAX_CHx_LMS 未设置为 NO_HARDCODE,则该字段不存在。

- 在这种情况下,回读值始终是硬编码值。 该字段可读回的最大值为“DMAX_NUM_MASTER_IF-1”。

CHx_STATUSREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

- DATA_LEFT_IN_FIFO:数据留在 FIFO 中。 该位指示完成当前块传输后 DW_axi_dmac 通道 FIFO 中剩余的数据总数。 通道FIFO中的数据宽度等于CHx_CTL.SRC_TR_WIDTH。

- 对于没有错误的正常块传输完成,Data_Left_In_FIFO = 0。 如果在 dma 传输期间发生任何错误,块传输可能会提前终止,在这种情况下,Data_Left_In_FIFO 指示通道 FIFO 中剩余的数据无法传输到目标外设。

- 该字段在启用通道时清零。 注意:如果 CHx_CTL.DST_TR_WIDTH > CHx_CTL.SRC_TR_WIDTH,则 FIFO 中可能有剩余数据不足以形成一个 CHx_CTL.SRC_TR_WIDTH 数据,此时 Data_Left_In_FIFO 将返回 0。

- CMPLTD_BLK_TFR_SIZE:完成的块传输大小。该位指示为前一个块传输传输的宽度为 CHx_CTL.SRC_TR_WIDTH 的数据总数。

- 对于没有任何错误的正常块传输完成,该值将等于 CHx_BLOCK_TS 寄存器的 BLOCK_TS 字段中编程的值。

- 如果在 dma 传输期间发生任何错误,块传输可能会提前终止,在这种情况下,该值表示当前块中无错误传输的实际数据。

- 该字段在启用通道时清零。

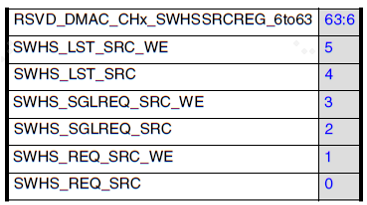

CHx_SWHSSRCREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 软件握手源寄存器 Channelx 软件握手源寄存器。

- SWHS_LST_SRC:通道源的软件握手last请求。 如果为相应通道的源选择了软件握手方法,则该位用于请求 LAST dma 源数据传输。 如果没有为 Channelx 的源启用软件握手,或者如果 Channelx 的源不是流量控制器,则忽略该位。

- CHx_SWHSSrcReg.SWHS_Req_Src 位必须设置为 1,DW_axi_dmac 才能将其视为有效的软件握手请求。

- 如果 CHx_SWHSSrcReg.SWHS_SglReq_Src 设置为 1,则最后一个请求用于 SINGLE dma 事务(AXI 突发长度 = 1),否则该请求将被视为 BURST 事务请求。

- 一旦软件读取 CHx_SWHSSrcReg.SWHS_Ack_Src 位并将其视为 1,DW_axi_dmac 会将此位清零。 软件只能将此位设置为 1; 不允许清除 此位为 0; 只有 DW_axi_dmac 可以清除该位。

- 注意:仅当相应的写使能位 SWHS_Lst_Src_WE 在同一寄存器写操作中有效且通道 x 在 DMAC_ChEnReg 寄存器中启用时,才会写入 SWHS_Lst_Src 位。 这允许软件在 CHx_SWHSSrcReg 寄存器中设置一个位,而无需执行读修改写操作。

- SWHS_SGLREQ_SRC:通道源的软件握手单一请求。如果为相应通道的源选择了软件握手方法,则该位用于请求单个(AXI 突发长度 = 1)dma 源数据传输。

- 如果没有为 Channelx 的源启用软件握手,则忽略该位。 该字段的功能取决于外设是否为流量控制器。

- 一旦软件读取,DW_axi_dmac 将该位清零 CHx_SWHSSrcReg.SWHS_Ack_Src 位并视为 1。软件只能将此位设置为 1; 不允许将该位清0; 只有 DW_axi_dmac 可以清除该位。

- 注意:仅当相应的写使能位 SWHS_SglReq_Src_WE 在同一寄存器写操作中有效且通道 x 在 DMAC_ChEnReg 寄存器中启用时,才会写入 SWHS_SglReq_Src 位。 这允许软件在 CHx_SWHSSrcReg 寄存器中设置一个位,而无需执行读修改写操作。

- ■ 0x1 (ACTIVE_SWHS_SGLREQ_SRC):源外设请求单次 dma 传输 ■ 0x0 (INACTIVE_SWHS_SGLREQ_SRC):源外设未请求单次传输

- SWHS_REQ_SRC_WE :通道源软件握手请求的写入使能位。 注:该位在回读时始终返回 0。

- ■ 0x1 (ENABLE_SWHS_REQ_SRC):允许写入 SWHS_REQ_SRC 位 ■ 0x0 (DISABLE_SWHS_REQ_SRC):禁止写入 SWHS_REQ_SRC 位

- SWHS_REQ_SRC:通道源的软件握手请求。 如果相应通道的源选择了软件握手方法,则该位用于请求 dma 源数据传输。 如果未启用软件握手,则忽略该位 Channelx 的来源。

- 该字段的功能取决于外设是否为流量控制器。 一旦软件读取 CHx_SWHSSrcReg.SWHS_Ack_Src 位并将其视为 1,DW_axi_dmac 会将此位清零。

- 软件只能将此位设置为 1; 不允许将该位清0; 只有 DW_axi_dmac 可以清除该位。

- 注意:仅当相应的写使能位 SWHS_Req_Src_WE 在同一寄存器写操作中有效且通道 x 在 DMAC_ChEnReg 寄存器中启用时,才会写入 SWHS_Req_Src 位。 这允许软件在 CHx_SWHSSrcReg 寄存器中设置一个位,而无需执行读修改写操作。

- ■ 0x1 (ACTIVE_SWHS_REQ_SRC):DMA 传输的源外设请求 ■ 0x0 (INACTIVE_SWHS_REQ_SRC):源外设未请求突发传输

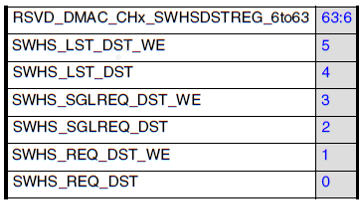

CHx_SWHSDSTREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 软件握手目标寄存器 Channelx 软件握手目标寄存器。

CHx_BLK_TFR_RESUMEREQREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 块传输恢复请求寄存器 Channelx 块传输恢复请求寄存器。 该寄存器在基于链表或影子寄存器的多块传输期间使用。

❑ 对于基于链表的多块传输,LLI.CHx_CTL 中的ShadowReg_Or_LLI_Valid 位表示从内存中取出的链表项是否有效(0:LLI 无效,1:LLI 有效)。 在注意到该位为 0 时,如果相应的通道错误中断屏蔽位设置为 0,DW_axi_dmac 会丢弃 LLI 并生成 ShadowReg_Or_LLI_Invalid_ERR 中断。此错误条件会导致 DW_axi_dmac 正常停止相应的通道。 在尝试另一个 LLI 读取操作之前,DW_axi_dmac 等待软件写入(任何值)到 CHx_BLK_TFR_ResumeReqReg 以指示有效的 LLI 可用性。

❑ 对于基于影子寄存器的多块传输,CHx_CTL 寄存器中的ShadowReg_Or_LLI_Valid 位指示影子寄存器内容是否有效(0:影子寄存器内容无效,1:影子寄存器内容有效)。 在影子寄存器获取阶段注意到该位为 0 时,DW_axi_dmac 丢弃影子寄存器内容并生成 ShadowReg_Or_LLI_Invalid_ERR 中断。 DW_axi_dmac 等待软件写入(任何值)到 CHx_BLK_TFR_ResumeReqReg 以指示有效影子寄存器可用性,然后再尝试另一个影子寄存器提取操作并继续下一个块传输。

BLK_TFR_RESUMEREQ:链表或基于影子寄存器的多块传输期间的块传输恢复请求。 ■ 0x0 (INACTIVE_BLK_TFR_RESUMEREQ):没有恢复块传输的请求 ■ 0x1 (ACTIVE_BLK_TFR_RESUMEREQ):请求恢复块传输

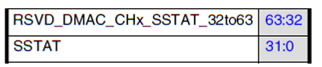

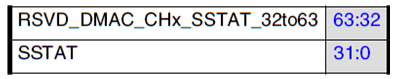

CHx_SSTAT(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 源状态寄存器,Channelx 源状态寄存器。 每个块传输完成后,硬件可以从 CHx_SSTATAR 寄存器的内容指向的地址检索源状态信息。然后,此状态信息存储在 CHx_SSTAT 寄存器中,并在下一个块开始之前写出到 LLI 的 CHx_SSTAT 寄存器位置。

仅当 DMAX_CHx_LLI_WB_EN = 1 且为通道的源或目标外设启用基于链表的多块传输时,才会将源状态写回 LLI 的 CHx_SSTAT 寄存器位置。 如果 MAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

SSTAT:源状态 硬件从 CHx_SSTATAR 寄存器的内容指向的地址检索的源状态信息。 源外设应在 CHx_SSTATAR 指向的位置更新源状态信息(如果有)以利用此功能。此状态与 DW_axi_dmac 的任何内部状态无关。 此状态与 DW_axi_dmac 的任何内部状态无关。

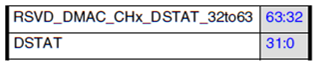

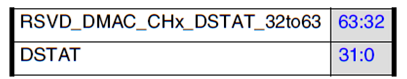

CHx_DSTAT(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 目标状态寄存器 Channelx 目标状态寄存器。 每个块传输完成后,硬件可以从 CHx_DSTATAR 寄存器的内容指向的地址检索目标状态信息。然后,此状态信息存储在 CHx_DSTAT 寄存器中,并在下一个块开始之前写出到 LLI 的 CHx_DSTAT 寄存器位置。

仅当 DMAX_CHx_LLI_WB_EN = 1 且为通道的源或目标外设启用基于链表的多块传输时,才会将目标状态写回 LLI 的 CHx_DSTAT 寄存器位置。存在:(DMAX_NUM_CHANNELS >= 1) && (DMAX_CH1_DST_STAT_EN == 1)

DSTAT: Destination Status,硬件从 CHx_DSTATAR 寄存器内容指向的地址检索到的目标状态信息。 目标外设应在 CHx_DSTATAR 指向的位置更新目标状态信息(如果有)以利用此功能。 此状态与 DW_axi_dmac 的任何内部状态无关。

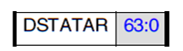

CHx_DSTATAR(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x目标状态获取寄存器

Channelx 目标状态获取寄存器。 完成每个块传输后,硬件可以从 CHx_SSTATAR 寄存器的内容指向的用户定义地址检索目标状态信息。 您可以选择系统内存中提供 64 位值的任何位置来指示目标传输的状态。

如果 DMAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

DSTATAR:源状态获取地址 硬件可以从中获取目标状态信息的指针, 对于通道的源或目标外设, 如果 DMAX_CHx_LLI_WB_EN = 1 并且启用了基于链表的多块传输,则该指针在 CHx_SSTAT 寄存器中寄存并在下一个块开始之前写到 LLI 的 CHx_DSTAT 寄存器位置。

目标外设应在 CHx_DSTATAR 指向的位置更新目标状态信息(如果有)以利用此功能。 此状态与 DW_axi_dmac 的任何内部状态无关。

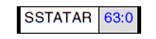

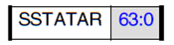

CHx_SSTATAR(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 源状态获取寄存器

Channelx 源状态获取寄存器。 完成每个块传输后,硬件可以从 CHx_SSTATAR 寄存器的内容指向的用户定义地址检索源状态信息。 您可以选择系统内存中提供 64 位值的任何位置来指示源传输的状态。

如果 DMAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

SSTATAR:源状态获取地址 硬件可以从中获取源状态信息的指针,对于通道的源或目标外设,如果 DMAX_CHx_LLI_WB_EN = 1 并且启用了基于链表的多块传输,则该指针在 CHx_SSTAT 寄存器中注册并在下一个块开始之前写到 LLI 的 CHx_SSTAT 寄存器位置 。

源外设应在 CHx_SSTATAR 指向的位置更新源状态信息(如果有)以利用此功能。 此状态与 DW_axi_dmac 的任何内部状态无关。

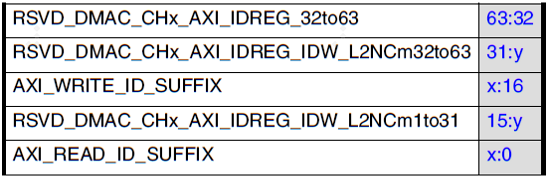

CHx_AXI_IDREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x AXI ID 寄存器 Channelx AXI ID 寄存器。 该寄存器仅在通道禁用时才允许更新,这意味着它在整个 DMA 传输过程中保持不变。

注意:该寄存器的存在由 DMAC_M_ID_WIDTH 和 DMAC_NUM_CHANNELS 配置参数。

❑ 如果为任何通道启用 LLI,则寄存器仅在以下情况下存在:DMAX_M_ID_WIDTH - (log2(DMAC_NUM_CHANNELS) +1) > 0

❑ 否则:DMAX_M_ID_WIDTH - log2(DMAC_NUM_CHANNELS) > 0

■ 存在:(DMAX_NUM_CHANNELS >= 1) && (DMAX_AXI_ID_SUFFIX_WIDTH != 0)

AXI_WRITE_ID_SUFFIX:AXI 写 ID 后缀。这些位构成 AXI3/AXI4 主接口的 AWID 输出的一部分。 IDW = DMAX_M_ID_WIDTH;L2NC = log2(DMAX_NUM_CHANNELS) 。awidN 的 L2NC+1 高位是从当前访问主接口的通道号导出的。 这因 LLI 获取和源数据传输而异。 对于源数据传输,awidN for channel1 4'b0000, awidN 对于 channel8 4'b0111 等等。 对于 LLI 获取访问,awidN 用于通道 1 4'b1000,awidN 用于 channel8 4'b1111 等等。 低位与 CHx_AXI_IDReg.AXI_Write_ID_Suffix 字段中编程的值相同。

AXI_READ_ID_SUFFIX:AXI Read ID Suffix,这些位组成了 AXI3/AXI4 主接口的 ARID 输出的一部分。 IDW = DMAX_M_ID_WIDTH;L2NC = log2(DMAX_NUM_CHANNELS) 。aridN的高L2NC+1位取自当前访问主接口的通道号。 这因 LLI 获取和源数据传输而异。 对于源数据传输,aridN 用于 channel1 4'b0000,aridN 用于 channel8 4'b0111 等等。 对于 LLI 获取访问,aridN 用于通道 1 4'b1000,aridN 用于通道 8 4'b1111 等等。 低位与 CHx_AXI_IDReg.AXI_Read_ID_Suffix 字段中编程的值相同。

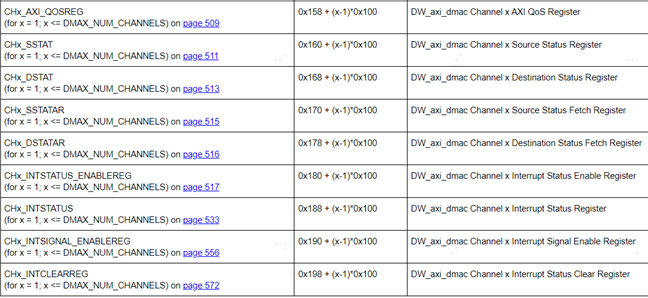

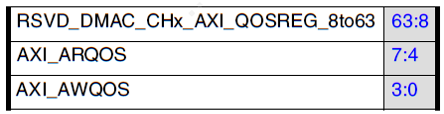

CHx_AXI_QOSREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x AXI QoS 寄存器 ,Channelx AXI QOS 寄存器。 该寄存器仅在通道禁用时才允许更新,这意味着它在整个 DMA 传输过程中保持不变。

AXI_ARQOS:AXI ARQOS。 这些位形成 AXI4 主接口的 arqos 输出。 复位后的值:0x0

AXI_AWQOS:AXI AWQOS。 这些位形成 AXI4 主接口的 awqos 输出。 复位后的值:0x0

CHx_SSTAT(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac Channel x Source Status Register,Channelx源状态寄存器。 每个块传输完成后,硬件可以从 CHx_SSTATAR 寄存器的内容指向的地址检索源状态信息。 然后,此状态信息存储在 CHx_SSTAT 寄存器中,并在下一个块开始之前写出到 LLI 的 CHx_SSTAT 寄存器位置。

仅当 DMAX_CHx_LLI_WB_EN = 1 且为通道的源或目标外设启用基于链表的多块传输时,才会将源状态写回 LLI 的 CHx_SSTAT 寄存器位置。 如果 DMAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

SSTAT:Source Status, 硬件从 CHx_SSTATAR 寄存器的内容指向的地址检索到的源状态信息。 源外设应在 CHx_SSTATAR 指向的位置更新源状态信息(如果有)以利用此功能。此状态与 DW_axi_dmac 的任何内部状态无关。 此状态与 DW_axi_dmac 的任何内部状态无关。

CHx_DSTAT(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 目标状态寄存器,Channelx 目标状态寄存器。 每个块传输完成后,硬件 可以从 CHx_DSTATAR 寄存器的内容指向的地址检索目标状态信息。 然后,此状态信息存储在 CHx_DSTAT 寄存器中,并在下一个块开始之前写出到 LLI 的 CHx_DSTAT 寄存器位置。

仅当 DMAX_CHx_LLI_WB_EN = 1 且为通道的源或目标外设启用基于链表的多块传输时,才会将目标状态写回 LLI 的 CHx_DSTAT 寄存器位置。

DSTAT:目的Status, 硬件从 CHx_DSTATAR 寄存器的内容指向的地址检索到的目的状态信息。 目标外设应在 CHx_DSTATAR 指向的位置更新目的状态信息(如果有)以利用此功能。此状态与 DW_axi_dmac 的任何内部状态无关。

SSTATAR(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 源状态获取寄存器 ,Channelx 源状态获取寄存器。 每次块传输完成后,硬件可以从 CHx_SSTATAR 寄存器的内容指向的用户定义地址检索源状态信息。

可以选择系统内存中提供 64 位值的任何位置来指示源传输的状态。 如果 DMAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

■ 存在:(DMAX_NUM_CHANNELS >= 1) && (DMAX_CH1_SRC_STAT_EN == 1)

SSTATAR:源状态获取地址 硬件可以从中获取源状态信息的指针,如果 DMAX_CHx_LLI_WB_EN = 1 并且启用了基于链表的多块传输,则该指针在 CHx_SSTAT 寄存器中注册并在下一个块开始之前写到 LLI 的 CHx_SSTAT 寄存器位置 对于通道的源或目标外设。 源外设应在 CHx_SSTATAR 指向的位置更新源状态信息(如果有)以利用此功能。 此状态与 DW_axi_dmac 的任何内部状态无关。

DSTATAR(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 目的状态获取寄存器 ,Channelx 目的状态获取寄存器。 每次块传输完成后,硬件可以从 CHx_DSTATAR 寄存器的内容指向的用户定义地址检索目的状态信息。

可以选择系统内存中提供 64 位值的任何位置来指示目的传输的状态。 如果 DMAC_CHx_SRC_STAT_EN 设置为 False,则该寄存器不存在; 在这种情况下,回读值始终为 0。

■ 存在:(DMAX_NUM_CHANNELS >= 1) && (DMAX_CH1_DST_STAT_EN == 1)

DSTATAR:目的状态获取地址 硬件可以从中获取目的状态信息的指针,如果 DMAX_CHx_LLI_WB_EN = 1 并且启用了基于链表的多块传输,则该指针在 CHx_DSTAT 寄存器中寄存并在下一个块开始之前写到 LLI 的 CHx_DSTAT 寄存器位置 对于通道的源或目标外设。 目标外设应在 CHx_DSTATAR 指向的位置更新目标状态信息(如果有)以利用此功能。 此状态与 DW_axi_dmac 的任何内部状态无关。

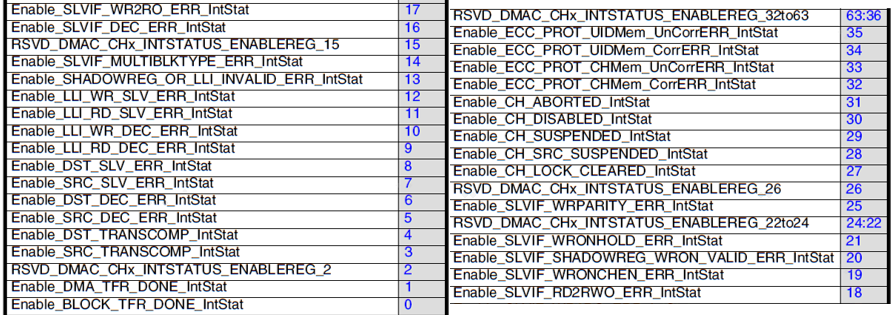

CHx_INTSTATUS_ENABLEREG(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 中断状态启用寄存器,向特定字段写入1 可在Channelx 中断状态寄存器(CH1_IntStatusReg) 中生成相应的中断状态。

■ 存在:DMAX_NUM_CHANNELS >= 1

CHx_INTSTATUS(对于 x = 1;x <= DMAX_NUM_CHANNELS)

DW_axi_dmac 通道 x 中断状态寄存器,Channelx 中断状态寄存器捕获 Channelx 特定中断 ■ 存在:DMAX_NUM_CHANNELS >= x

ECC_PROT_UIDMem_UnCorrERR_IntStat:通道 x UID 内存接口 ECC 保护相关的不可纠正错误中断状态位。 如果在 UID 内存接口数据上检测到 ECC 不可纠正错误,则会发生此错误。

- ■ 0:没有通道x UID 内存接口不可纠正的错误。 ■ 1:检测到通道x UID 内存接口无法纠正的错误。

- 如果 CHx_INTSTATUS_ENABLEReg 寄存器中相应的状态启用位设置为 1,则会生成错误中断状态。在将 1 写入 CHx_IntClearReg 中相应的中断清除位时,该位会被清除为 0。

- ■ 0x1 (ACTIVE_EccPROT_UIDMem_UnCorrERR):检测到通道 x UID 内存接口无法纠正的错误 ■ 0x0 (INACTIVE_EccPROT_UIDMem_UnCorrERR):未检测到通道 x UID 内存接口不可纠正错误

ECC_PROT_UIDMem_CorrERR_IntStat:通道 x UID 内存接口 ECC 保护相关的可纠正错误中断状态位。 如果在 UID 内存接口数据上检测到 ECC 可纠正错误,则会发生此错误。

- ■ 0:没有通道x UID 内存接口可纠正的错误。 ■ 1:检测到通道x UID 内存接口可纠正错误。

- 如果 CHx_INTSTATUS_ENABLEReg 寄存器中相应的状态启用位设置为 1,则会生成错误中断状态。在将 1 写入 CHx_IntClearReg 中相应的中断清除位时,该位会被清除为 0。

- ■ 0x1 (ACTIVE_EccPROT_UIDMem_CorrERR):检测到通道 x UID 内存接口可纠正错误 ■ 0x0 (INACTIVE_EccPROT_UIDMem_CorrERR):未检测到通道 x UID 内存接口可纠正错误

ECC_PROT_CHMem_UnCorrERR_IntStat:通道 x FIFO 存储器接口 ECC 保护相关的不可纠正错误中断状态位。 如果在 FIFO 内存接口数据上检测到 ECC 不可纠正错误,则会发生此错误。

- ■ 0:没有通道x FIFO 内存接口不可纠正的错误。 ■ 1:检测到通道x FIFO 存储器接口不可纠正的错误。

- 如果 CHx_INTSTATUS_ENABLEReg 寄存器中相应的状态启用位设置为 1,则会生成错误中断状态。在将 1 写入 CHx_IntClearReg 中相应的中断清除位时,该位会被清除为 0。

- ■ 0x1 (ACTIVE_EccPROT_CHMem_UnCorrERR):检测到通道 x FIFO 存储器接口无法纠正的错误 ■ 0x0 (INACTIVE_EccPROT_CHMem_UnCorrERR):未检测到通道 x FIFO 内存接口不可纠正错误

ECC_PROT_CHMem_CorrERR_IntStat:通道 x FIFO 存储器接口 ECC 保护相关的可纠正错误中断状态位。 如果在 FIFO 存储器接口数据上检测到 ECC 可纠正错误,则会发生此错误。

- ■ 0:没有通道x FIFO 内存接口可纠正的错误。 ■ 1:检测到通道x FIFO 内存接口可纠正错误。

- 如果 CHx_INTSTATUS_ENABLEReg 寄存器中相应的状态启用位设置为 1,则会生成错误中断状态。在将 1 写入 CHx_IntClearReg 中相应的中断清除位时,该位会被清除为 0。

- ■ 0x1 (ACTIVE_EccPROT_CHMem_CorrERR):检测到通道 x FIFO 内存接口可纠正错误 ■ 0x0 (INACTIVE_EccPROT_CHMem_CorrERR):未检测到通道 x FIFO 内存接口可纠正错误

CH_ABORTED_IntStat:通道中止。 这向软件表明 DW_axi_dmac 中的相应通道已中止。

- ■ 0:通道未中止 ■ 1:通道中止 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。

- 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

- ■ 0x1 (ACTIVE_CH_ABORTED):通道中止 ■ 0x0 (INACTIVE_CH_ABORTED):通道未中止

CH_LOCK_CLEARED_IntStat:通道锁定已清除。 这向软件表明 DW_axi_dmac 中的相应通道被清除。

- ■ 0:频道锁定未清除。 ■ 1:通道锁定被清除。 在以下情况下,DW_axi_dmac 会清除通道锁定:

- ■ 如果DW_axi_dmac 根据软件请求禁用通道,则清除通道锁定并重置CHx_CFG 寄存器中的通道锁定设置。

- ■ 如果DW_axi_dmac 在主接口上收到错误响应后禁用通道,则清除通道锁定并重置CHx_CFG 寄存器中的通道锁定设置。启用通道时该位清零。

SLVIF_WRPARITY_ERR_IntStat:从接口写入奇偶校验错误。 如果在通道寄存器上执行写操作,则会发生此错误; 但写入数据未通过偶/奇奇偶校验。

- ■ 0:无从接口写入奇偶校验错误。 ■ 1:检测到从接口写入奇偶校验错误。 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。

- 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_WRONHOLD_ERR_IntStat:从接口写入暂停错误。如果对寄存器执行了非法写操作,则会出现此错误; 如果在 DW_axi_dmac 处于保持模式时对通道寄存器执行写操作,则会发生这种情况。

- ■ 0:无从属接口写入保持错误。 ■ 1:检测到从接口写入保持错误。 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_SHADOWREG_WRON_VALID_ERR_IntStat:影子寄存器写入有效错误。 如果启用基于影子寄存器的多块传输并且当 CHx_CTL.ShadowReg_Or_LLI_Valid 位为 1 时软件尝试写入影子寄存器,则会发生此错误。

- ■ 0:无从接口影子寄存器写入有效错误。 ■ 1:检测到从接口影子寄存器写入有效错误。 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。

- 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_WRONCHEN_ERR_IntStat:从接口写入通道启用错误。如果对寄存器执行了非法写操作,则会出现此错误; 如果在启用通道时对寄存器执行写操作,并且根据 DW_axi_dmac 规范不允许对相应的寄存器执行写操作,则会发生这种情况。

- ■ 0:无从接口写入通道启用错误。 ■ 1:检测到从接口写入通道启用错误。 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_RD2RWO_ERR_IntStat:从接口只读到写错误。 如果对只写寄存器执行读取操作,则会发生此错误。

- ■ 0:没有从属接口只读到只写错误。 ■ 1:检测到从接口只读到写入错误。 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。

- 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_WR2RO_ERR_IntStat:从接口写入只读错误。 如果对只读寄存器执行写操作,则会发生此错误。

- ■ 0:没有从接口写入只读错误。 ■ 1:检测到从接口写入只读错误。

- 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_DEC_ERR_IntStat:从接口解码错误。 寄存器访问期间 DW_axi_dmac 生成的解码错误。如果寄存器访问是对 Channelx 寄存器空间中的无效地址,导致 DW_axi_dmac 从接口的错误响应,则会发生此错误。

- ■ 0:无从接口解码错误。 ■ 1:检测到从接口解码错误。 如果启用 CHxINTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。

- 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SLVIF_MULTIBLKTYPE_ERR_IntStat:从接口多块类型错误。 如果在 CHx_CFG 寄存器(SRC_MLTBLK_TYPE 和 DST_MLTBLK_TYPE)中编程的多块传输类型无效,则会发生此错误。

- 此错误情况会导致 DW_axi_dmac 正常停止相应的通道; 如果相应的通道错误中断屏蔽位设置为 0 并且通道等待软件写入(任何值)到 CHx_BLK_TFR_ResumeReqReg 以指示有效的多块传输类型可用性,则会生成错误中断。

- ■ 0:无多块传输类型错误。 ■ 1:检测到多块传输类型错误。

- 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。 在向 CHx_IntClearReg 寄存器中相应的通道中断清除位写入 1 时,该位被清除为 0。

SHADOWREG_OR_LLI_INVALID_ERR_IntStat:影子寄存器或 LLI 无效错误。 如果在 DW_axi_dmac 影子寄存器/LLI 提取阶段期间 CHx_CTL.ShadowReg_Or_LLI_Valid 位被视为 0,则会发生此错误。

- 此错误情况会导致 DW_axi_dmac 正常停止相应的通道; 如果相应的通道错误中断屏蔽位设置为 0 并且通道等待软件写入(任何值)到 CHx_BLK_TFR_ResumeReqReg 以指示有效影子寄存器可用性,则会生成错误中断。

- 在 LLI 预取的情况下,即使 ShadowReg_Or_LLI_Valid 位对于预取 LLI 被视为 0,也不会生成 ShadowReg_Or_LLI_Invalid_ERR 中断。

- 在这种情况下,DW_axi_dmac 在完成当前块传输后重新尝试 LLI 提取操作 并且仅当 ShadowReg_Or_LLI_Valid 位仍被视为 0 时才会生成 ShadowReg_Or_LLI_Invalid_ERR 中断。

- ■ 0:无影子寄存器/LLI 无效错误。 ■ 1:检测到影子寄存器/LLI 无效错误。

- 如果启用 CHx_INTSTATUS_ENABLEReg 中的相应位,则会生成错误中断。