数字电路模拟程序

一、核心功能

模拟与门、或门、非门、异或门、同或门 5 种电路元件,根据输入的元件信息、引脚连接关系,计算各元件输出电平并按规则输出。

二、关键规则(输入 / 元件 / 输出)

元件规则

类型标识:A = 与门、O = 或门、N = 非门、X = 异或门、Y = 同或门

命名格式:

与 / 或门:标识 (输入引脚数)+ 编号(如 A (8) 1=8 输入与门、O (4) 2=4 输入或门)

非 / 异或 / 同或门:标识 + 编号(如 N1 = 非门、X8 = 异或门、Y4 = 同或门)

逻辑功能:

与门:全输入 1→输出 1,否则 0;或门:全输入 0→输出 0,否则 1

非门:输入反置(0→1、1→0);异或门:两输入不同→1,相同→0

同或门:两输入相同→1,不同→0

引脚:所有元件仅 1 个输出引脚(编号 0);输入引脚连续编号(如 8 输入与门引脚 1-8)

输入规则

电路输入:格式为 “INPUT: 输入 1 - 信号 1 输入 2 - 信号 2...”(如 “INPUT: A-0 B-1”,A 输入 0、B 输入 1)

连接关系:格式为 “[输出引脚 输入引脚 1 输入引脚 2...]”(如 “[A A (8) 1-1 X5-2]”,A 信号传给与门 A (8) 1 的 1 号引脚、异或门 X5 的 2 号引脚)

结束标志:输入以 “end” 结尾,之后内容忽略

连接约束:1 个输出可连多个输入,1 个输入仅能连 1 个输出;输出引脚不能互接

输出规则

顺序:先与门、再或门、然后非门、异或门、同或门

同类排序:按元件编号从小到大

忽略条件:元件输入引脚未接有效信号时,不输出该元件结果

三、程序核心逻辑

读取并解析输入(元件信息、电路输入信号、引脚连接关系)

按元件逻辑计算输出(先确认输入引脚信号是否完整,再算输出)

按规则排序并输出有效元件的输出电平

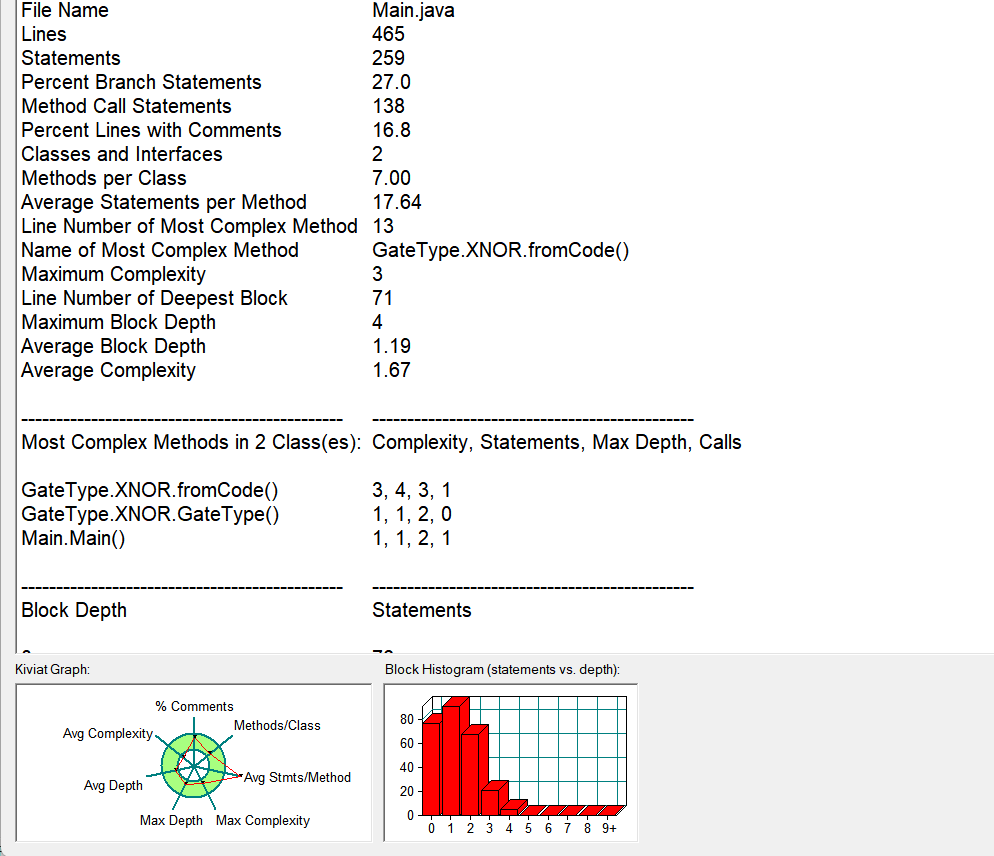

以下是代码规模:

一、方法参数特征

从整体代码结构可推断,核心方法(如门电路类型解析的GateType.XNOR.fromCode()、程序入口Main.Main()等)的参数数量较少,输入数据特征单一,无多参数、多维度输入的场景。基于此特征,在调试与测试阶段,仅需覆盖少量参数场景即可完成核心逻辑验证。

二、代码块嵌套与语句分布特征

(一)核心定义

Block Depth:代码块的嵌套层级(0 代表最外层,数值越大表示嵌套层级越深);

Statements:对应嵌套层级下的代码语句数量。

(二)分布特征

代码嵌套层级主要集中在 0-4 层(5 层及以上嵌套的语句数为 0)。其中,嵌套层级为 1 时语句数最多(90 条),表明代码以单层嵌套逻辑为主(如基础条件判断、简单循环);2 层嵌套语句数次之(67 条)。整体来看,代码嵌套逻辑简单,无过深层级的嵌套设计。

三、Main.java 核心指标补充

(一)基础结构指标

分析文件:Main.java;

代码总行数:465 行;

有效代码语句数:265 条;

包含类 / 接口数量:2 个;

平均每个类的方法数:7 个;

注释行占比:仅 2.8%,注释量极少,几乎无结构化注释。

(二)复杂度核心指标

最大复杂度:3(对应方法GateType.XNOR.fromCode());

平均复杂度:1.67;

代码块最大嵌套深度:4;

平均嵌套深度:1.19;

最复杂方法:GateType.XNOR.fromCode()(复杂度 3、语句数 4 条、嵌套深度 3 层),其余方法(如Main.Main())复杂度仅为 1。

(三)可视化补充数据

最复杂方法列表:以 “[方法名]:[复杂度,语句数,最大嵌套深度,调用数]” 格式呈现核心方法,可直观体现单方法的复杂度分布;

代码块深度分布:以数值列表展示不同嵌套层级的语句数,与前述 Block Depth 数据一致,嵌套层级 0-2 的语句占比超 80%。

四、整体结论

该代码整体逻辑极简:嵌套层级浅(最大嵌套深度 4,平均仅 1.19),核心方法GateType.XNOR.fromCode()的复杂度仅为 3,所有方法复杂度均低于 5;项目结构简单(仅 2 个类),维护成本极低,无需拆分现有逻辑。需重点关注的优化点为补充必要的结构化注释,以提升代码后续的可读性与可维护性。

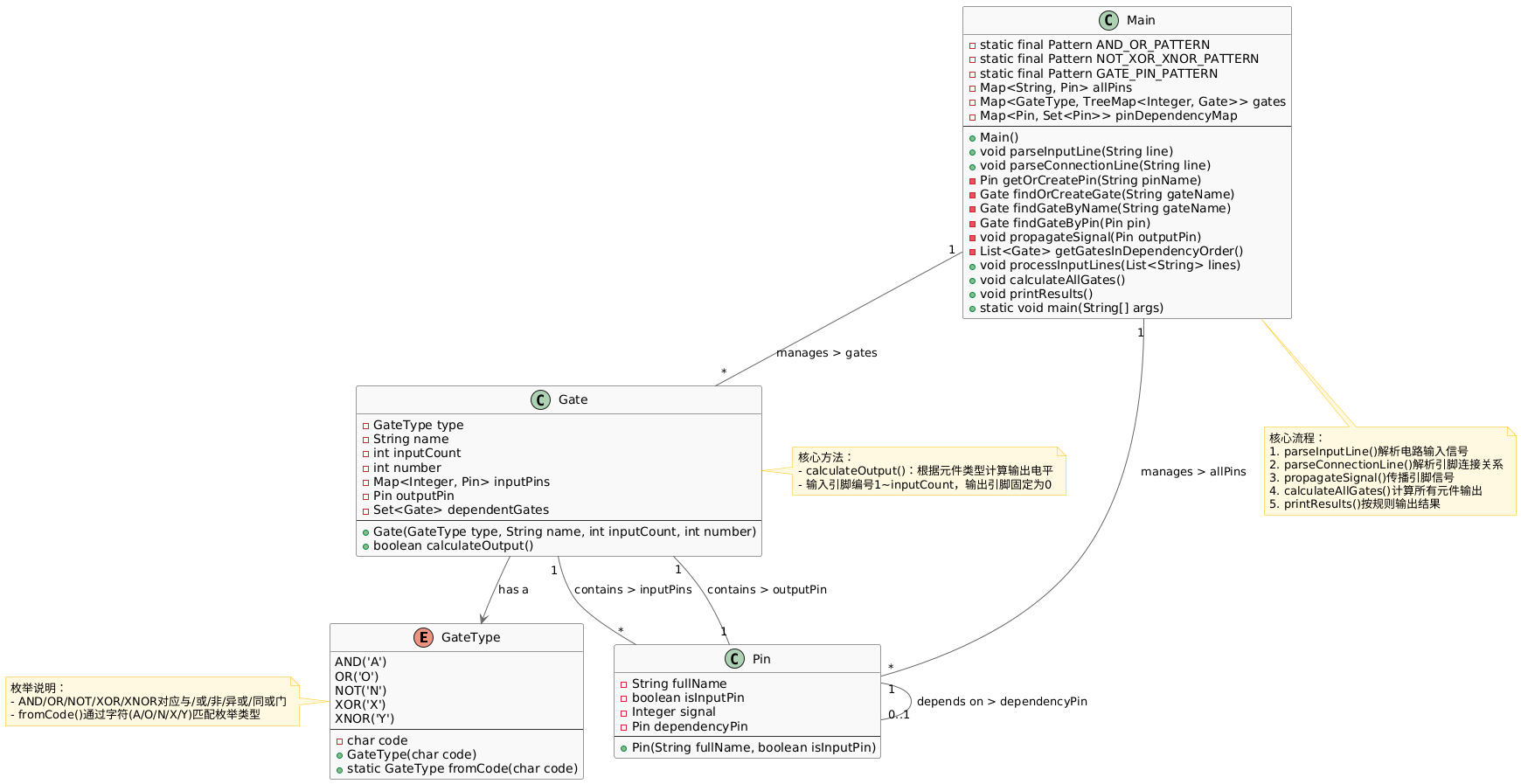

类图如下:

一、核心类与枚举设计

- GateType(枚举,标识:E)

功能定位:作为电路元件类型的枚举定义,涵盖与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)、同或门(XNOR)5 类核心电路元件,每类元件均绑定专属字符标识(例如 AND 对应字符 'A')。核心能力:提供 fromCode(char code) 方法,可依据输入字符(A/O/N/X/Y)精准匹配对应的电路元件类型,是元件类型解析的核心入口。 - Pin(类,标识:C)

功能定位:对电路中 “引脚” 的属性及依赖关联进行封装,是电路信号传递的基础载体。核心属性说明:

fullName:引脚完整命名(示例:“A (2) 1-1”“A”),用于唯一标识引脚;

isInputPin:标识该引脚是否为电路级输入引脚(区别于元件自身的输入引脚);

signal:引脚承载的信号值(0 代表低电平、1 代表高电平、null 代表信号未定义);

dependencyPin:输入引脚所依赖的输出引脚,遵循 “单输入引脚仅依赖单个输出引脚” 的关联规则。 - Gate(类,标识:C)

功能定位:封装电路元件的核心逻辑与引脚关联关系,是实现元件信号计算的核心类。核心属性说明:

type:关联 GateType 枚举,明确元件所属类型;

name:元件自定义名称(示例:“A (2) 1”“N1”);

inputCount:输入引脚数量(与 / 或门支持自定义数量,非门固定为 1,异或 / 同或门固定为 2);

number:元件编号,用于同类元件的有序排序;

inputPins:输入引脚集合(以引脚号为键、引脚对象为值的键值对形式存储);

outputPin:输出引脚(固定编号为 0)。

核心方法:calculateOutput(),依据元件所属类型(与 / 或 / 非等),结合输入引脚信号计算输出引脚的最终信号值。 - Main(类,标识:C)

功能定位:作为程序入口类,统筹管控电路输入解析、信号传播、元件逻辑计算、结果格式化输出的全流程。核心属性说明:

正则表达式(如 AND_OR_PATTERN 等):用于匹配元件名、引脚名的格式规范,保障输入解析的准确性;

allPins:全局引脚管理容器,统一维护所有引脚对象;

gates:按元件类型分组管理所有元件(基于 TreeMap 实现同类元件按编号有序排列);

pinDependencyMap:构建输出引脚到依赖其信号的输入引脚的映射关系,为信号传播提供数据支撑。

核心方法说明:

parseInputLine():解析电路输入信号,完成初始信号的赋值与引脚初始化;

parseConnectionLine():解析引脚间的连接规则,构建引脚依赖关系;

propagateSignal():将输出引脚的信号同步至所有依赖该引脚的输入引脚,实现信号层级传播;

calculateAllGates():按照元件间的依赖层级,依次计算所有元件的输出信号;

printResults():按预设规则(元件类型顺序:与→或→非→异或→同或,同类元件按编号排序)输出最终计算结果。

二、类间关联关系

Gate 与 GateType:属于 “has a”(包含)关系,Gate 类内置 GateType 类型的属性,明确每个电路元件对应的类型归属;

Gate 与 Pin:Gate 类对 Pin 类存在包含关系,具体体现为:

包含多个输入引脚(inputPins,关联描述:contains > inputPins);

包含一个输出引脚(outputPin,关联描述:contains > outputPin);

Main 与 Gate/Pin:Main 类承担全局管理角色,分别实现对所有元件(关联描述:manages > gates)和所有引脚(关联描述:manages > allPins)的统一管控;

Pin 与 Pin:输入引脚与输出引脚存在依赖关系(关联描述:depends on > dependencyPin),是信号传递的核心关联逻辑。

三、核心执行流程(基于 Main 类逻辑)

程序运行遵循固定的逻辑链路:

输入解析阶段:通过 parseInputLine() 解析电路初始输入信号,完成基础数据初始化;

依赖构建阶段:调用 parseConnectionLine() 解析引脚连接规则,建立引脚间的依赖映射;

信号传播阶段:执行 propagateSignal() 实现输出引脚信号向依赖输入引脚的同步;

逻辑计算阶段:通过 calculateAllGates() 按依赖层级完成所有元件的输出信号计算;

结果输出阶段:调用 printResults() 按指定规则输出最终的元件计算结果。

总结

该类结构体系完整复刻了数字电路模拟程序的核心设计逻辑与运行架构:以 GateType 枚举界定元件类型维度,以 Pin 类封装信号传递的基础单元,以 Gate 类落地元件的核心计算逻辑,最终通过 Main 类实现全流程的调度管控。类间关联关系清晰呈现了 “元件包含引脚、程序统一管理元件与引脚” 的核心设计思路,完整支撑了数字电路信号解析、传播、计算与输出的全链路运行。

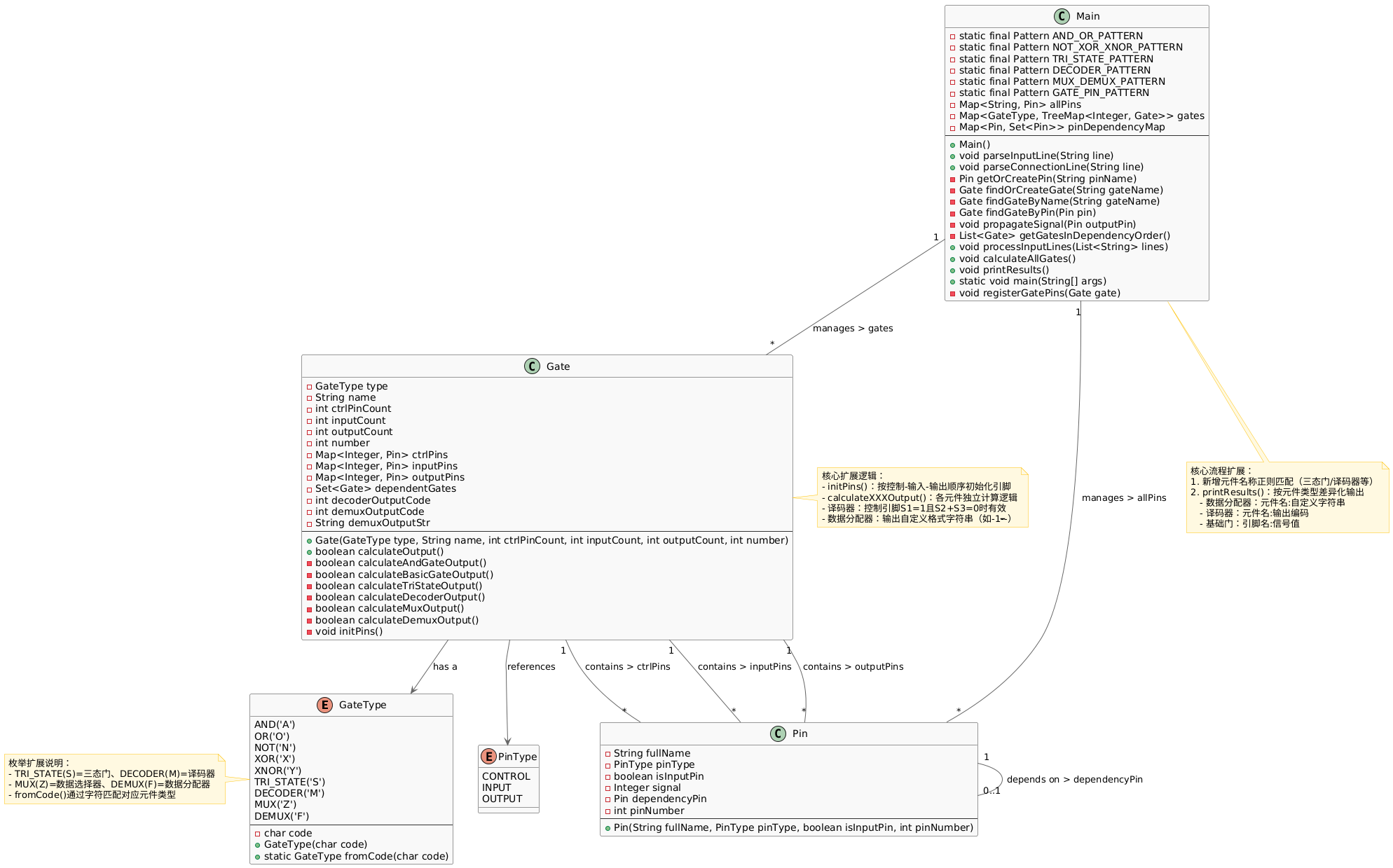

第二次作业:

作业内容:

在作业1的基础上增加要求,输入规则(新增 / 调整)

元件命名:

数据选择器 / 分配器:标识 (控制引脚数)+ 编号;译码器:标识 (输入引脚数)+ 编号;其余保持原有格式;

同类元件编号不可重复,不同类可重复(如 X4、Y4)。

引脚命名:仍为 “元件名 - 引脚号”,新增元件引脚需按 “控制 - 输入 - 输出” 顺序编号,同类型引脚按编号升序。

其他输入规则:

电路输入:INPUT: 输入名 - 信号 空格分隔(如 INPUT: A-0 B-1);

连接关系:[输出引脚 输入引脚 1 输入引脚 2...],1 输出可连多输入、1 输入仅连 1 输出;

输入以 “end” 结束,后续内容忽略。

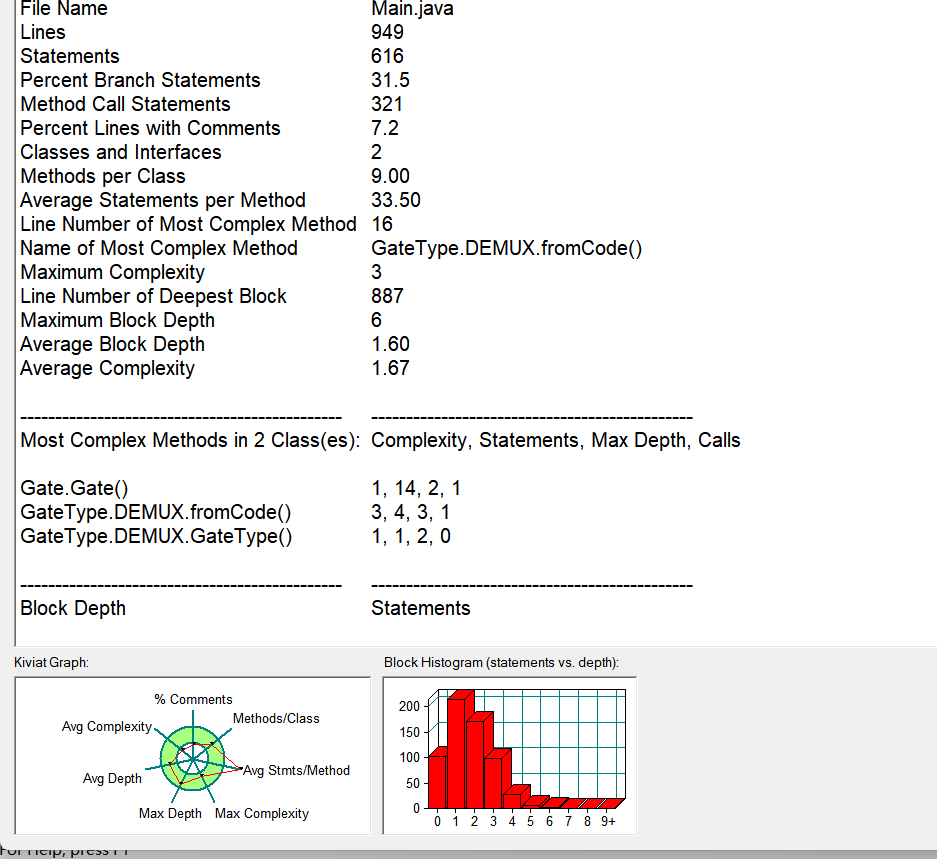

代码规模如下:

一、基础维度数据

(一)代码规模与语句构成

Main.java 文件总行数达 949 行,其中有效代码语句共计 616 条;分支类语句(if、switch 等)数量为 315 个,方法调用类语句 321 条。注释占比仅 2.2%,几乎无结构化注释内容,代码可读性完全依赖自身语法结构与逻辑排布。

(二)结构分布特征

文件内包含 2 个类 / 接口,平均每个类承载 9 个方法;方法级语句分布上,单个方法平均包含 33.5 条语句,其中复杂度最高的方法出现在代码第 16 行位置。

二、复杂度与嵌套层级分析

(一)核心复杂度指标

最大复杂度:887(对应方法为 GateType.DEMUX.fromCode());

平均复杂度:1.67,整体复杂度处于偏低水平;

代码块嵌套深度:最大嵌套层级为 6 层,平均嵌套深度 1.60 层。

(二)关键方法与嵌套分布详情

最复杂方法明细(格式:[方法名]:[复杂度,语句数,最大嵌套深度,调用数]):

GateType.DEMUX.fromCode():复杂度 3、语句数 4 条、嵌套深度 3 层;

Gate.Gate():复杂度 1、语句数 14 条、嵌套深度 2 层;

其余方法复杂度均≤3,核心逻辑简洁易懂。

代码块嵌套深度语句分布:

嵌套深度 0(无嵌套):102 条语句;

嵌套深度 1(单层嵌套,如基础 if 判断、for 循环):213 条语句;

嵌套深度 2:170 条语句;

嵌套深度≥6 时:语句数极少(≤5 条),无因过深嵌套引发的逻辑冗余或混乱问题。

三、整体结论与优化建议

(一)核心特征总结

代码规模与可读性:文件总行数达 949 行,属于规模较大的代码文件,但注释占比仅 2.2%,缺乏必要的注释说明,易增加后续理解与维护成本;

复杂度分布:核心方法 GateType.DEMUX.fromCode() 复杂度数值偏高(887),但其余方法复杂度均≤3,整体逻辑简单;

嵌套层级:代码块嵌套主要集中在 0-3 层,最大嵌套深度为 6 层,未出现因过深嵌套导致的逻辑混乱问题;

结构特征:整体代码结构清晰,仅包含 2 个类,无冗余的类层级设计。

(二)优化方向

重点优化 GateType.DEMUX.fromCode() 方法的复杂度,可通过拆解逻辑、简化条件判断等方式降低复杂度,提升方法的可维护性;

补充结构化注释,针对核心方法、关键逻辑分支、特殊业务规则等添加注释说明,改善代码可读性;

虽无过深嵌套问题,但可对 2-3 层嵌套的核心逻辑进行梳理,进一步简化嵌套结构,提升代码简洁性。

以下是类图:

浙公网安备 33010602011771号

浙公网安备 33010602011771号