计算机组成原理(二)

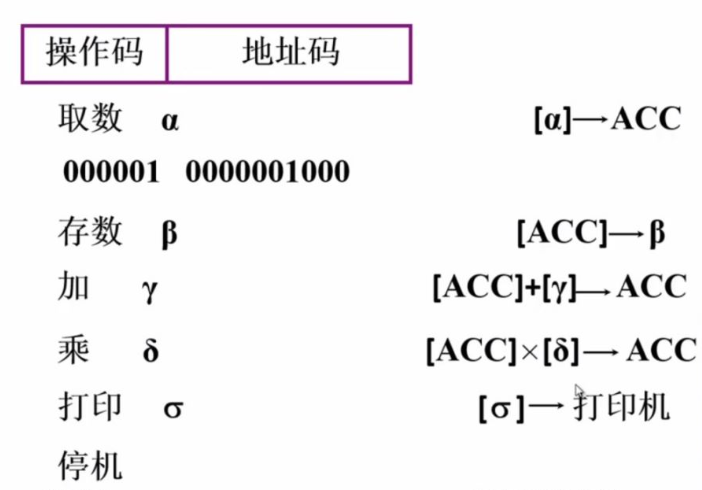

指令格式举例

[]的意思为取出内存地址中对应的值

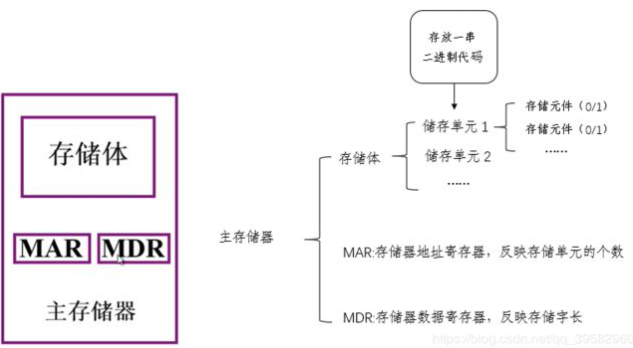

存储器的基本组成

指令和数据都是保存在存储器中的

存储体 ― 存储单元 – 存储元件 (0/1)

大楼 – 房间 - 床位 (无人/有人)

存储单元:存放一串二进制代码

存储字: 存储单元中二进制代码的组合

存储字长:存储单元中二进制代码的位置

按地址寻访

MAR(Memory Address Register):存储器地址寄存器,反映存储单元的个数

MDR(Memory Data Register):存储器数据寄存器,反映存储字长

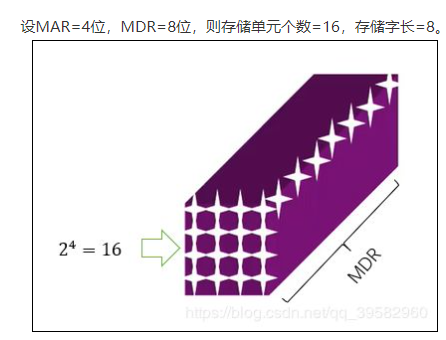

再用个例子来说明下:

比如有32个存储单元,而存储单元的地址是用二进制来表示的,那么5位二进制数就可以32个存储单元。那么,MAR的位数就是5位。

在实际运用中,我们 知道了MAR的位数,存储单元的个数也可以知道了。

MDR 存放的是从存储元件读出,或者要写入某存储元件的数据(二进制数)。

如果 MDR=16,,每个存储单元进行访问的时候,数据是16位,那么存储字长就是16位。

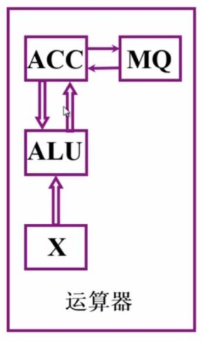

运算器的基本组成及操作过程

ACC(Accumulator): 累加器,运算器中运算前存放操作数、运算后存放运算结果的寄存器;

ALU (Arithmetic and Logic Unit): 算术逻辑运算单元,运算器中完成算术逻辑运算的逻辑部件;

MQ (Multiplier-Quotient Register):乘商寄存器,乘法运算时存放乘数、除法时存放商的寄存器

X: 此字母没有专指的缩写含义,可以用作任一部件名,在此表示操作数寄存器,即运算器中工作寄存器之一,用来存放操作数;

参考:https://blog.csdn.net/qq_42712280/article/details/104969936

| ACC | MQ | X | |

|---|---|---|---|

| 加法 | 被加数,和 | 加数 | |

| 减法 | 被减数,差 | 减数 | |

| 乘法 | 乘积高位 | 乘数,乘积低位 | 被乘数 |

| 除法 | 被除数,余数 | 商 | 除数 |

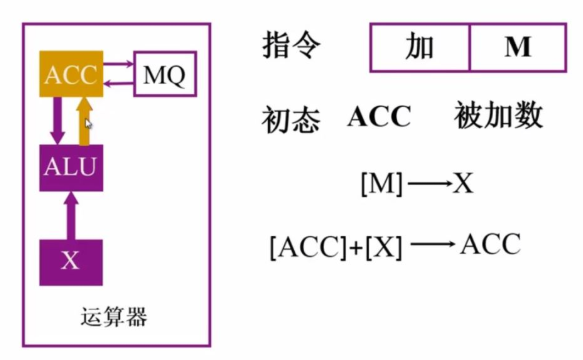

加法操作过程

加法操作指令由累加操作码和被加数的地址M构成

首先在加法操作之前,ACC 中已经保存了另一个加数,或者说之前运算得到的结果

加法操作其实是一个累加指令,即对 ACC 中已有的结果,累加地址M处的数据

执行加法操作时,将存储器地址为 M 处的数据取出放入 X寄存器 中,随后 ALU 执行加法操作将 ACC 和 X寄存器 中的数据累加,结果覆盖放入 ACC 中

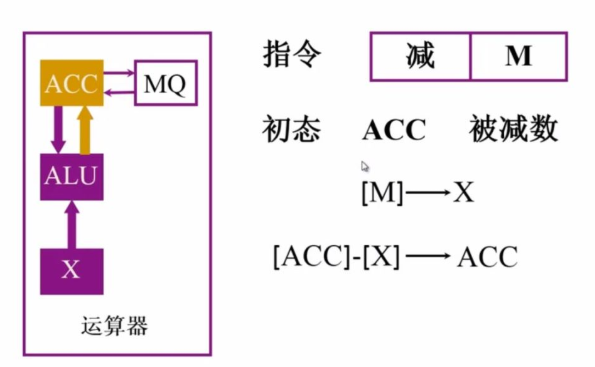

减法操作过程

减法操作指令由累减操作码和被减数地址M组成

和加法操作一样,减法操作也是一个累减指令,即对ACC中已有的结果累减地址M处的数据

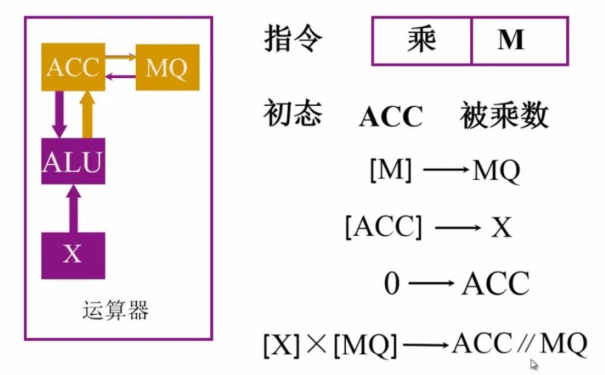

乘法操作过程

乘法操作由累乘操作码和乘数的地址M组成

乘法操作也是一个累乘过程,对ACC中已有的结果,累乘地址M处的数据

乘法操作是通过移位和累加完成的,累加保存结果的操作需要通过ACC实现,真正开始乘法之前,我们会将乘数读取到MQ中,之后将ACC中的已有结果给到X中,再对ACC清0(累加初始化)

并且由于积的位数会比乘数长,因而我们还需要MQ辅助保存乘积的低位结果

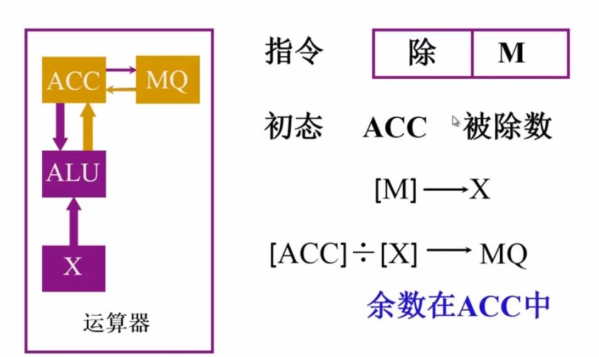

除法操作过程

除法操作由累除操作码和被除数的地址M组成

除法操作也是一个累除过程,对ACC中已有的结果,累除地址M处的数据

除法操作是通过位移和减法实现的,ACC中已有的结果作为被除数,除数被读取到X中,此时就需要MQ来保存商,我们会逐位试减决定每位上0或是上1,从而组合出商的结果,ACC中的被除数则会被累减变为余数

浙公网安备 33010602011771号

浙公网安备 33010602011771号