单片机基础(一):外部引脚及总线接口

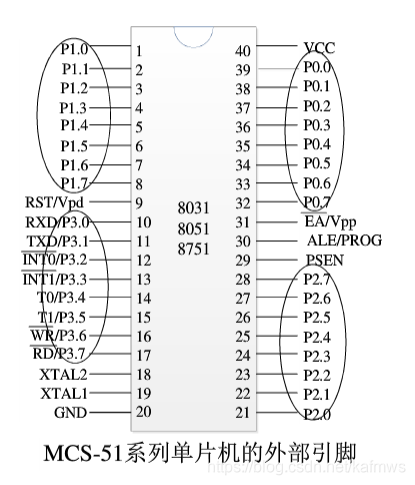

51单片机外部引脚

如上图,从左至右,从上到下,32个引脚每八个一组,分别称为P1口,P0、P3、P2口

输入输出引脚

P0口(39 ~ 32脚):即P0.0 ~ P0.7,通常作为双向I/O口,在接有片外存储器或扩展I/O口时,P0口分时复用为低八位地址总心啊和双向数据总线

P1口(1 ~ 8脚):即P1.0 ~ P1.7,作为双向I/O口使用

P2口(21 ~ 28脚):即P2.0 ~ P2.7,通常作为双向I/O口使用,在扩展片外存储器时,P2口用作高8位地址总线

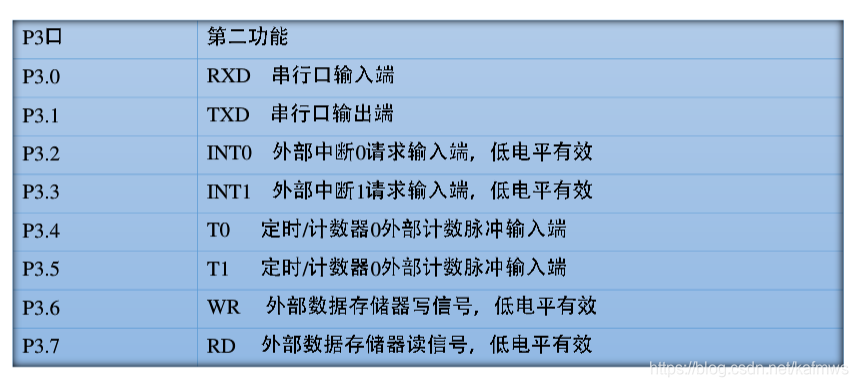

P3口(10 ~ 17脚):即P3.0 ~ P3.7,除作为双向I/O口使用外,每一位都可由于第二功能

控制引脚

1.ALE(Adress Lock Enable)30脚:地址锁存信号输出端,用于接外部存储器时,与外部锁存器配合,将复用的地址数据总线功能分离

2.PSEN——(Peripherals Select Enable)29脚:片外程序存储器选通信号输出端

3.RST(Reset)9脚:当单片机振荡器工作时,该引脚上出现持续10ms以上的高电平,就可实现复位操作,使单片机回复到初始状态

4.EA 31脚:EA为片外程序存储器选用端,该引脚低电平时,选用片外程序存储器,高电平或悬空时选用片内程序存储器

主电源引脚

VCC(40脚):接+5V电源

GND(20脚):接地

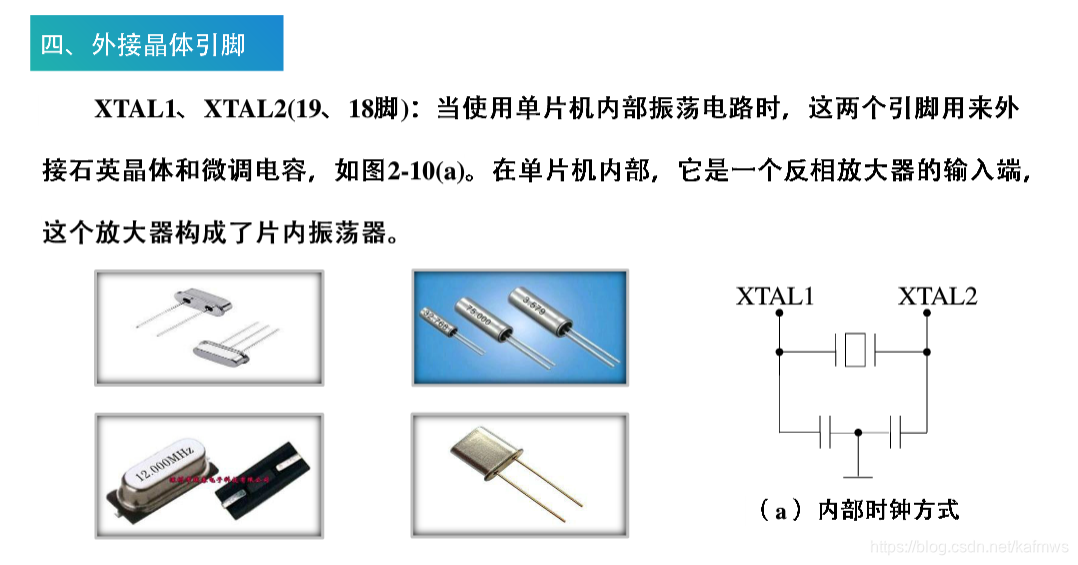

那么还剩下18、19两个引脚,XTAL2和XTAL1,

18、19脚是片内震荡电路的输出与输入端,或使用外部电路,XTAL1接地,外部时钟信号从XTAL2(18脚)接入

单片机基础(三)时钟系统与复位

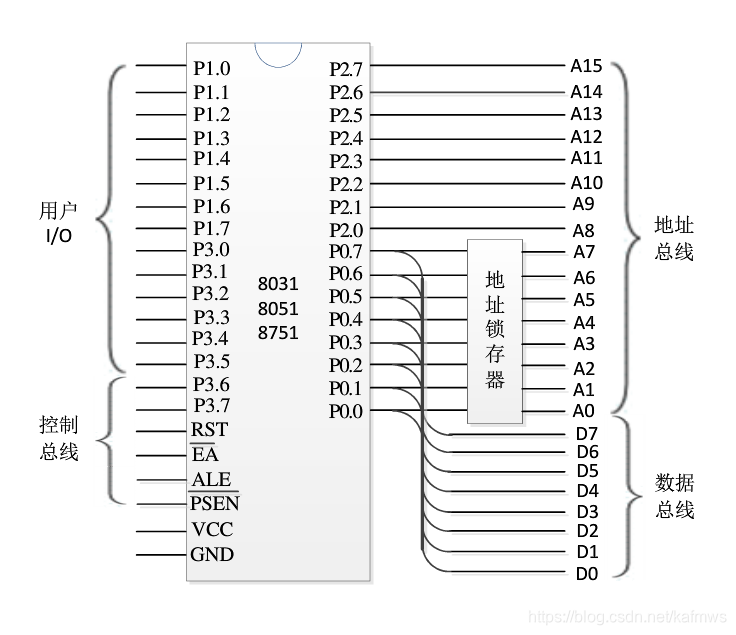

按总线方式理解的总线接口

即P0口发挥地址/数据总线分时复用功能,与外部地址锁存器结合(总线分时复用,所以需要保存地址),作数据总线和低八位地址总线,P2口作高八位地址总线,P3.6、P3.7加四条控制引脚作控制总线,P1口和剩余的P3引脚作外部I/O口

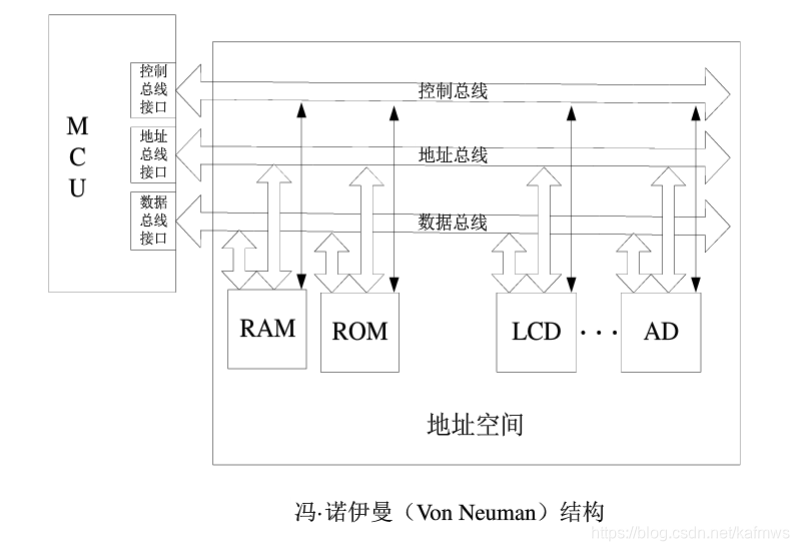

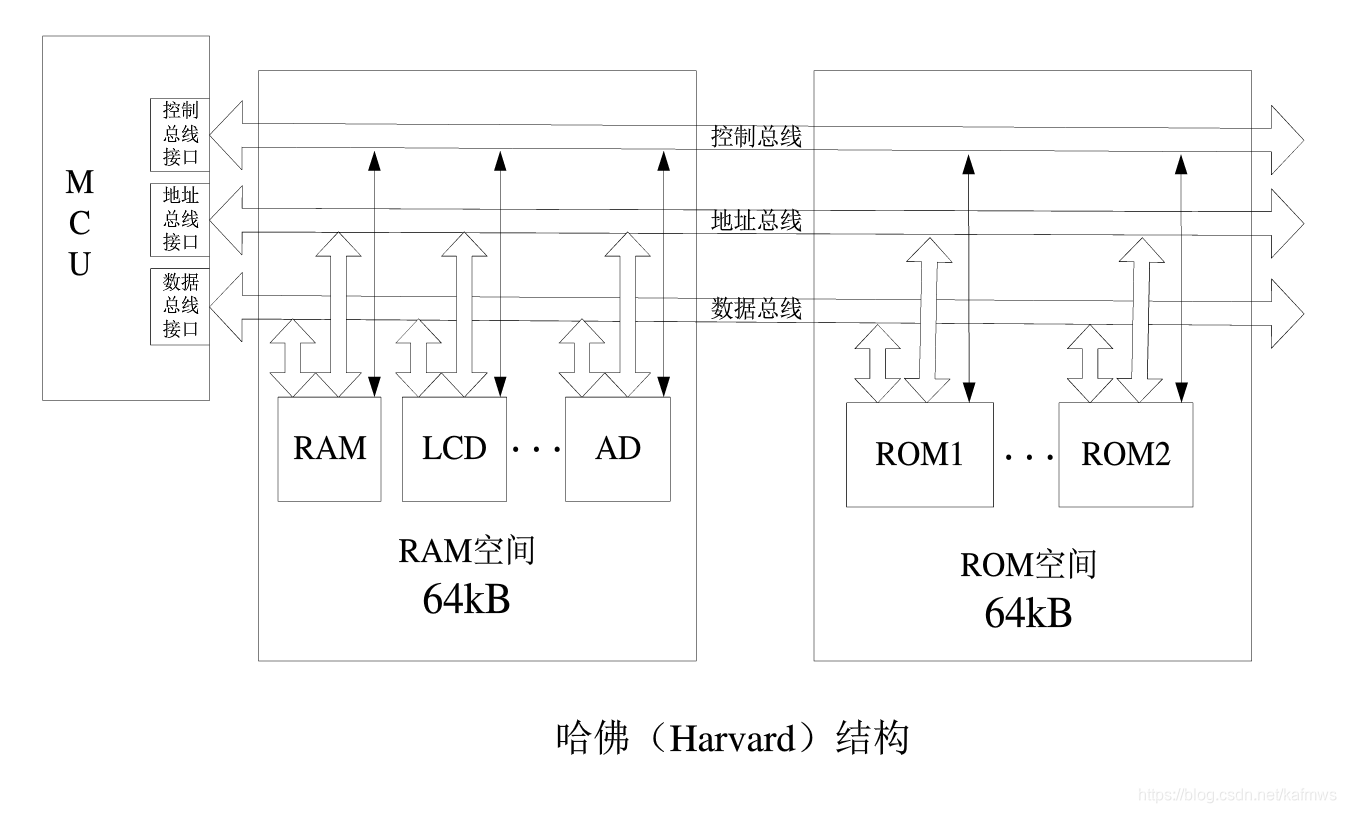

冯·诺依曼结构和哈佛结构

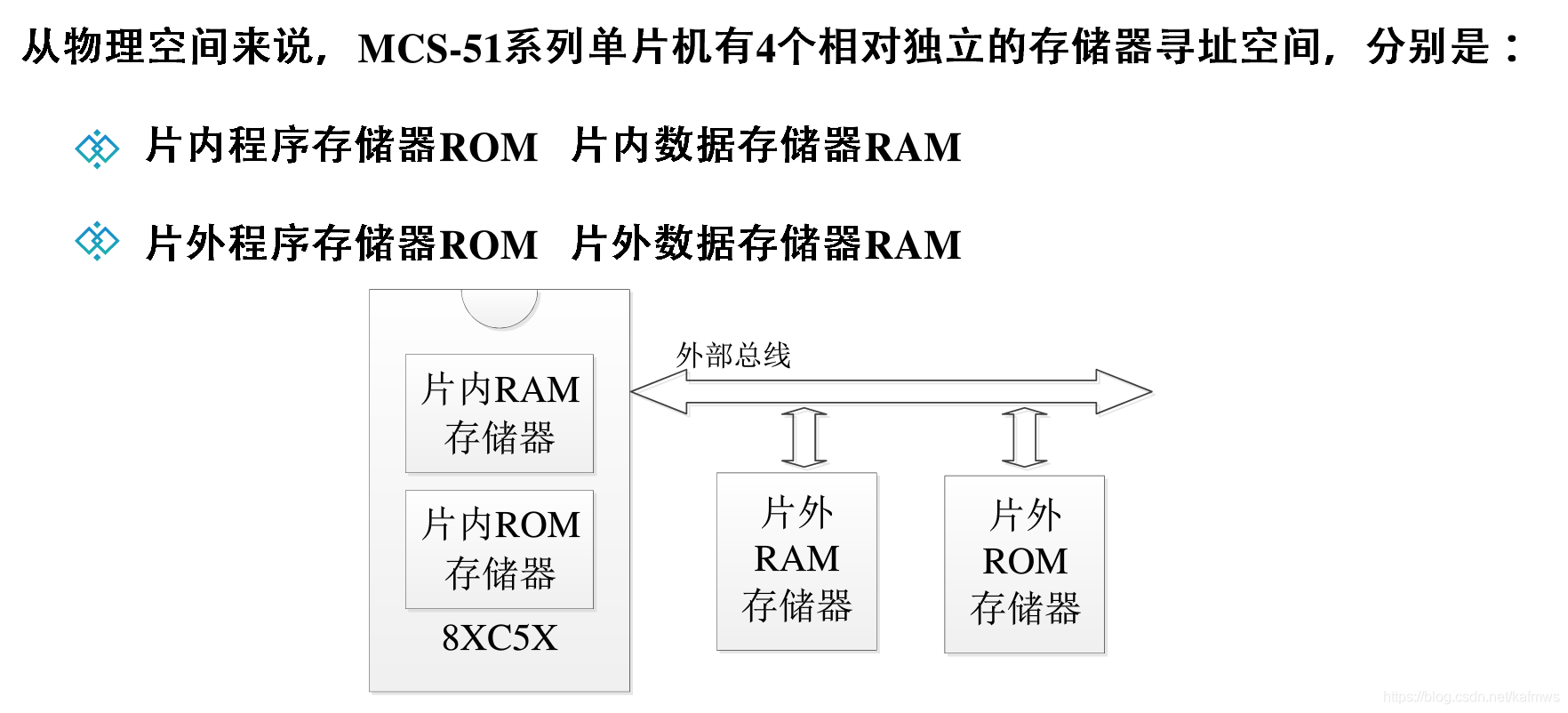

两种结构的区别:CPU的外部程序存储器ROM空间和数据存储器RAM空间是否共用一个地址空间

冯·诺依曼结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数懂事通过一条总线分时进行

当进行高速运算时,该结构不但不能同时取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢

哈佛结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大提高了数据处理能力和指令的执行速度,非常适合实时的数字信号处理

2019/2/24

浙公网安备 33010602011771号

浙公网安备 33010602011771号