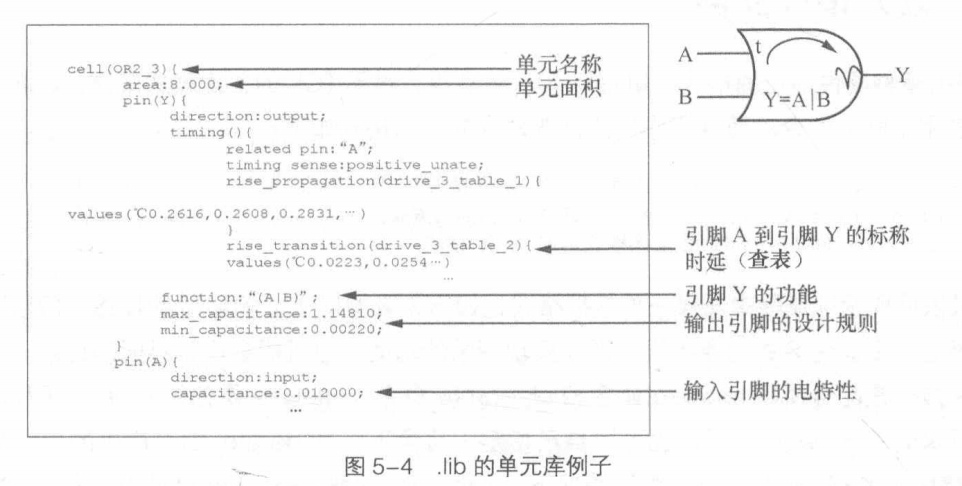

一、DC综合中需要用到的库材料

2、link_library( .db )

3、symbol_library( .sdb )

4、IP库( .sldb )

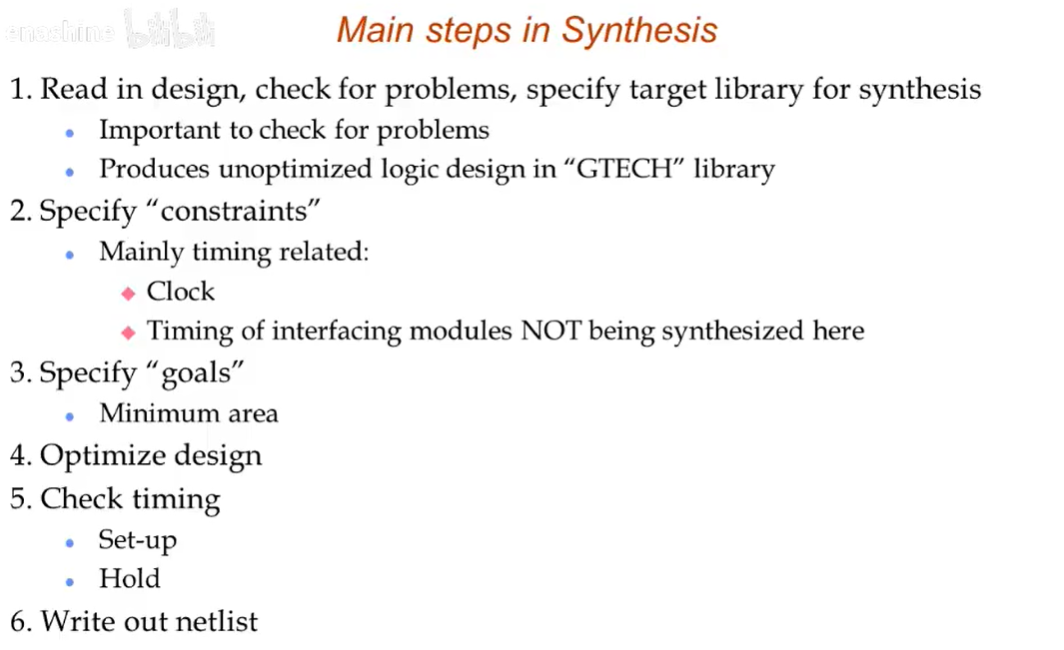

二、综合流程——转译、优化、映射

1、读入设计,检查问题,确定综合目标库文件

使用 read_verilog $active_design.v读入设计,直接转换为内部数据库,不经过GTECH;也行采用analyze+elaborate组合读入设计,如:

> set PRJ_DIR. /

> set_app_var search_path [ list $PRJ_DIR/rtl $PRJ_DIR/lib ]

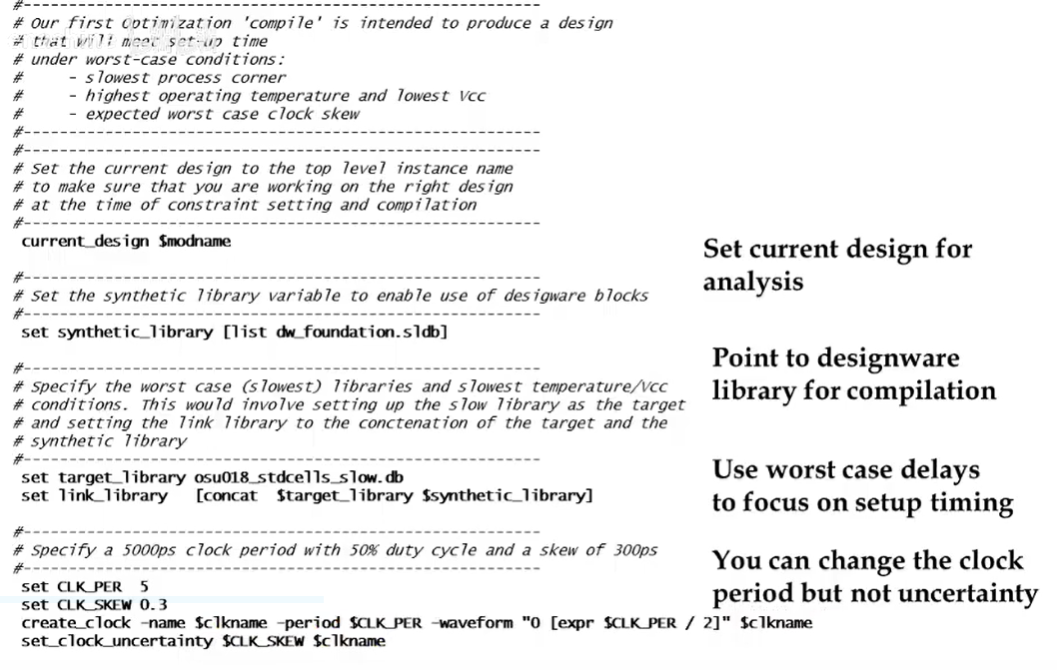

>set_app_var synthetic_library { mydesign.sldb }

> set_app_var target_library {scc018_ss.db }

(运用最坏情况工艺角检查建立时间违规)

> set_app_var link_library { list * scc018_ss.db scc018_IO.db macro.db}

(其中 * 表示已经加载到DC内存中的库,如DesignWare组件和通过analyze加载的设计等)

> analyze -formate verilog Top.v

> elaborate Top

通过analyze主要进行语法检查、生成中间数据库文件(.syn)等操作,elaborate核心进行设计实例创建、参数重定义与工艺库映射等操作。该方式将设计映射到GTECH,继而能够映射到目标库。

(GTECH格式是DC先将不同语言的RTL网表转化成统一的与工艺无关的门级网表形式,转化的过程中,DC会利用其内部的DesignWare库对RTL代码进行结构级和逻辑级的优化)。

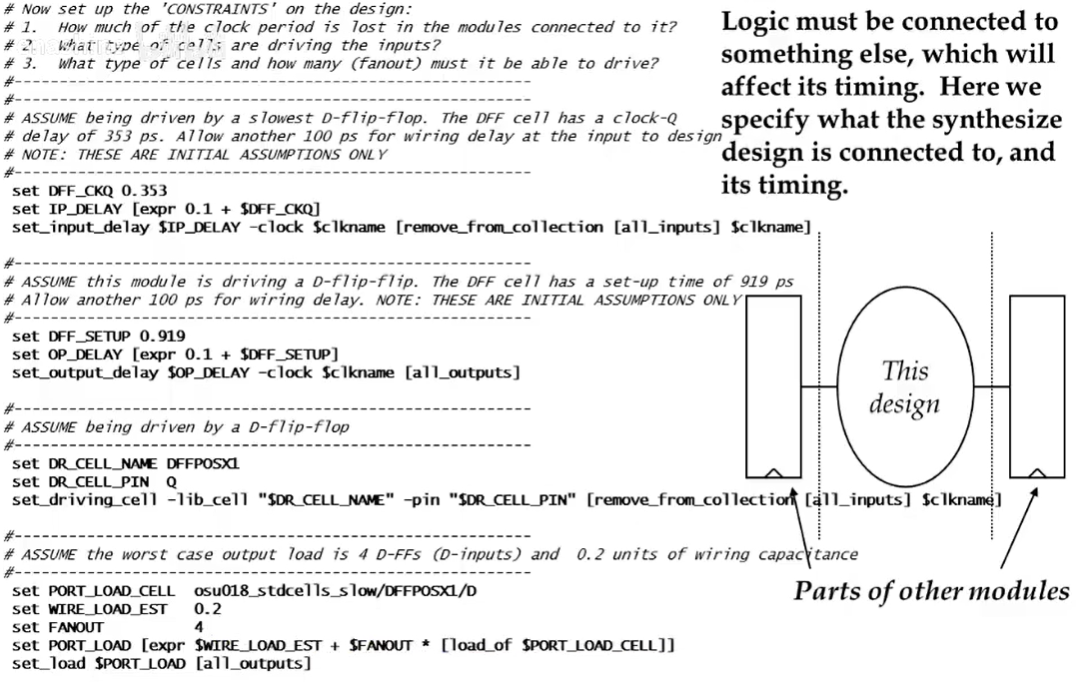

2、确定时钟信号及接口模块的时序约束

set_input_delay $OP_DELAY -clock clk [remove_from_collection[all_inputs] clk] 是一个集合操作,表示从所有输入端口中移除名为clk的端口,然后对剩下的输入端口设置输入延迟。

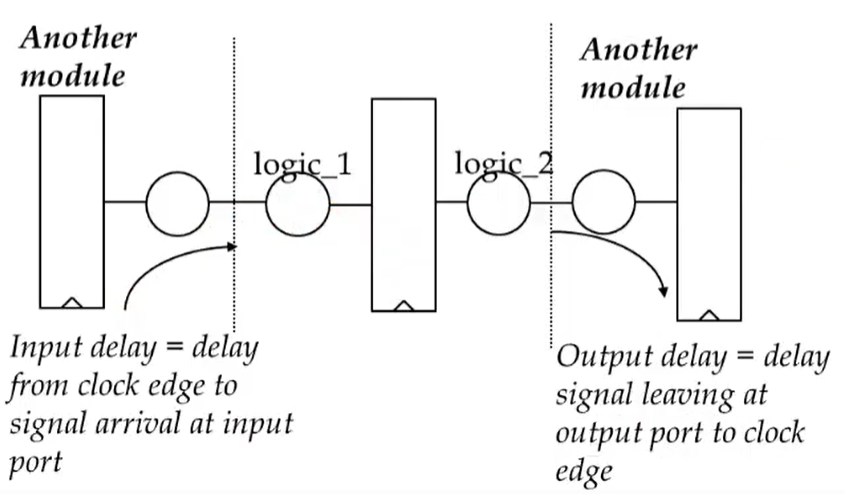

这里假设大家的设计由一个D触发器驱动,因此这里的输入延迟基本上是ck-Q的延迟;并假设设计驱动一个D触发器,输出延迟设定为触发器的建立时间以及额外的互连线延迟。实际场景中可能还会有其他逻辑的延迟。

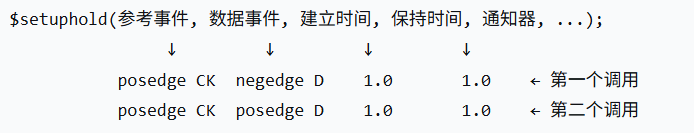

例如SMIC0.18um工艺库中DRQHDV0模块的建立和保持时间均为1ns:

时序检查架构任务$setuphold(specify块中):

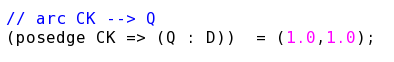

条件路径延迟声明(specify块中):

该语句表示从时钟CK的上升沿到输出Q的时序弧,并且输出Q的值取决于输入D的值。延迟被指定为(1.0,1.0),分别代表上升延迟和下降延迟,即这个D触发器的t_ck-Q延迟是1ns。

输入延迟等于从时钟上升沿到信号到达输入端口的延迟,一般为t_ck-Q delay;

Tcp >= input_delay + t_logic1 + t_su + t_uncertainty

由此可计算出logic1的最大延迟;

输出延迟等于信号离开输出端口到时钟上升沿的延迟,一般为t_setup;

Tcp >= t_ck-Q + t_logic2 + output_delay + t_uncertainty

由此可计算出logic2的最大延迟;

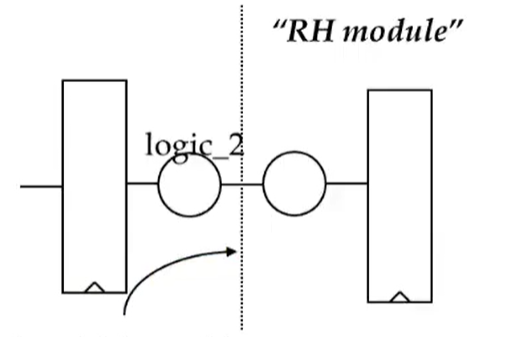

eg:假设t_logic2已给定,对于RH module你得确定多大的输入延迟?

>input_delay = t_ck-Q + t_logic2

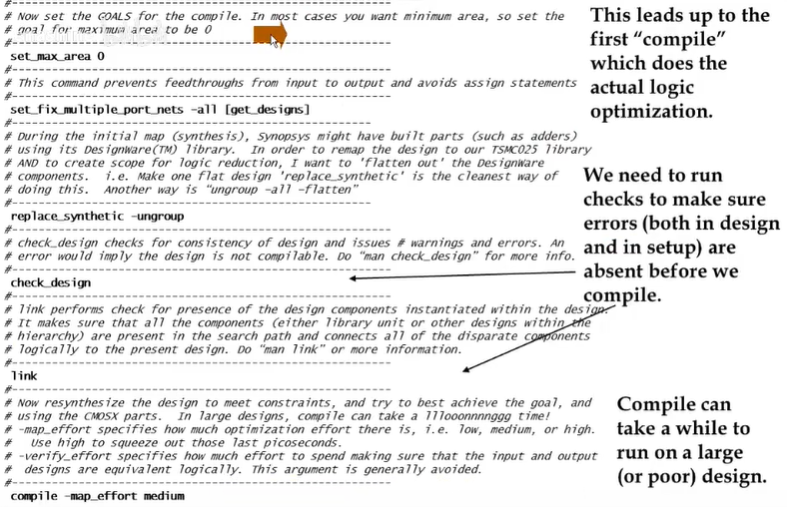

3、确定综合目标,优化设计与时序

如想要最小面积,则只需set_max_area 0;

DesignWare是Synopsys提供的IP库,在最初的映射阶段,Synopsys可能已经利用该库构建了某些部分(例如加法器),为了将设计重新映射到我们的工艺库(如SMIC018),并为逻辑简化创造空间,可以使用replace_synthetic -ungroup命令取消分组,使其成为扁平化设计,以便进行逻辑优化。

>check_design

>link

>compile_ultra -map_effort medium

compile语句将进行逻辑优化,将通用的GTECH网表转换并优化成选定的目标工艺库,运行启发式算法来尝试接近最优的逻辑,并指定运行启发式算法的努力程度,即开始对设计进行综合。compile_ultra现代设计的普遍选择。就是是更高级的综合命令,相比compile具有更强大的逻辑优化能力,

>report_timing -delay max -nworst 30>timing_report_max_30.rpt

新建或替换原有文件;

>report_timing -delay max -nworst 30>>timing_report_max_30.rpt

在文件结尾开始写,不改变原有文件内容。

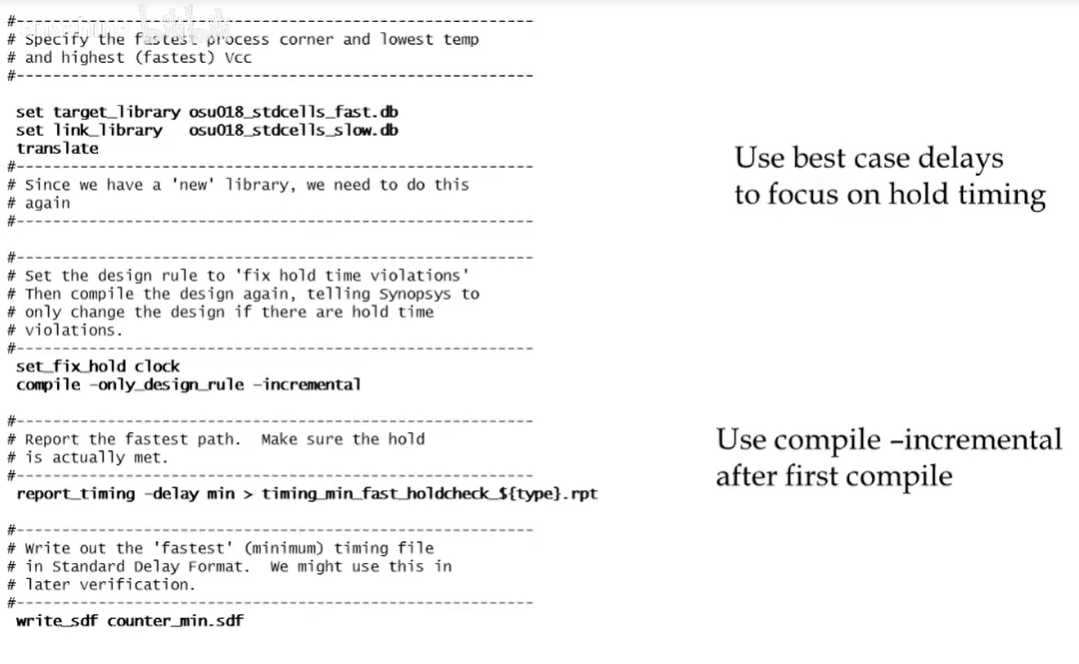

建立时间检查结束后,还应该检查保持时间违规,因此需要将设计转译到最快的工艺角:

(最快工艺,最低温度,最高电压)

> set_app_var target_library {scc018_ff.db }

> set_app_var link_library { * scc018_ff.db }

> translate

translate相比compile只进行简单的门级映射,而不进行深入优化,可以认为是compile的一个子步骤;

之后进行时序约束;

> set_fix_hold clock

该命令使DC关注并修复指定时钟域下的保持时间违例,核心手段是通过在内容路径上插入缓冲器来增加数据路径的延迟;

> compile only-design-rule -incremental

该命令表示对当前设计进行增量编译增量编译;就是,并且只修复设计规则违例。由于我们已经完毕了主编译,之后的所有编译都应该

>report_timing -delay min -nworst 30 > timing_report_min_30.rpt

检查是否有保持时间违例。

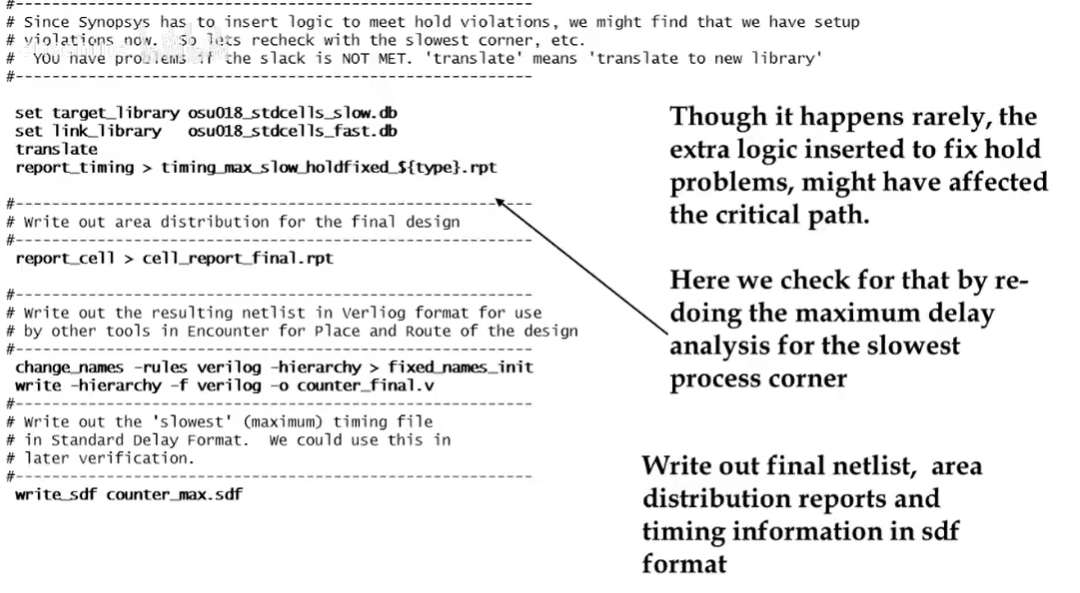

为了修复保持时间违规,综合程序很可能会插入逻辑门电路,这可能会导致建立时间违规,于是我们需检查设计在慢速版本的时序:

> set_app_var target_library {scc018_ss.db }

> set_app_var link_library {* scc018_ss.db }

> translate

>report_timing -delay max -nworst 30 > timing_report_max_30.rpt

进行最大延时分析,检查是否有建立时间违规;如果存在,则必须在慢速库进行增量编译,然后重复检查建立保持时间。若是没有障碍,则可以输出最终结果:

>report_area

> report_power

保存设计:

> write -hierarchy -output ./Top.db Top

将当前设计连同其完整的层次结构,保存到当前目录下的Top.db文件中,使用DC的专用二进制数据库格式,采用以下语句再次读入与解析:

> read_db ./Top.db

> current_design Top#指定顶层

> link#建立Top与其他子模块的实例连接关系,绑定工艺库单元到实际库模型等

> write -hierarchy -formate verilog -output ./Top.v Top

> write_sdf Top.sdf

> write_sdc Top.sdc

.v,.sdc,.sdf主要用于综合后仿真。 如在门级仿真时在tb材料中加入以下语句,将.sdf文件标注到测试记录中:

initial $sdf_annotate("Top.sdf",u_Top);

参考资料:

【精品课程】芯片设计与综合 第19课 综合优化、时序验证与网表生成_哔哩哔哩_bilibili

《ASIC设计理论与实践》

Deepseek

浙公网安备 33010602011771号

浙公网安备 33010602011771号