Verilog语法串烧

==================================================================================

===================================begin===========================================

以一下参考张德学的EDA课件:

挑些有用的,写写记心间

===================

==reg/wire类型==

wire:表达连接关系;

reg:表达存储部件,如D触发器(DFF,D Flip-Flop);也可能表达组合逻辑;reg,time,integer,real都属于reg类型;

reg都是有基本门电路构建起来!!!

都可以指定位宽:

wire a; wire [9:0] a; //????? reg a; reg [8:0] a;

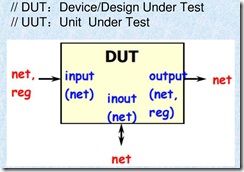

wire和reg的使用,谨记如下图:

===================

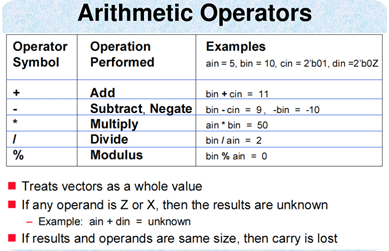

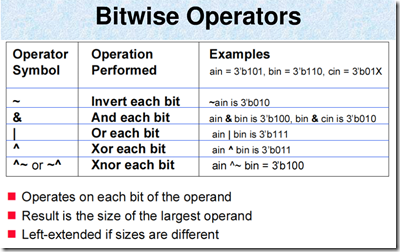

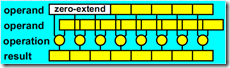

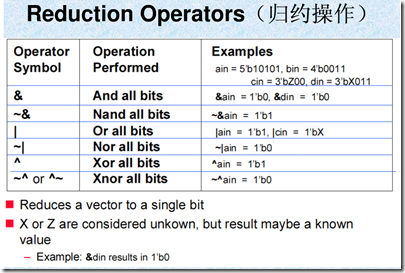

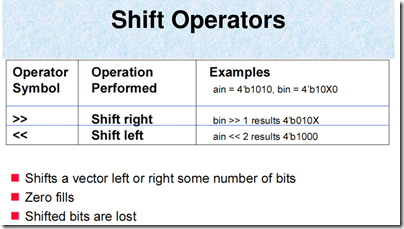

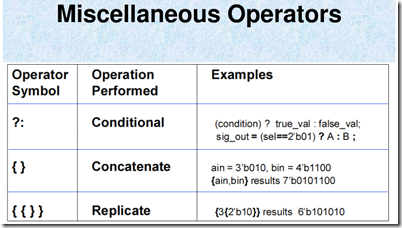

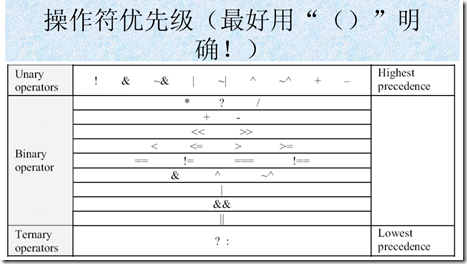

==运算==

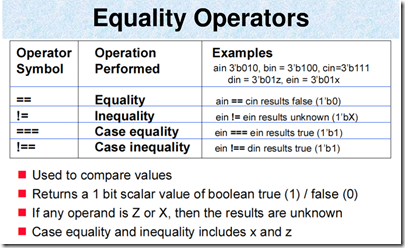

==和!=可用于描述硬件

===和!==仅用于仿真

This is Very important!!!

4、语法

assing 连续赋值语句

- 为wire类型赋值,一般表达组合逻辑

Example:

assign out = in1 & in2;

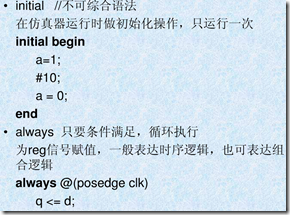

initial 、always 过程块

begin end表达顺序操作

fork join表达并发操作

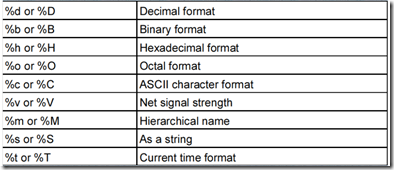

5、常用系统任务

$display

$monitor 监控指定信号,当指定信号发生变化时,执行一次,语法同$display,只是执行时间不同

$time 返回当前时间,单位同 ’timescale

$finish 仿真器退出

$stop 仿真器暂停

$display 类似于C语言的printf

Example:

====================================end============================================

===================================================================================

浙公网安备 33010602011771号

浙公网安备 33010602011771号