ARM Cortex-M3/M4初学习(未完待续)

ARM Cortex-M3/M4初学习

0. 架构与核心特性

0.1 指令集架构

- 基于ARMv7-M架构,支持Thumb-2指令集(混合16/32位指令集)

- 基于哈佛架构,数据和指令分布存储在独立的空间中

0.2 流水线

- 三级流水线: 取值(Fetch) - 译码(Decode) - 执行(Execute)

- 这种结构在简化设计和降低功耗的同时,仍然能够提供足够的处理能力。

0.3 总线结构

- I-bus(Instruction Bus,指令总线):

用于从代码存储器(如 Flash 或 ROM)中读取指令。

- D-bus(Data Bus,数据总线):

用于从内存(如 SRAM)或外设寄存器中读写数据。

- S-bus(System Bus,系统总线):

用于访问 内存映射的外设、系统控制块(SCB) 和 调试接口。

- DMA:(不一定存在)stm32f1,f4系列均有,一般每个DMA有8个 stream 流,其中f4系列的DMA具有FIFO

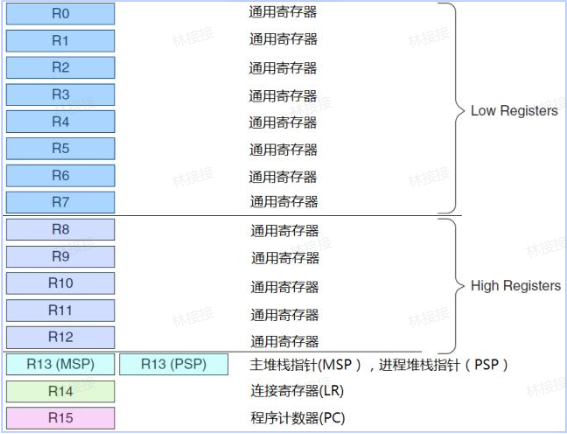

1. 寄存器组

| 寄存器 | 说明 | 分组 |

|---|---|---|

| R0 | 通用寄存器 | Low Registers |

| R1 | 通用寄存器 | Low Registers |

| R2 | 通用寄存器 | Low Registers |

| R3 | 通用寄存器 | Low Registers |

| R4 | 通用寄存器 | Low Registers |

| R5 | 通用寄存器 | Low Registers |

| R6 | 通用寄存器 | Low Registers |

| R7 | 通用寄存器 | Low Registers |

| R8 | 通用寄存器 | High Registers |

| R9 | 通用寄存器 | High Registers |

| R10 | 通用寄存器 | High Registers |

| R11 | 通用寄存器 | High Registers |

| R12 | 通用寄存器 | High Registers |

| R13 | 主堆栈指针 (MSP) ,R13 (PSP) 为进程堆栈指针 (PSP) | - |

| R14 | 连接寄存器 (LR) | - |

| R15 | 程序计数器 (PC) | - |

1.1 通用寄存器:R0-R12(共13个)

- 低组寄存器(Low Registers):

R0-R7 为低组寄存器,所有指令都可以访问(共8个)

- 高组寄存器(High Registers):

R8-R12为高组寄存器,只有32位Thumb指令和很少的16位Thumb指令能访问(共5个)

1.2 堆栈指针:SP(R13)

cm3/cm4内核有两个SP,分别是MSP(主堆栈指针)和PSP(进程堆栈指针),共用寄存器地址

-

主 堆栈指针(MSP):

-

用于 特权模式(Handler Mode) 和 异常 / 中断处理。

-

由硬件自动切换,例如进入中断服务程序(ISR)时,处理器强制使用 MSP。

-

裸机默认只使用MSP

-

进程堆栈指针(PSP):

- 用于 用户模式(Thread Mode),通常运行应用程序或用户任务。

- 需手动配置,适用于多任务系统中不同任务的堆栈隔离。

- 常用于RTOS中

-

示例:FreeRTOS中是怎么使用MSP和PSP的

场景 使用的堆栈指针 说明 系统启动 MSP 默认模式,初始化阶段使用 用户任务运行 PSP 每个任务独立堆栈,由调度器管理 中断 / 异常处理 MSP 保证内核稳定性,隔离任务堆栈 任务切换(PendSV) PSP → MSP → PSP 保存旧任务 PSP,加载新任务 PSP 特权 API 调用 PSP(短暂切换) 通过 SVC 或直接寄存器操作

1.3 链接寄存器:LR

- 连接调用子程序(中断or异常or函数)时存储的返回地址

- 可以用于栈回溯调试

1.4 程序计数器:PC

- 指向当前程序运行的指令的地址

1.5 程序状态寄存器:xPSR

等我有时间学一下😁

2. 寄存器用途

- R0 到 R3:前4个函数参数使用R0-R4传参,超出部分通过堆栈传递

- R4 到 R11:局部变量,保存上下文,被调用者保存的寄存器。

- R12:临时寄存器,调用者保存的寄存器。

- SP:栈指针。

- LR:链接寄存器,用于保存返回地址。

- PC:程序计数器。

3. 堆栈

这里讨论的C语言中的堆栈,不是RTOS中的堆栈

堆栈的空间均分配在RAM中,一般可以通过修改启动文件来修改栈的大小

3.1 堆

- cm3/cm4中堆向上生长

- 由程序员分配,效率低

3.2 栈

-

栈一般是函数调用中会使用,所以过度递归会导致爆栈

-

由程序自动分配,效率高

-

cm3/cm4中栈向上生长

-

栈的最大调用深度可以通过MDK生成的htm文件查看(估计值)

KEIL MDK .map文件分析(必学知识点) - 正点原子倾力打造!-OpenEdv-开源电子网

4. CM3与CM4的区别

| 特性 | Cortex-M3 | Cortex-M4 |

|---|---|---|

| 指令集 | Thumb-2(支持部分 16/32 位指令) | Thumb-2 + DSP 扩展指令集 |

| 浮点单元(FPU) | 不支持 | 可选单精度 FPU(IEEE 754) |

| DSP 指令 | 无 | 支持乘加(MAC)、SIMD、饱和运算 |

| 硬件除法器 | 支持(32 位除法的周期数更多) | 优化除法周期(部分型号) |

5. 什么是哈佛架构?

- 定义:将程序指令和数据存储在两个独立的内存中的体系结构。

- 特点:

- 分离存储器:指令和数据各自有独立的存储空间。

- 独立总线:使用分开的总线分别传输指令和数据,允许同时访问指令和数据(并行)。

- 提高性能:通过并行访问指令和数据,增强系统的处理速度。

- 硬件复杂:需要两个独立的存储器和总线,硬件复杂性较高

浙公网安备 33010602011771号

浙公网安备 33010602011771号