练习三 条件语句实现计数分频

模块源代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 14:50:03 07/25/2019

// Design Name:

// Module Name: fdivision_test

// Project Name:

// Target Devices:

// Tool versions:

// Description: 10M分频到500K

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module fdivision_test(

RESET,

F10M,

F500K

);

input F10M,RESET;

output F500K;

reg F500K;

reg [7:0]j;

always @(posedge F10M)

if(!RESET)

begin

F500K <= 0;

j <= 0;

end

else

begin

if(j == 19)

begin

j <= 0;

F500K = ~F500K;

end

else

j <= j+1;

end

endmodule

测试模块代码

`timescale 1ns / 100ps

`define clk_cycle 50

// Company:

// Engineer:

//

// Create Date: 14:58:48 07/25/2019

// Design Name: fdivision_test

// Module Name: D:/FPGA/project/fdivision_test/vtf_fdivision_test.v

// Project Name: fdivision_test

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: fdivision_test

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module vtf_fdivision_test;

// Inputs

reg RESET;

reg F10M;

// Outputs

wire F500K;

// Instantiate the Unit Under Test (UUT)

fdivision_test uut (

.RESET(RESET),

.F10M(F10M),

.F500K(F500K)

);

always #`clk_cycle F10M = ~F10M;

initial begin

// Initialize Inputs

RESET = 1;

F10M = 0;

#100 RESET = 0;

#100 RESET = 1;

#10000 $stop;

end

endmodule

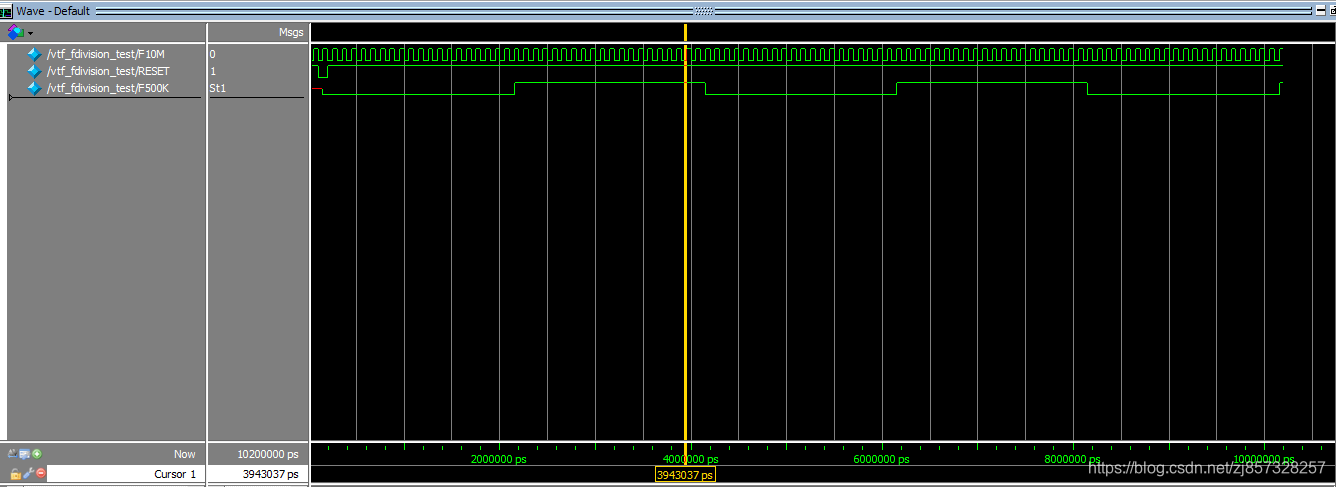

仿真波形

信心最重要

浙公网安备 33010602011771号

浙公网安备 33010602011771号