Allegro布线基本操作

目录:

一、Allegro基本技巧

1.关闭电源和地网络的飞线

2.开启特定NET飞线

3.元器件快速对齐(待完善)

4.allegro布线完成后如何修改线宽

5.Allegro批量复制Via并保持net属性

6.针对win10系统叠层和Identify DC Nets窗口弹不出来解决方法

7.元件高度的设定与测量

二、快捷键的应用与设置

三、规则设置

四、网表DXF的导入与placement

五、电源PCB注意事项

六、CLK、Chock、MOS、高速信号等注意事项

七、DDR Layout讲解

八、Geber的设置与导出。

1.关闭电源和地网络的飞线

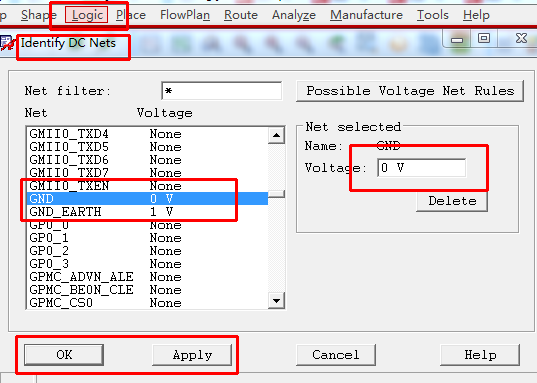

(1)点击Logic-Identify DC Nets,把要关闭的电源和地net设置成相应的电压值,即可关闭。

(2)从Command窗口关闭电源和地的飞线.如下图:

2.开启特定NET飞线

打开未完成的PCB文件,点击菜单栏的DISPLAY->Show RATS->nets。点击你想要显示的VCC\GND元器件的引脚,使未布线完成的电源管脚的连接关系暴露。

3.元器件快速对齐

(1)要在placement模式,框选或者按Shift选择元件,右键align component选项。

注意,如果元件散落成X,Y方向都有可能对齐的样式,软件会选择其中不会造成Align 后元件重叠的那种方向进行对齐。

(2)在top/bottom 的Silkscreen临时画一条线(add line)手动对齐

4.allegro布线完成后如何修改线宽

1.如果要改变整个一条导线的宽度

(1)在find栏里选择Cline;

(2)在PCB中选择要改的导线,点击右键,选择Change Width

(3)在对话框中输入你想要的线宽

2.如果要改变整个导线中某一段导线的宽度

(1)在find栏里选择Cline Segs

(2)在PCB中选择要改的导线,点击右键,选择Change

(3)在对话框中输入你想要的线宽

edit\change,find栏里选上cline,options里有个linewidth在框框中输入你需要的线宽,然后点击需要修改的cline

edit\change,find栏里选上cline,options里有个linewidth在框框中输入你需要的线宽,然后点击需要修改的cline

5.Allegro批量复制Via并保持net属性

使用Allegro时需要批量复制net属性是GND或是其它属性的Via:

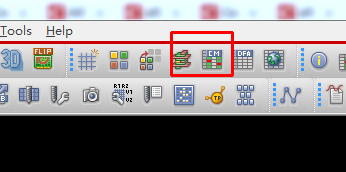

批量选中Via后点击Copy或'Shift+F5'

然后完成复制,如图:

复制完,我们可能发现,这些复制的Via的net属性不是我们想要的GND属性

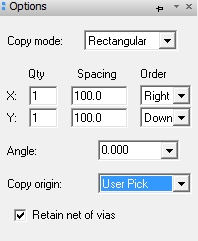

注意选择上Retain net of vias可以解决这一问题:

该选项允许我们在复制时候保留via的net属性

6.针对win10系统叠层窗口弹不出来解决方法

先右键看有没有done,然后点击层叠,如果没有看到窗口,就按住alt+空格+x,层叠对方框就会跳出。之后缩小窗口,点击OK.

7.元件高度的设定与测量

如何在Allegro中对器件高度设定规则? 在有的设计中,需要设定PCB板上所贴器件的高度规则。比如,超过一定高度,会对该产品在今后的装配带来不便或麻烦。所以,如果我们在项目设计之前就知道类似的一些相关尺寸规定,就可以在设置规则的时候增加一些约束条件。 首先,在制作器件封装的时候,就需要给每个器件定义它的高度:package height。 具体操作是:打开.dra文件,点击Setup—Areas—Package Height,点击器件的Place Bound Top,在Options里面会看到设定器件高度的图示。在相应的位置填入器件的min、max的值,就可以把这些信息记录在该器件的封装里了。 接下来,在.brd里面设置相关规则。 具体操作是:在需要设定相关规则的区域添加一层Route Keepout层,或者Place Bound Top层。然后,同样的按照上面的操作,点击Setup—Areas—Package Height,在Options里面按照示意图,设定相关的规则就行了。 需要注意的是: (1) 首先应该确保所有器件的.dra文件里面都包含了器件高度的设定,否则默认状态下,在placement的时候每个器件都会产生DRC的。如果不知道器件的高度,又不希望那些规则作用在这个器件上,那么可以把最大值设置为0,就可以避免出现不希望看到的DRC。 (2) 如果是采用在Place Bound Top层设定该规则,那么,DRC会产生在相应的Top或者Bottom层;而如果是采用在Route Keepout层设定该规则,那么,DRC会产生在DRC这一列下方的Place Top或者Place Bottom。 (3) 在用不同的层设定该规则的时候示意图的尺寸指示是有所区别的,在设定规则的时候需要注意规则的正确性。 (4) 这种关于器件高度的规则设定是不能够在Setup--Constraints里面通过添加一个Area再在Area里面设定规则来实现的。

如果要对高度设定规则,则需要器件封装中的Place Bound这一层有高度信息。然后在allegro单板设计时,要area中增加如下shape即可

右键添加shape到对应层面后,填入相应要求的高度信息即可

8.Allegro中如何更改字体和大小(位号丝印)

1.、更改丝印字体的大小

选择Edit->change按钮,在allegro的右侧出现如下图所示的图标:

若要更改字体大小,只需调整Text block字体大小即可。

2、更改丝印字体的粗细

选择Setup->Design Parameter,再选择Text,即可出现下图所示界面:

再选择Setup Text Sizes,出现下图所示界面:

调整Photo Width,即可达到调整线宽的目的。

9.

浙公网安备 33010602011771号

浙公网安备 33010602011771号