转:3.3V和5V电平双向转换——NMOS管

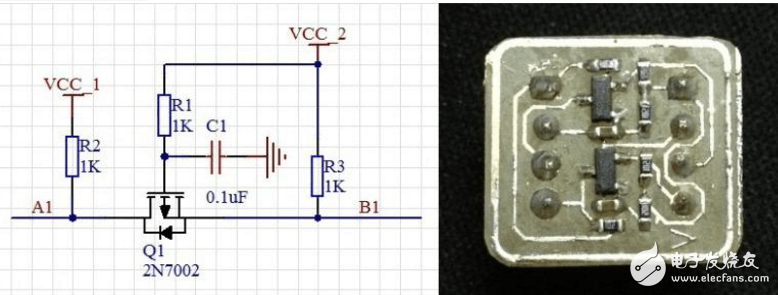

分简单,仅由3个电阻加一个MOS管构成,电路图如下:

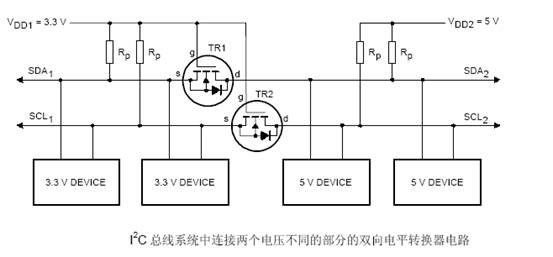

此电路来自于飞利浦的一篇设计指导文档,是I2C总线官方推荐使用的电平转换电路。在实际使用过程中,需要尤其注意NMOS管的选型以及上拉电阻阻值的选取。由于该电路基于上拉电阻,NMOS管的电容特性可能会导致波形劣化。为了保证输出的上升速度,使得输出波形维持较好的形状以保证数据正确,通常选择Qg较小的NMOS管。

上图中,SDA1/SCL1,SDA2/SCL2为I2C的两个信号端,VDD1和VDD2为这两个信号的高电平电压。电路应用限制条件为:

1,VDD1 ≤ VDD2;

2,SDA1/SCL1的低电平门限大于0.7V左右(视NMOS内的二极管压降而定);

3,Vgs ≤ VDD1;

4,Vds ≤ VDD2 。

电路分析如下:

1、没有器件下拉总线线路。

3.3V部分的总线线路通过上拉电阻Rp上拉至3.3V。 NMOS管的栅极和源极都是3.3V, 所以它的Vgs 低于阀值电压,NMOS管不导通。这就允许5V部分的总线线路通过它的上拉电阻Rp上拉到5V。此时两部分的总线线路都是高电平,只是电压电平不同。

2 、一个3.3V 器件下拉总线线路到低电平。

NMOS管的源极也变成低电平,而栅极是3.3V,Vgs上升高于阀值,NMOS 管开始导通。然后5V部分的总线线路通过导通的NMOS管被3.3V 器件下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

3、一个5V 的器件下拉总线线路到低电平。

NMOS管的漏极基底二极管导通,源极电压为基底二极管导通0.7V,3.3V部分被下拉直到Vgs 超过阀值,NMOS管开始导通。3.3V部分的总线线路通过导通的NMOS管被5V 的器件进一步下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

优点:

1、适用于低频信号电平转换,价格低廉。

2、导通后,压降比三极管小。

3、正反向双向导通,相当于机械开关。

4、电压型驱动,当然也需要一定的驱动电流,而且有的应用也许比三极管大。

从此看的出几个关键点:

1、MOS管一定要选内嵌DS反向二极管的,没有就要外加低导通压降的管子。

2、高端侧拉低的低电平一定要够低,因为电平转换电路已经有了上拉电阻,就 不要在重复增加上拉电阻了。尤其是对于存在若下拉状态的接口。

3、线路串联电阻不要随意放,很简单串联分压,串联电阻后,主控端拉低后,接收端的电平会不够低,尤其这种状态出在3.3V一侧你就Game over了

4、通常选择Qg较小的NMOS管。

3.3向5V转换测试:

对这个电路测试了下,MOS管采用的是2N7002小信号NMOS,输入电容很小的,大概几十pF。下面是电路及实物

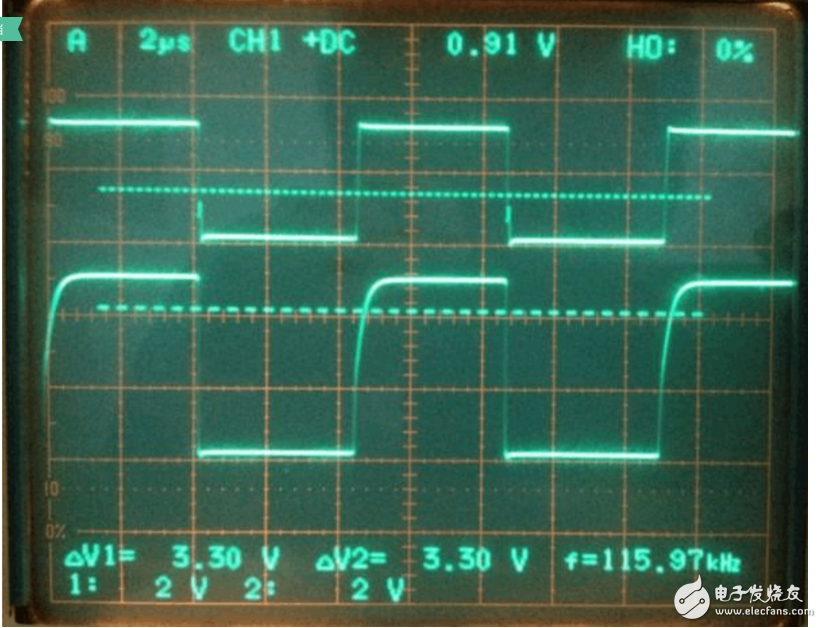

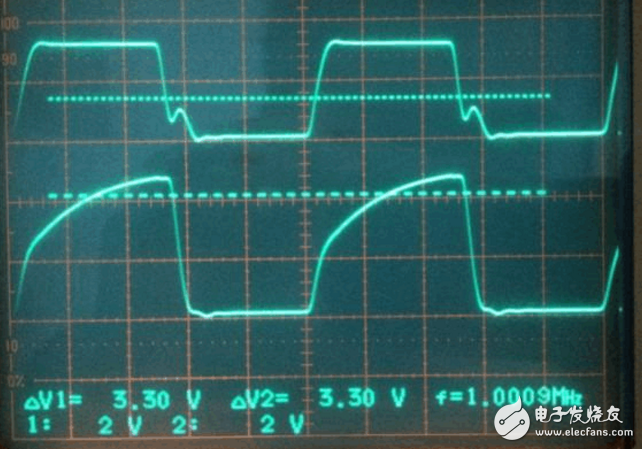

115KHz波形,这个是频率是常用串口较高的波特率

分析:5V电路上升沿缓是因为依靠上拉电阻上升至5V,时间常数决定,上拉电阻越小上升时间越小;5V电路下降沿陡是因为NMOS导通,直接由3.3V电路驱动低电平。

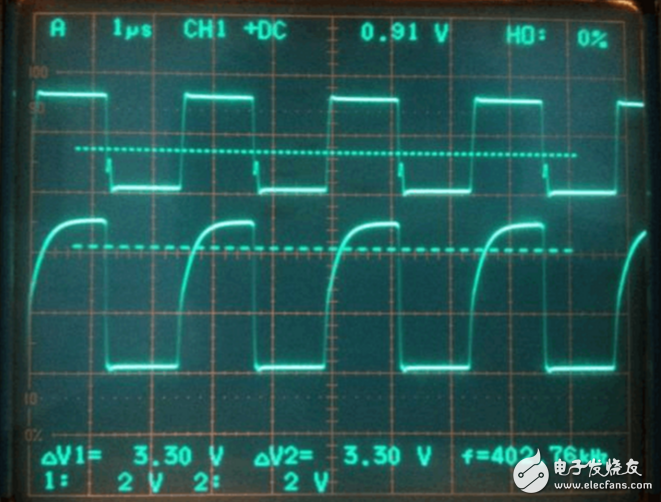

400KHz,高速IIC通信的时钟频率

1MHz,波形上升太慢了

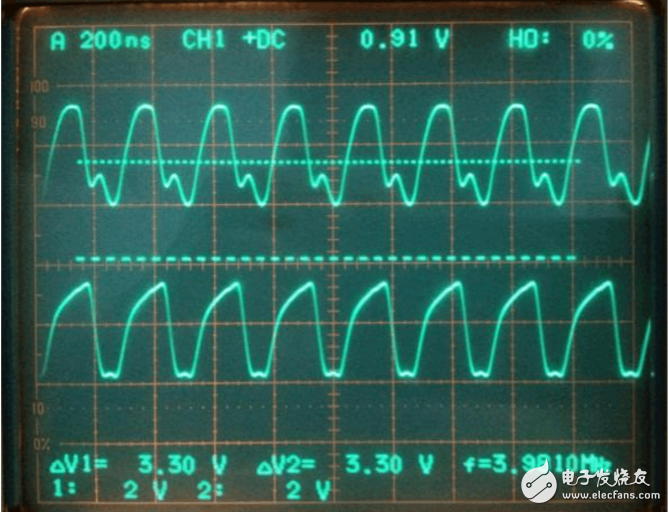

4MHz,已经不能输出5V的电平了

分析:5V电路还没来得及上升至5V就被拉下来了。

---------------------

作者:硬件菜鸟备忘录

来源:CSDN

原文:https://blog.csdn.net/impossible1224/article/details/80618703

浙公网安备 33010602011771号

浙公网安备 33010602011771号