【EMC】脉冲群Burst

目录

- 参考标准

- 目的

- 原理

- 试验等级

- 试验结果的评定

参考标准

GB/T 17626.4-2018 电磁兼容-试验和测量技术-电快速瞬变脉冲群抗扰度试验

IEC61000-4-4:2012

目的

评估设备的供电电源端口、信号、控制和接地端口在受到电快速脉冲群时的性能

![]()

原理

脉冲群发生器的输出阻抗是50欧姆,耦合电容(10±2)nF,也可以使用(100±20)nF的电容替代耦合夹、金属箔或者金属带的分布电容把脉冲群耦合到线路的端子上。

所以,如果EUT的输入阻抗是50欧姆左右时,将耦合到最大功率的干扰。

典型耦合/去耦网络特性:

- 铁氧体的去耦电感 >100uH ,串联,抑制干扰的通过。

- 耦合电容 33nF,并联,提供对地通道。

可以尝试使用这两种办法解决脉冲群问题。

试验等级

产品开发时,两种频率5kHz-15ms-300ms和100kHz-0.75ms-300ms,最好都进行测试,进行摸底。

meter使用3级时,则,电源端口和接地端口(PE)2kV-5kHz ,信号端口和控制端口1kV-5kHz。电压电流采集端口当作电源端口。

GB/T 17626.4-2018 附录B 试验等级的选择中,可以看到3级是典型的工业过程设备环境的代表,4级是变电站等这类环境的代表。

试验结果的评定

解决脉冲群问题

1.干扰源:降低干扰

2.传播路径:阻隔路径

3.敏感设备:提高抗干扰能力,使得信号变强

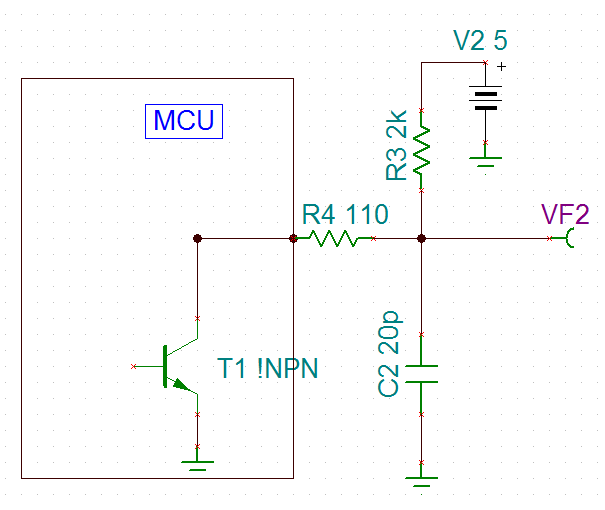

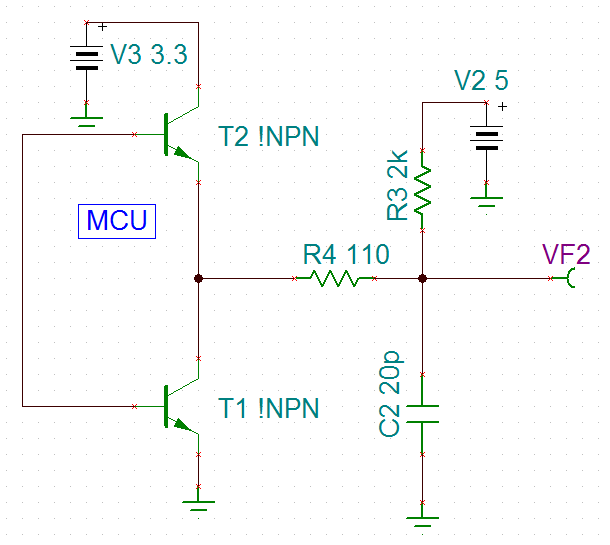

如下:输入是MCU的IO引脚,3.3V电平,100kHz方波,右侧是5V供电的IC,高电平阈值3.5~5V,低电平阈值0~1.5V。

1.当MCU设置为开漏OD模式时,脉冲群干扰到后级IC。

分析:如下图,MCU输出低电平时,信号线到地的阻抗110Ω,如果有干扰,可以导入地平面。但高电平时,噪声传入地平面和电源平面的阻抗较大,有可能因此干扰后级IC。

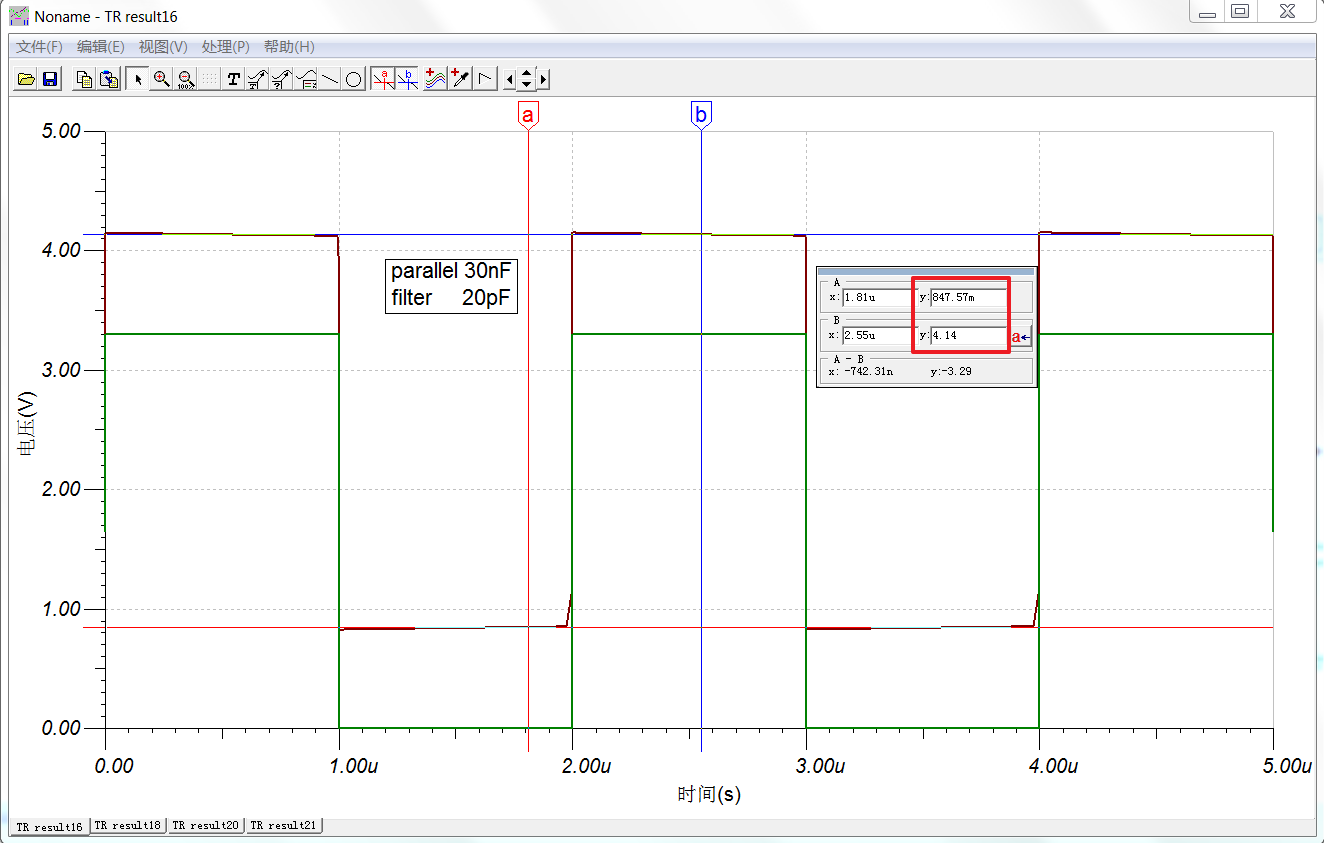

2、当MCU的IO设置为Push-Pull模式,其高低电平阻抗都将近110欧姆,测试结果良好,如下:

分析:R4=110欧姆,R3=2k时,对于逻辑1(3.5V)的阈值和逻辑0(1.5V)的阈值,信号电平安全裕量不足。

如果保证均衡的安全余量,则,R4=680,R3=2k,如下:

此时的测试结果,由于限流电阻的变大,脉冲群干扰已经干扰后级IC,可以猜想到R4的阻抗阻碍了干扰流入电源和地平面的路径。

单纯使用电阻R1=680、R2=2k分压后,能够保证逻辑1和逻辑0都有0.23V的安全余量,但是噪声传入地平面的阻抗变大。

3、加一个C1=30nF,给噪声提供低阻抗的耦合路径。

此时,信号=3.3V方波,周期500kHz,输出信号的仿真波形,如下:

分析:C1可以提高高电平到4.2V,降低低电平到0.8V。

当信号频率降低为50kHz时,出现信号电平变不规则,加大C1即可。

浙公网安备 33010602011771号

浙公网安备 33010602011771号