CH585/CH584/CH592/CH591硬件设计

CH585/CH584/CH592/CH591硬件设计

在进行设计之前 先根据自己的实际需要来选择合适的型号, 可以参见 https://www.cnblogs.com/iot-fan/p/13439275.html

注意

- 优先选择CH585/CH584/CH59x 系列芯片

- CH57x_gen1/CH57x_gen2原则上不建议新产品设计使用

获取官方的硬件资料: 直接在官网搜索相关的芯片,一般建议搜索同系列最高配置的芯片,比如找CH577的搜索CH579即可

本文分以下章节:

- 电源部分

- 时钟部分

- 复位引脚

- 天线部分

- 调试与烧录接口

- USB部分

- 以太网部分

- LCD设计

- GPIO设计

- 设计参考原理图

- layout注意事项

[电源部分]

- 部分芯片才支持最低1.7v供电

- 芯片最大供电电压为3.6v

** CH577/578/579对电源有些要求,请留意wch官方的最新的参考设计**

集成DCDC与LDO:

芯片的内部工作电压比较低,而供电往往是3.3v,不同的降压方式具有不同效率:

DCDC与LDO对比

- DCDC方式:

- 表现为供电电流会低一些,功耗友好,

- 需要一个功率电感(增加BOM),

- 一定程度的降低RX的接收灵敏度.

- LDO方式:

- 电流稍微大些,

- 但是无需外部电感,只需要把电感的引脚直接并联,或者贴0欧电阻即可,这样成本低,

- 接收灵敏度会好一些.

DCDC方式功率电感选择:

- CH57x/CH582/CH583: 22uH/DCR<=2ohnm/额定电流>=100mA (WCH的开发板用的是顺络SPH202012H220MT/ YNR2016-220)

- CH59x/CH584/CH585:10uH-22uH/DCR<=1ohnm/额定电流>=50mA (DCR也可稍大,DCR越大,DCDC效率稍有降低)

[时钟部分]

高频时钟

- CH577/578/579有内部高频RC,不用无线的话,做普通MCU时钟准确度要求不高,可以用内部;但是如果做无线通信/以太网通信,外部高频时钟是必须的;

- CH573/571/581/583/582/581/591/592,手册并没有标明有内部RC,这意味着,外部晶振是必须存在的;

- CH584 在不用无线,且对时钟误差范围要求不严格情况下,可以不贴晶振

- 上述使用晶体的情况,原则上只支持32M晶体

- 有源晶体串联150pF 到芯片Xout引脚上(你没看错,是Xout)

低频时钟

- BLE主机模式,为了良好的兼容性,必须加外部32768

- BLE从机模式,对RTC定时没有什么要求的话,可以用内部低频RC做RTC时钟.

- 其他情况,视实际需求而定.

具体可参见文章 wch ble例程中关于低频时钟的选择和差异

晶体选择:

- 外部高频晶体

- CH579/578/577 :32Mhz/10ppm/12pF

- CH573/571/CH58x/CH59x:32Mhz/10ppm/10pF (使用32Mhz/10ppm/12pF 会导致默认偏差20ppm左右,需要代码开始加入

HSECFG_Capacitance(HSECap_20p);) - 无源晶体往往有三个关键参数:频率/误差/负载电容,CH57x系列芯片 在使用BLE时候, 所选用的晶体的推荐参数是32Mhz/10ppm/12pF,尽管芯片内部支持负载电容调节,但是调节的范围是有限的,只支持晶体负载电容在9-16pF(CH579),7-14pF(CH573/571/CH58x/CH59x)的调节

- 外部低频晶体

- 32.768Khz/20ppm/12.5pF

- 更高要求的场景,一般是建议进行实际的测量来调整内部的电容值,当然,这是所有的产品设计时候的一般规律.

[复位引脚]

复位引脚开启后,内部的上拉会生效,不用再挂外部上拉,如果用不到复位,直接悬空即可.

芯片提供了一个可选择的外部复位引脚,在与PB23复用,当作为复位使用时候,是低电平有效,但是注意以下事项

- 调试使能后,外部复位(PB23)这个引脚自动强制关闭;

- 在使用reset引脚对应的外设后,必须要把外部复位关掉,如在ch579上使用LCD;

- 外部复位在烧录时候修改后,一定要重新上电才会生效;

- 在芯片处于ISP 的boot时候,这时候如果复位有效,会导致芯片退出isp;

- 芯片出厂的默认配置,复位引脚是没有启用的.

- 如果使用按键做复位,需要并联10nF(103)的电容对地(CH573F/571F必须).

* 新版本的CH579 在bootloader 版本>=2.8后,如果外部挂104(100nF)电容,会导致芯片上电时候产生的复位是外部复位而不是上电复位,导致进到bootloader后就跳出去了,保险的方法是挂103,能不挂就不挂

* ch571/573 外部复位时候,必须大于1us,加电容其实主要消抖

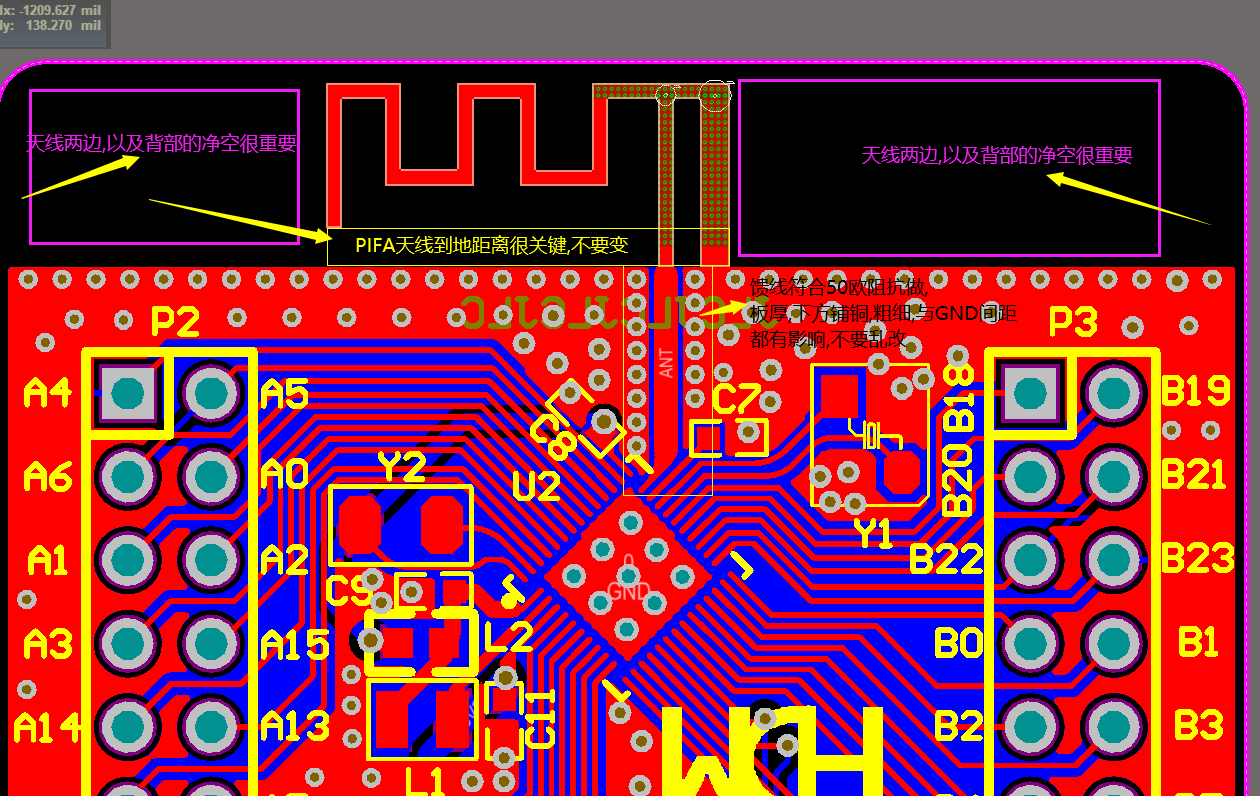

[天线部分]

- 芯片的天线部分内部集成balun,低通, 引脚已经在内部做了50欧姆的阻抗

- 在不要求极致性能的情况下,直接使用常见的2.4G的PCB/SMA/IPEX的天线即可

- 一般情况下建议预留 π 电路,可用0欧电阻连接

- 天线对净空要求比较高, layout 时候注意,尤其是要远离金属

- wch提供的不同天线封装,在尺寸允许的情况下,尽量用大的封装

- 对于陶瓷天线,严格遵循其layout指南

- 在可能需要SRRC/CE/FCC 之类的认证时候,建议在输出引脚, 可以先贴0欧电阻直连到天线.

[调试与烧录接口]

烧录支持UART/USB/SWD方式(对于CH579,ARM-SWD功能需要芯片的bootloader>=2.5才能开启), 但是由于不是所有的型号都具有USB外设,而SWD接口可能一些封装没有引出具体的IO,所以设计时候这里一定要谨慎.

- SWD:

- 对于CH578M/CH579M 使用PB16_SWDIO / PB17_SWCLK(只有QFN48的芯片才支持,并且有局限性)

- 对于CH571/CH573/CH58x/CH59x等RISC-V内核芯片SWD 在 PB14,PB15,此SWD为wch专有,非通用的arm-swd

- USB: PB10_D- /PB11_D+;

- UART1: PA8/PA9;

- USB/UART 下载触发 IO: 大多数芯片CH57x,CH58x洗牌默认PB22,(上电时候此脚低电平将会进入固件下载模式),其他芯片参考 https://www.cnblogs.com/iot-fan/p/13498088.html

[USB部分]

- usb通常不需要串联额外的电阻

[以太网部分]

[LCD设计]

LCD的功能 SEG使能是4个IO一个控制位的, 如果SEG选用的IO 不连续,一定严格参考手册上SEG寄存器使能对应IO 范围:

[9.GPIO设计]

- 只有部分引脚支持中断,支持中断的都可做唤醒

- 大部分IO是不支持防灌电的,外部输入电平不要超过芯片供电电压

- 所有的GPIO,在睡眠的时候,都可以保持电平

- 所有的gpio都支持上拉和下拉, 且可以同时开启

- 低功耗设计时候, 没有用到的IO,睡眠时候要有固定电平,可以设置为下拉输入模式

[设计参考原理图]

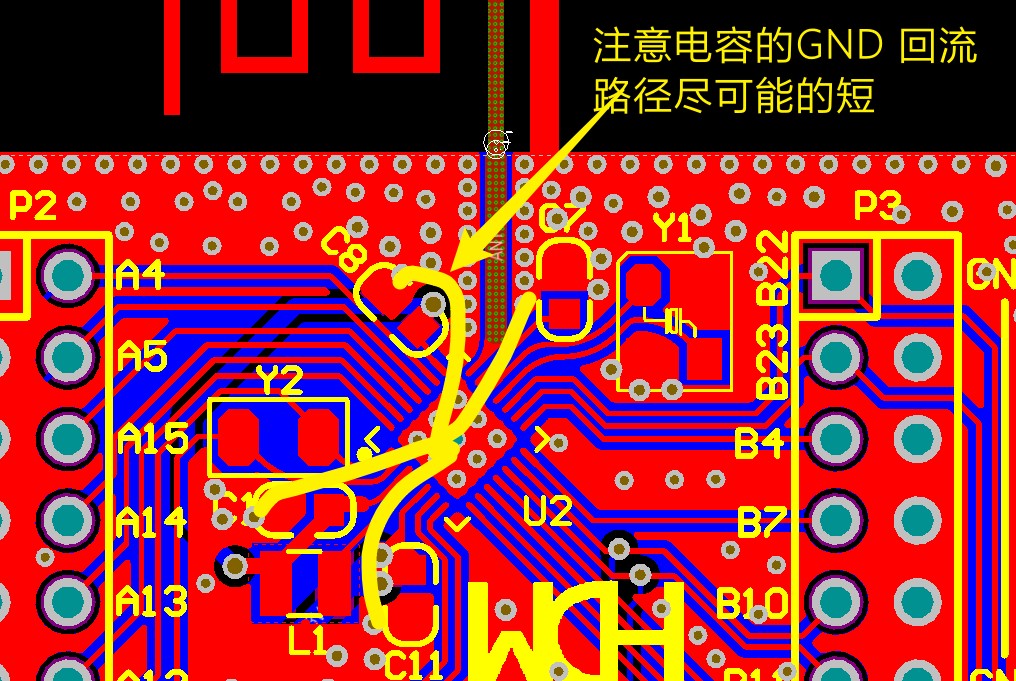

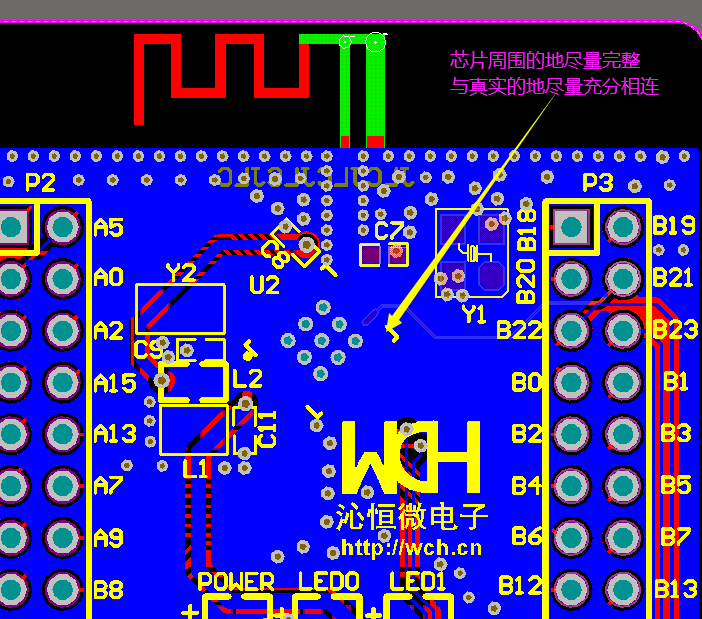

[layout注意事项]

- 射频板子的layout,并不是只需要注意天线本身,芯片周围电路的设计更为重要, 天线设计的好不好,顶多一定程度上影响信号品质, 芯片周围的电路没设计好,将会影响芯片整体的工作稳定性.

- 芯片内部的FLASH 在工作时候有几十Mhz的频率和480M的PLL倍频,以此产生的高次谐波可能会对周围靠的太近的频率敏感的元件造成干扰,如GPS接收机/SUB-G接收机,在layout时候尤为注意器件间的相对位置距离

图片来源: 沁恒微电子官方 CH579 EVT 开发板: http://www.wch.cn/downloads/CH579PCB_ZIP.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号