SSD FTL设计:

首先这里讲的是ALL-Dram的一种GC设计, 我们采用L2P+P2L的模式去collect valid data。

这里吧GC分成几个步骤:

1. select src(一般情况是找到valid data 最少的Block)。

2. Load/rebulid P2L (这里采用P2L设计,自然要先Load P2L)。

3. Collect valid data (通过对比L2P和P2L去找到Valid data)。

4. Program valid data (把valid data写到dest open)。

5. Updata L2P (更新dest open data addr)。

6. Search L2P (是否有Uecc,需要search,这个步骤可能没有)。

7. release src blk (释放所有的src)。

下面依次展示每个步骤:

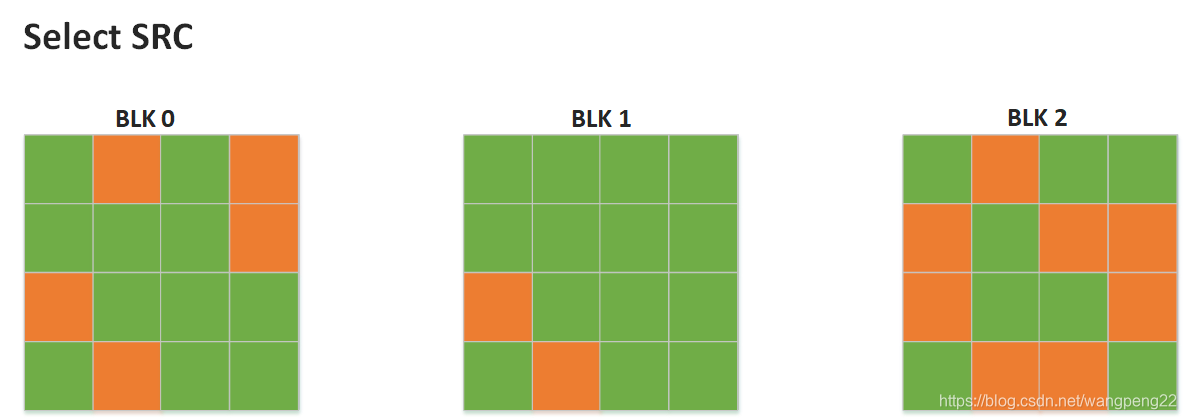

1):

这里有三个Block,分别是BLK0、BLK1、BLK2,它们的Valid Data分别是5、2、8,显然需要选择BLK1当成Src BLK。

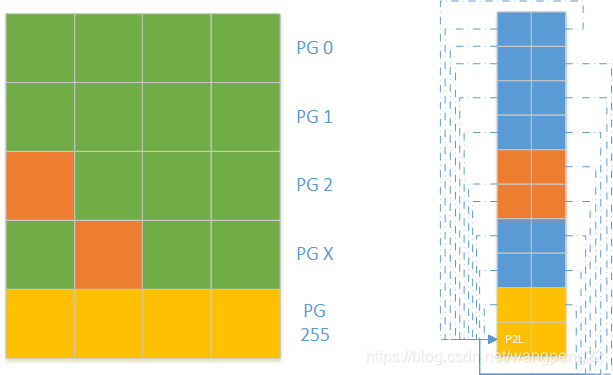

2):这里假设每个Page是4个4K单元组成,那么把Page0~Page255的addr存放在Page 255的倒数第二个4K单元,刚刚合适。

那么,这里只需要读P2L page的对应P2L 单元就可以得到整个BLK的P2L。

另外一种情况是rebulid,这里暂不阐述。

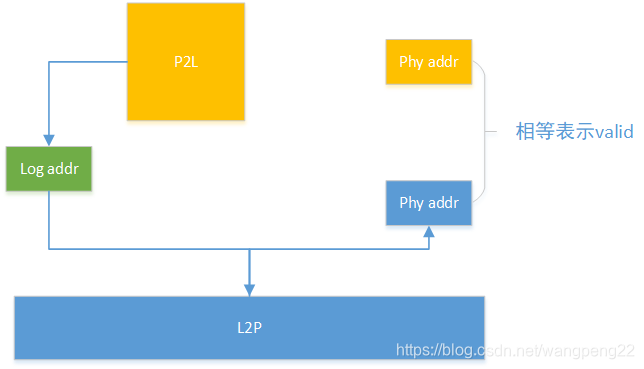

3):这里collect valid data,通过对比P2L的log addr,去查L2P的phy addr,然后对比P2L的phy addr和L2P的phy addr是否相等得到valid data。

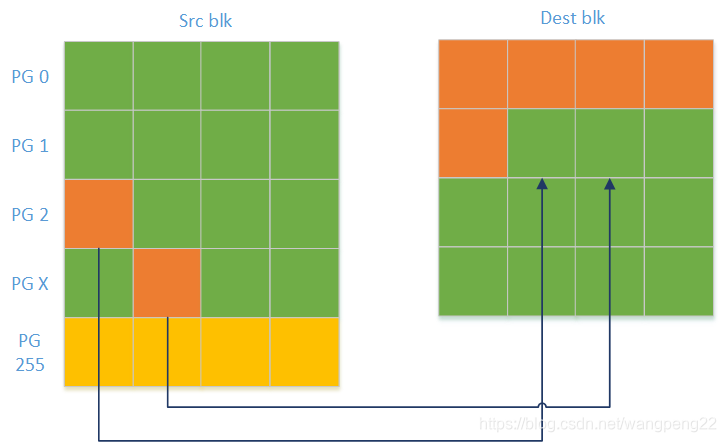

4):把上一个步骤得到的valid data program 到新的位置。

5):更新L2P, 把valid data写到新的位置后,需要更新L2P。这里值得注意的是有个Delay update机制,目的是等到program稳定之后再去更新L2P。Dest是SLC可以等delay一个page的数据, TLC需要delay一个layer的数据。

6):暂不阐述。

7):释放这个src blk,加入free blk里面。

最后需要说明,这里只是讲了最基本的GC flow,实际情况GC 需要承担各种Eorror handle 处理,远比该流程复杂。

本文来自博客园,作者:ingram14,转载请注明原文链接:https://www.cnblogs.com/ingram14/p/15778944.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号