毛刺glitch的产生与消除

1毛刺产生的原因

竞争与冒险:

有两种情况会产生竞争:门电路两个输入信号同时向相反的逻辑电平跳变或同一信号经不同路径到达终点的时间有先有后的现象。

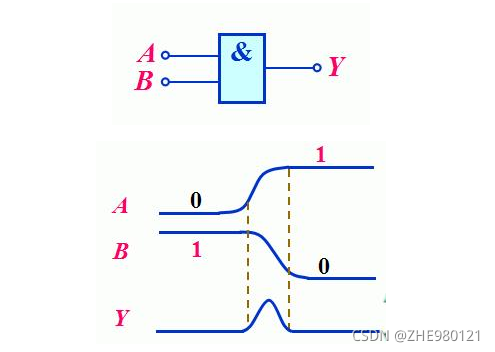

例1:信号 A、B 不可能突变,需要经历一段极短的过渡时间。而门电路的传输时间也各不相同,故当A、B同时改变状态时可能在输出端产生虚假信号。

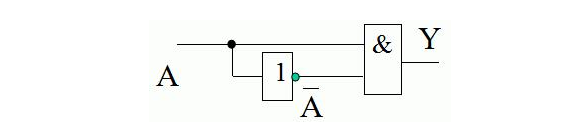

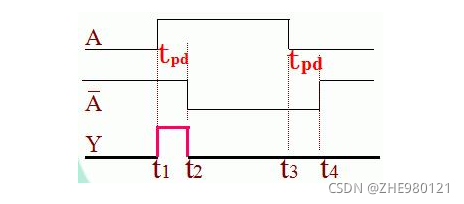

例2:同一信号经不同路径到达终点的时间有先后(或者两个不同信号变化不同步)

结果,在t1-t2 时间内,电路输出端产生了Y=1的尖峰脉冲,不符合静态下,Y恒为0的逻辑关系:

竞争:在组合电路中,信号经由不同的途径达到某一会合点的时间有先有后,这种现象称为竞争。

冒险:由于竞争而引起电路输出发生瞬间错误现象称为冒险。表现为输出端出现了原设计中没有的窄脉冲,常称其为毛刺。

竞争与冒险的关系:有竞争不一定会产生冒险,但有冒险就一定有竞争

2毛刺造成的危害

当毛刺信号成为系统的启动信号,控制信号,握手信号,触发器的清零信号,预置信号,时钟信号,或锁存器的输入信号时就会产生逻辑错误

组合逻辑产生的毛刺也会大量消耗功耗。毛刺会提高电路的活动因子增加功耗

毛刺并不是对所有的输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,因此可以 说D触发器的D输入端对毛刺不敏感。

3毛刺消除的方法

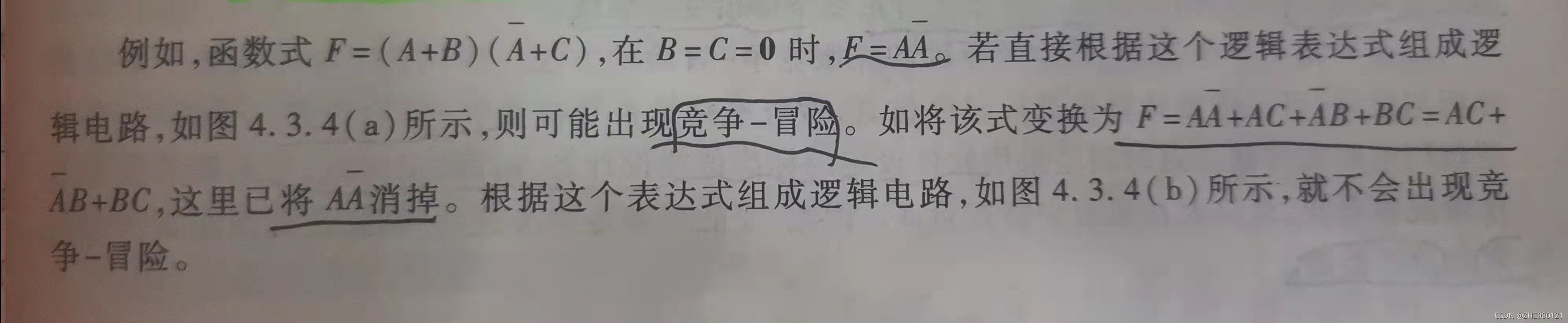

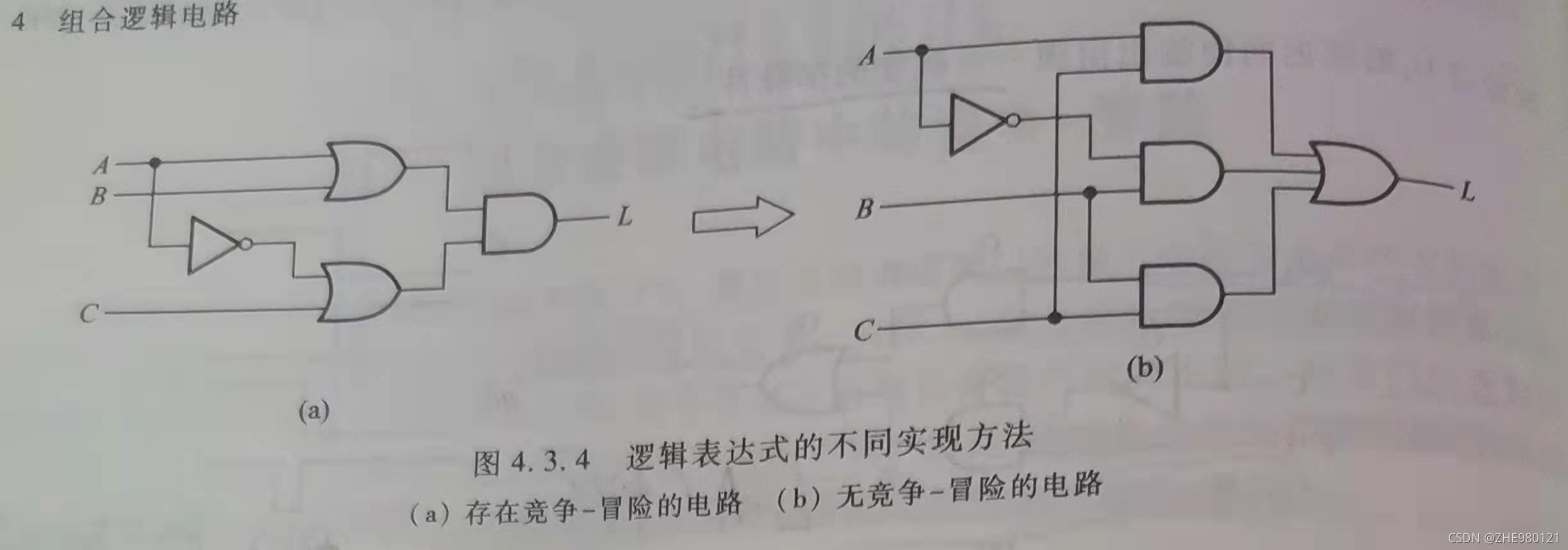

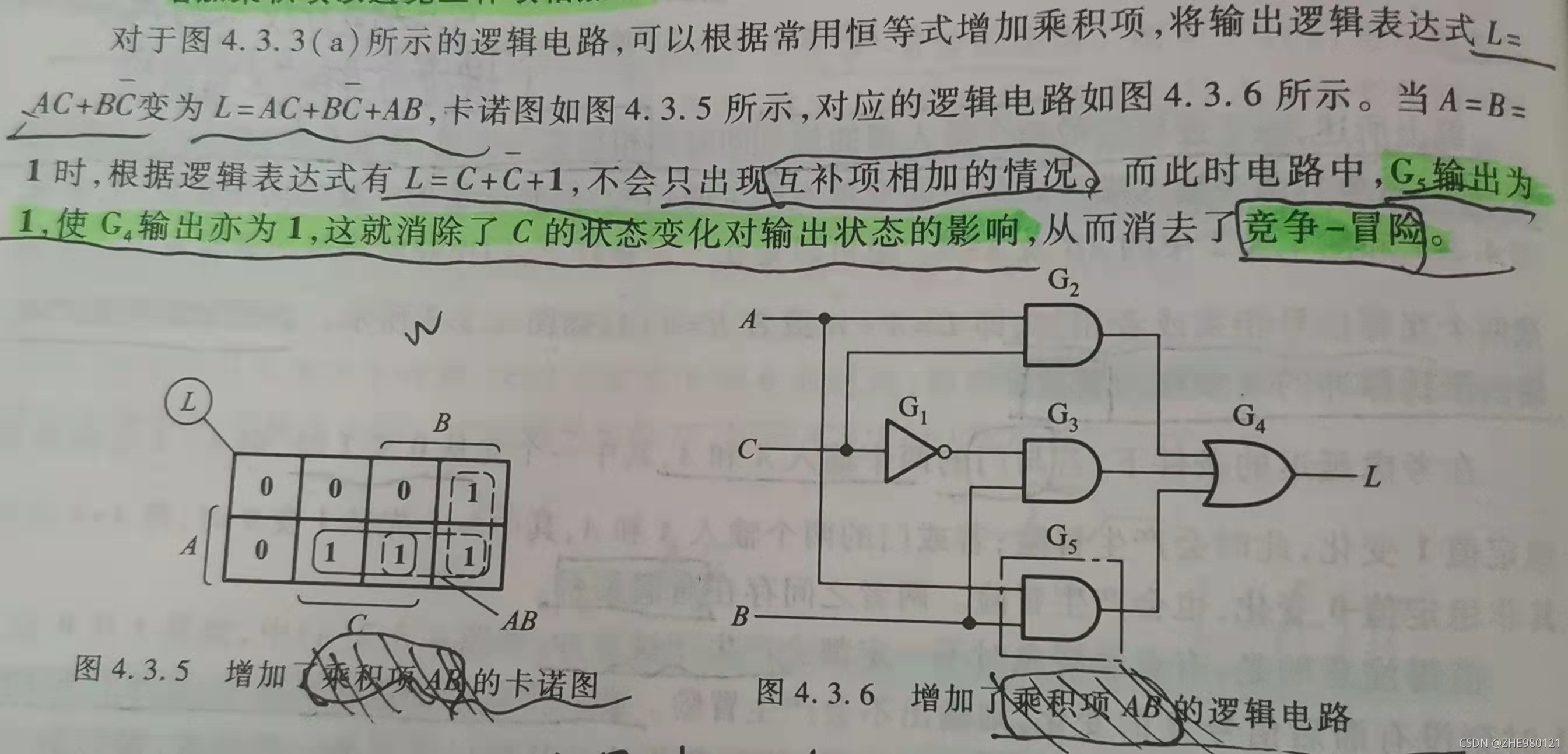

消除或者增加互补项

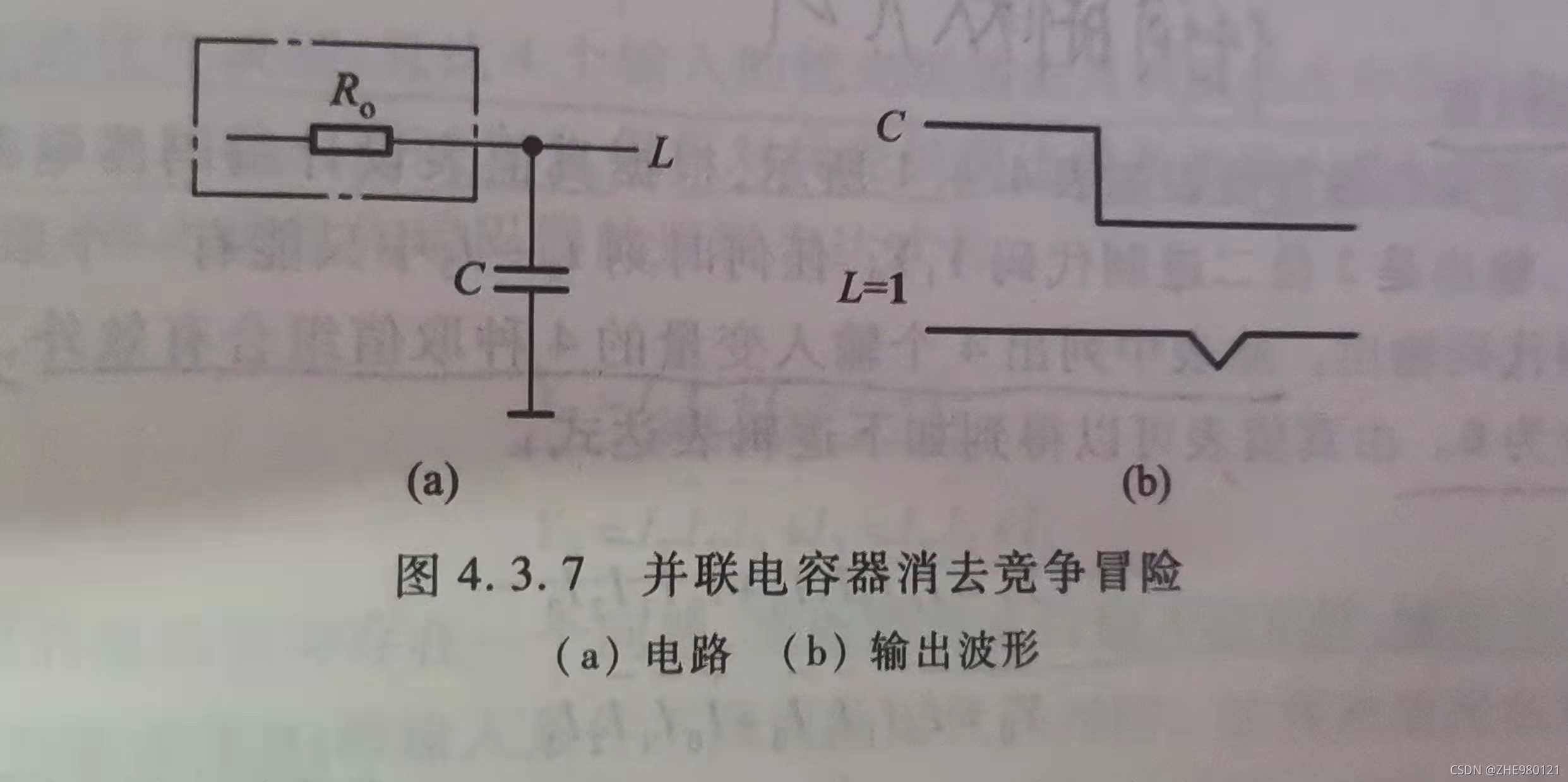

输出端并联电容器吸收

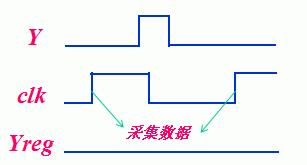

引入时序逻辑采样

用verilog代码,实现消除一个glitch

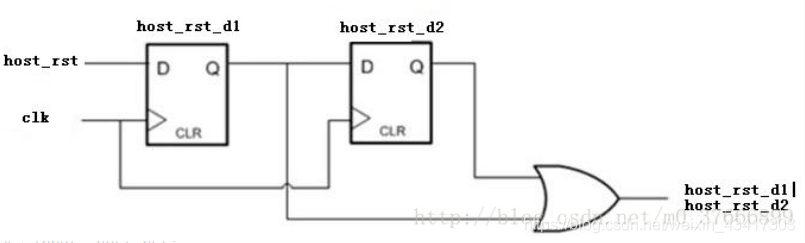

(1) 滤掉小于1个周期glitch的原理图如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

always@(posedge clk_in or negedge rst)

begin

if(!rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2;

endmodule

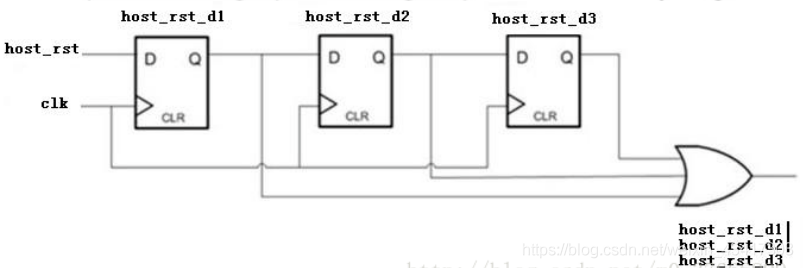

(2)滤掉大于1个周期且小于2个周期glitch的原理图如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);

input clk_in;

input rst;

input host_rst;

output host_rst_filter;

reg host_rst_d1;

reg host_rst_d2;

reg host_rst_d3;

always@(posedge clk_in or negedge rst)

begin

if(!rst)

begin

host_rst_d1 <= 1'b1;

host_rst_d2 <= 1'b1;

host_rst_d3 <= 1'b1;

end

else

begin

host_rst_d1 <= host_rst;

host_rst_d2 <= host_rst_d1;

host_rst_d3 <= host_rst_d2;

end

end

assign host_rst_filter = host_rst_d1 | host_rst_d2 | host_rst_d3;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号