低功耗设计

低功耗设计

5.2 功耗源

浪涌:器件上电时产生的最大瞬时输入电流

静态功耗:晶体管的漏电流所导致

动态功耗:逻辑转换

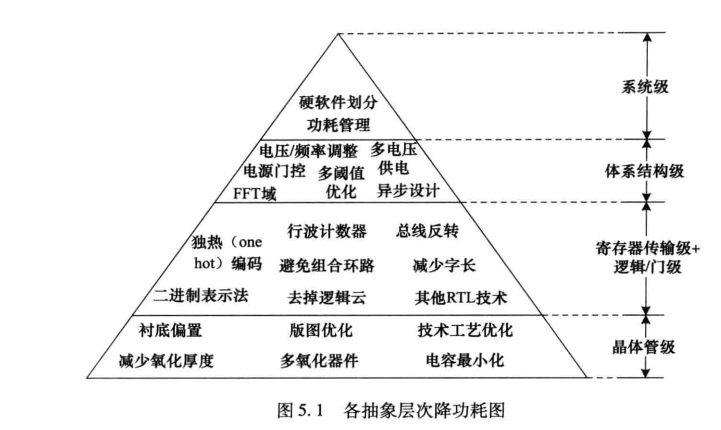

5.3 在各设计抽象层次降低功耗

层次越高,对功耗降低越有效。

5.4 系统级低功耗技术

8位处理器来处理16位数据会增加大量排序。

16位乘法使用16位处理器需要30条指令,而在8位机器上则需要127条指令。

5.5体系结构级降低功耗技术

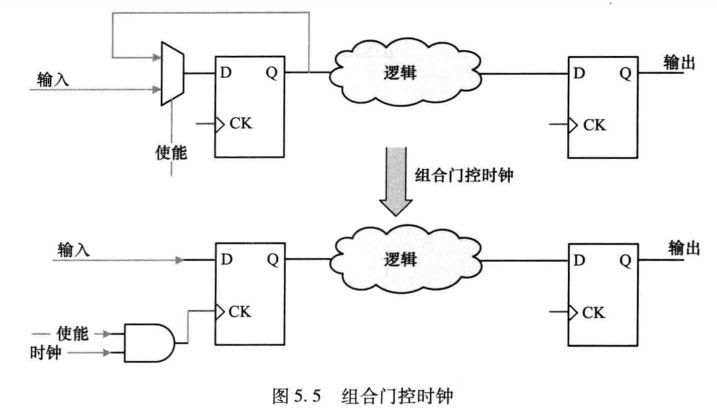

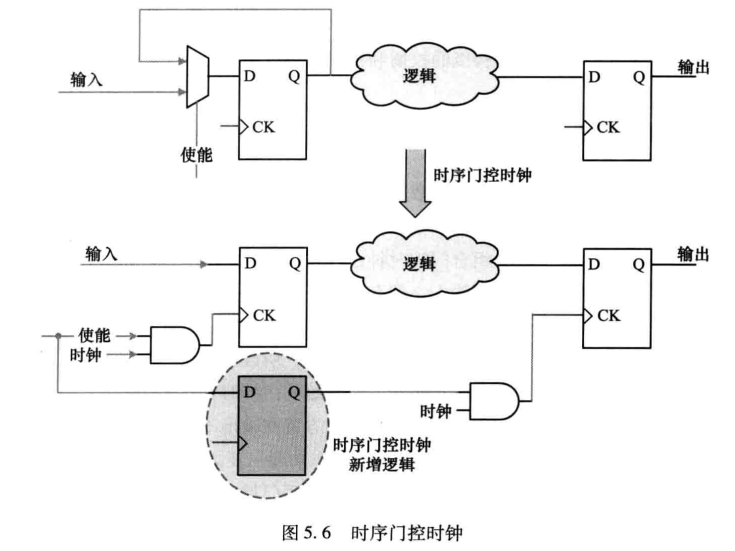

门控时钟

分为组合门控时钟和时序门控时钟

时序门控时钟需要插入额外的逻辑,所以不适合多位宽情况。

动态电压频率调节

动态电压调节(dynamic vlotage scaling,DVS)

在对频率不敏感的应用阶段中降低时钟速率和供电电压,可以在性能适度损失的情况下大幅降低功耗。

当今使用CMOS工艺的绝大多数处理器的最大频率往往与供电电压相关,所以在低频时处理器可以工作在低供电电压下。

DVS依赖特殊的硬件,可编程的DC-DC开关电压调节器,可编程时钟产生器,宽操作域的高性能处理器。

总结:DVS在满组性能需求的前提下,根据运算符在动态调整处理器/系统的电压和频率。

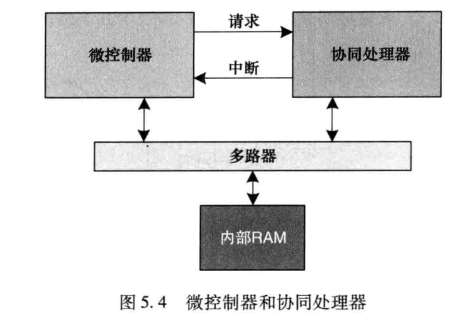

基于缓存的系统体系结构

在系统存储器和处理器之间增加缓存,预先将相关数据从主存中取到缓存中,减少对系统存储器的频繁访问,降低功耗。

对数FFT体系结构

异步设计(无时钟设计)

因为未工作元件几乎不消耗能量,所以异步电路的动态功耗接近于0。

异步电路信号交换采用双轨道编码,通信使用两根线分别表示01,两部分能可靠的彼此通信而不受线上延迟的影响。

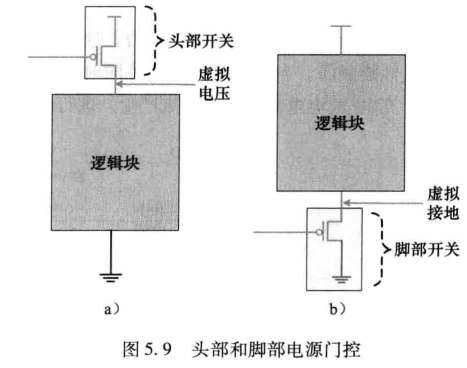

电源门控

在芯片中加入开关根据应用要求选择性切断供电电流,减少晶体管漏电流造成的功耗。

细粒度电源门控:在每个门和地之间存在一个开关晶体管,在不使用某些功能时关闭与地的连接。

粗粒度电源门控:使用电源门控晶体管控制供电网络的一部分而不是标准单元的一部分。

多阈值电压

高阈值电压较慢但是漏电较少,低阈值电压更快但漏电较多。

高阈值电压单元可以在不增加面积开销的情况下降低50%的漏电。

实际应用中可以先采用低阈值电压库进行第一遍综合以达到更好的性能来满足对时序的要求,然后对设计中不需要高性能的单元用高阈值电压单元进行替换,以减少整体功耗和设计的漏电流。

多电压供电

存储器电源门控

典型SOC中,SRAM消耗了总功耗的1/3,其余部分由时钟树和随即逻辑消耗掉。

将大块存储划分为小块存储后,读周期总数仍是相同的,但每个周期所消耗的功耗会大大增加。

5.6 寄存器传输级降低功耗

大规模ASIC中,在RTL完成时至少80%的功耗已经确定。

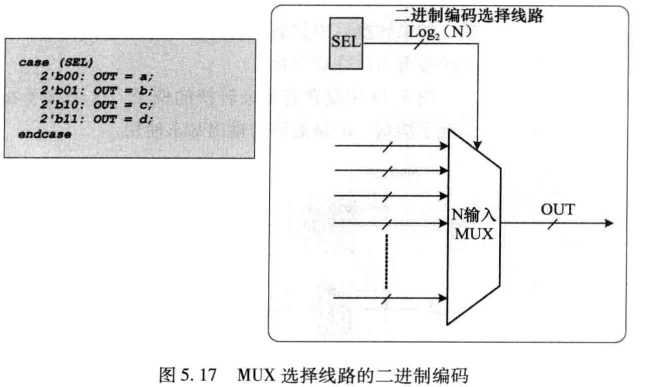

各种状态机编码类型中,格雷码最适合低功耗设计。

格雷码逻辑反转少,并且消除了依赖于状态的组合等式中存在毛刺的风险。

有时用有符号数表示法相比补码表示法可以减少逻辑翻转。

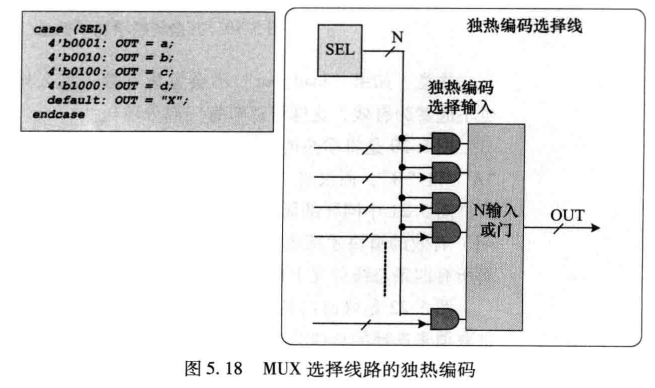

在条件判断语句中采用独热码,输出更快、更稳定,并且降低功耗。

采用独热码,MUX模块转为了N输入或门,但实现了相同功能。

5.7 寄存器级低功耗技术

通过采用新CMOS生产工艺来将功耗降低。

浙公网安备 33010602011771号

浙公网安备 33010602011771号