vivado fifo ip学习笔记

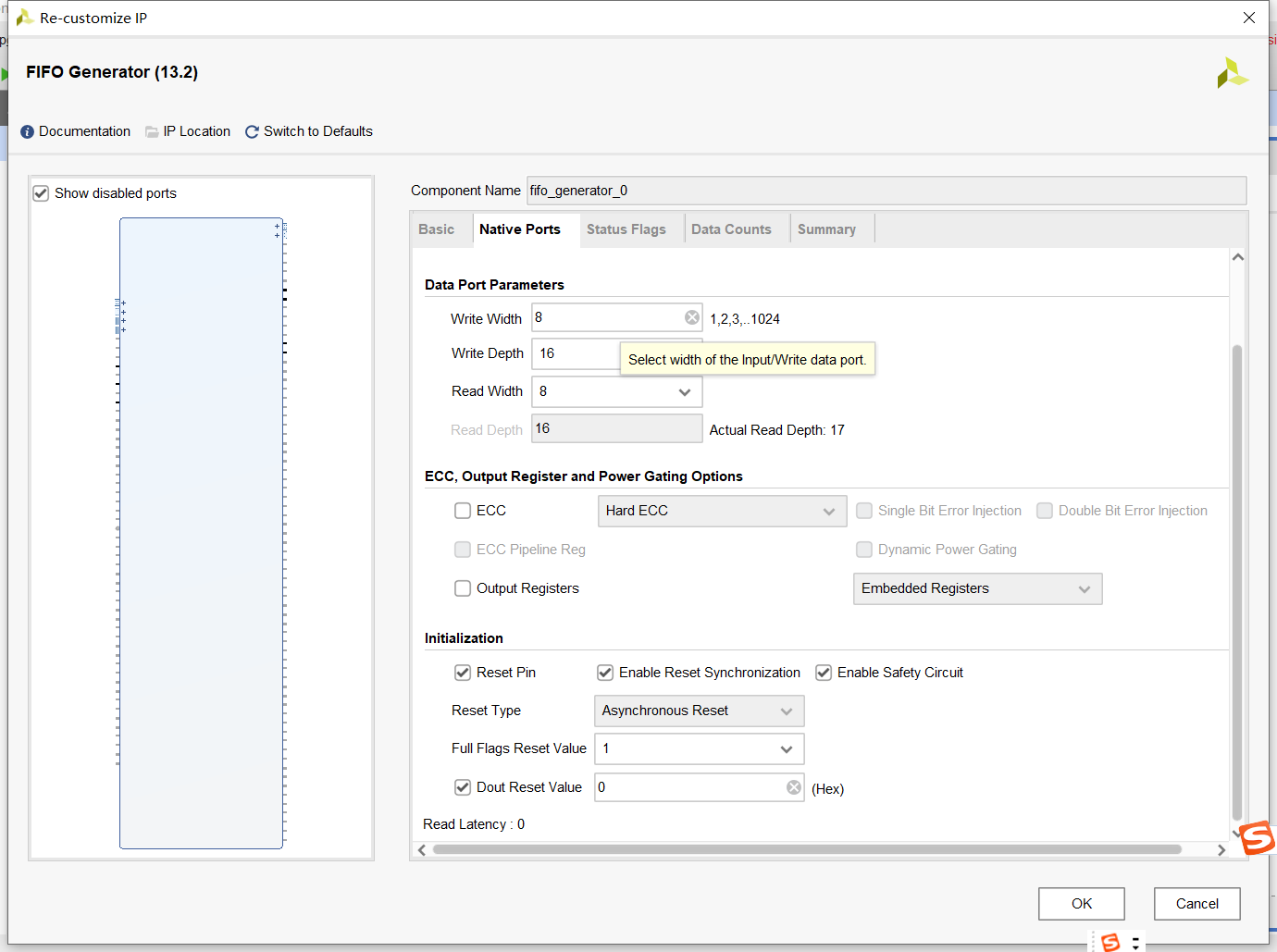

1、同步fifo(特别注意srst低电平有效)

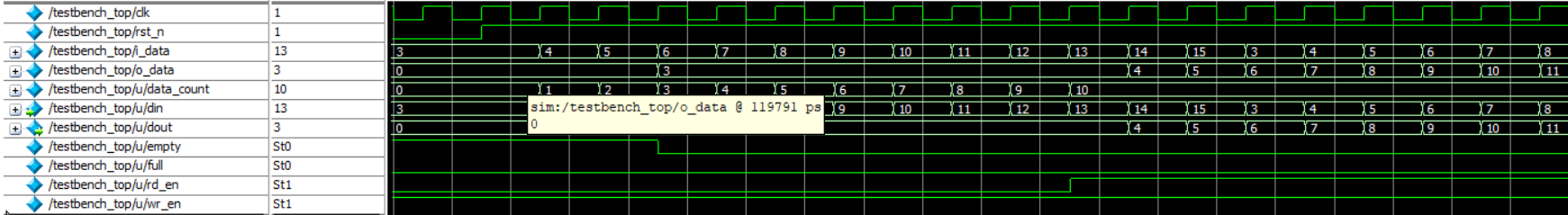

First Word Fall Through模式:输出数据提前放到线上,读出时可直接读到数据,没有延时

module vlg_design( input i_clk, //50MHz, 20ns input i_rst_n, input[7:0] din, output[7:0] dout ); wire wr_en ; wire rd_en ; wire full ; wire empty ; wire[4:0] data_count ; assign wr_en = ~full ; assign rd_en = (data_count >= 'd10 ) ; fifo_generator_0 u ( .clk(i_clk), // input wire clk .srst(!i_rst_n), // input wire srst .din(din), // input wire [7 : 0] din .wr_en(wr_en), // input wire wr_en .rd_en(rd_en), // input wire rd_en .dout(dout), // output wire [7 : 0] dout .full(full), // output wire full .empty(empty), // output wire empty .data_count(data_count) // output wire [4 : 0] data_count ); endmodule

module testbench_top(); //////////////////////////////////////////////////////////// //参数定义 `define CLK_PERIORD 20 //时钟周期设置为20ns(50MHz) //////////////////////////////////////////////////////////// //接口申明 reg clk; reg rst_n; reg[7:0] i_data ; wire[7:0] o_data ; //////////////////////////////////////////////////////////// //对被测试的设计进行例化 vlg_design u( .i_clk (clk), //50MHz, 20ns .i_rst_n (rst_n), .din (i_data), .dout (o_data) ); //////////////////////////////////////////////////////////// //复位和时钟产生 //时钟和复位初始化、复位产生 initial begin clk <= 0; rst_n <= 0; #110; rst_n <= 1; end always #(`CLK_PERIORD/2) clk = ~clk ; always@ (posedge clk or negedge rst_n)begin if(!rst_n) i_data <= 'd3 ; else if(i_data >= 'd15) i_data <= 'd3 ; else i_data <= i_data + 1 ; end endmodule

wr_en上升沿时直接读出数据没有延时。

Standard FIFO:读出时有一个时钟的延时,如下图

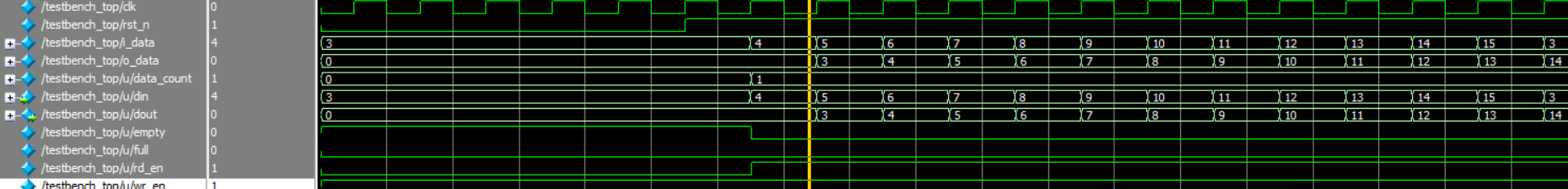

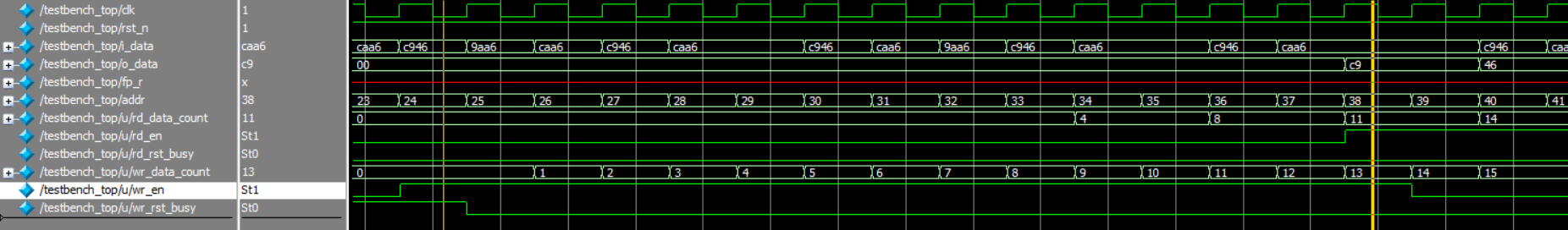

2、异步fifo(rst低电平有效)

如下图所示wr_en有效时写入14,rd_en有效时立刻读出14,没有延时

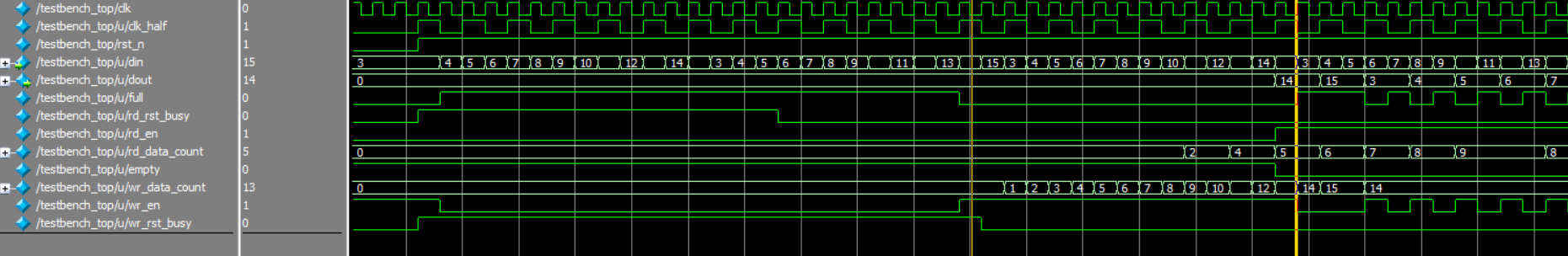

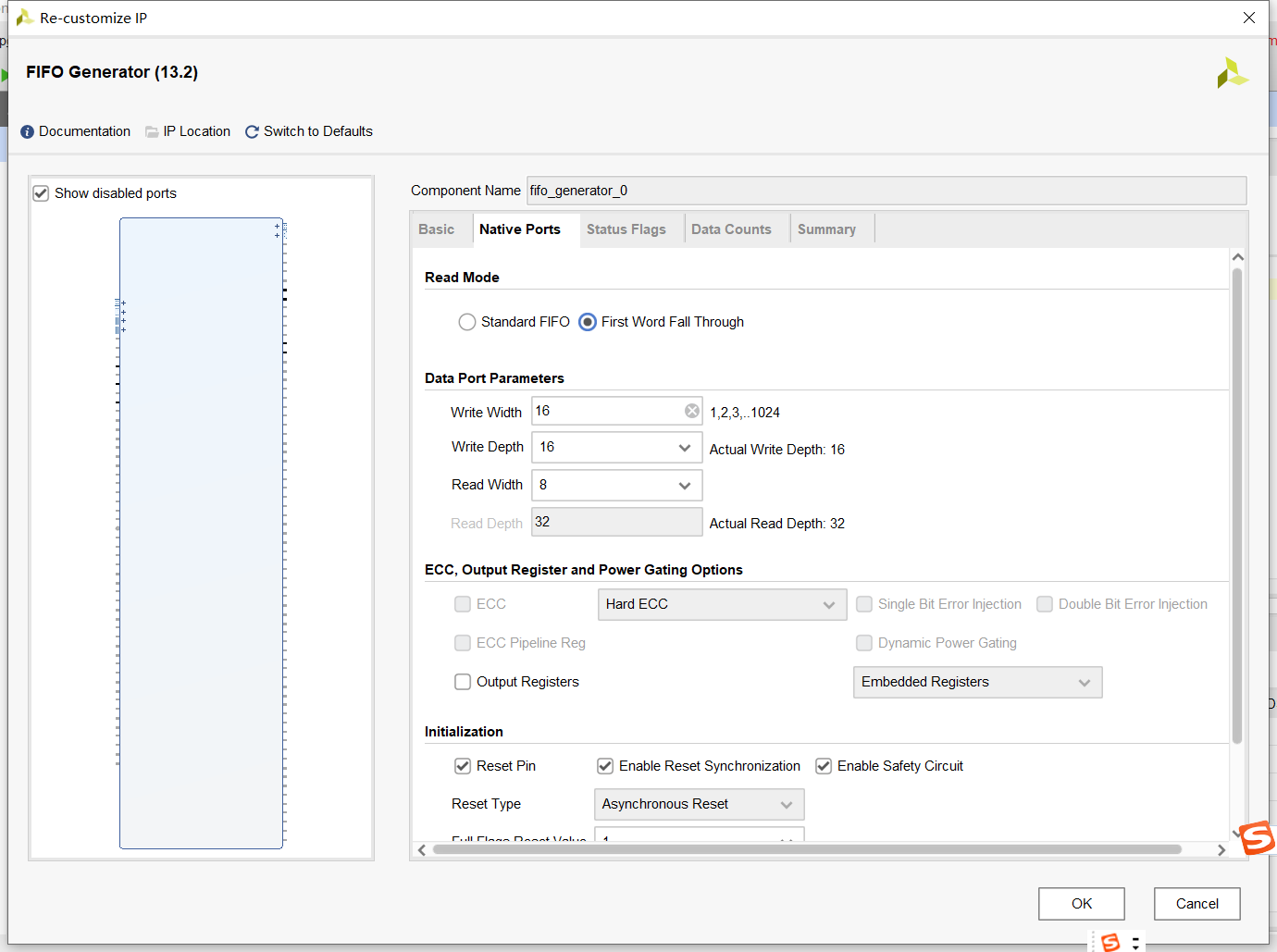

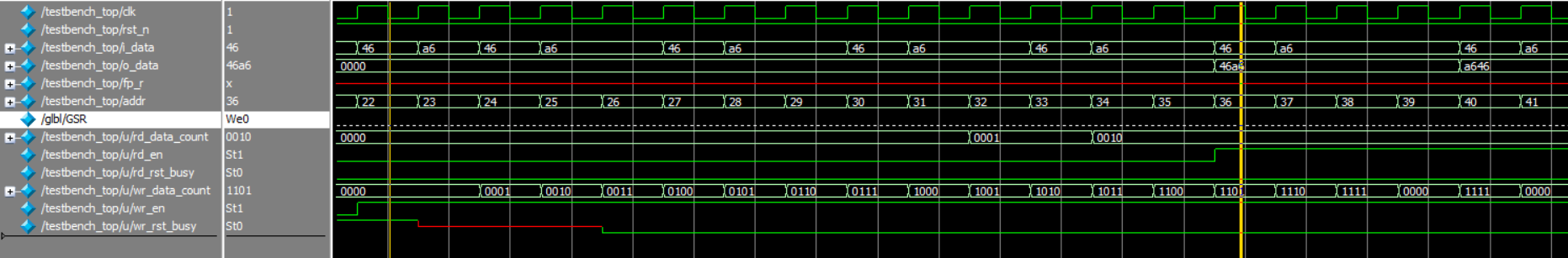

3、异步fifo,输入宽度与输出宽度不同

输入为16位,输出为8位

输入为8位输出为十六位

浙公网安备 33010602011771号

浙公网安备 33010602011771号