高速接口之DDR4

DP

USB 3.0

SATA

PCIe

PS-GTR

GigE

USB 2.0

CAN

UART

SPI

Quad SPI NOR

NAND

SD/eMMC

DDR总共有7大类信号,较简单的就是以下三类,

| PIN分类 | 名称 | 方向 | 功能描述 |

|---|---|---|---|

| 电源 | VDD | PI | 芯片主电源输入,1.2V |

| VDDQ | PI | DQ信号线电源供电,1.2V | |

| VPP | PI | DRAM激活电压,2.5V。 | |

| VREFCA | PI | 控制/命令/地址信号的参考电平。 | |

| 地 | VSS | - | 主地 |

| VSSQ | - | DQ信号参考地。 | |

| 配置 | ZQ | - | 阻抗匹配(ODT)的校准参考,接240Ω电阻到地。 |

接下是如下四类,

| PIN分类 | 名称 | IO方向 | 功能描述 |

|---|---|---|---|

| 控制信号 | ALERT_N | OUT | 报警信号,若命令/地址出现奇偶校验错误或者CRC错误,该PIN脚拉低,告知DDR Controller、 |

| TEN | IN | 测试模式使能信号,高电平使能测试模式。正常操作过程中,必须拉低。 | |

| RESET_N | IN | DDR复位信号,低电平有效。正常操作过程中,保持高电平。 | |

| PAR | IN | 命令/地址信号的奇偶校验使能,可通过寄存器禁用或者使能。 | |

| ODT | IN | 阻抗匹配使能。 | |

| CKE | IN | 时钟信号使能。通过此电平,可以控制芯片是否进入低功耗模式。 | |

| ACT_N | IN | 命令激活信号,这个信号为低电平时,可以通过A[14:16]地址信号线选择激活命令的行地址。为高电平时,Address信号线正常使用。 | |

| CS_N | IN | DDR芯片使能,用于多个RANK时的RANK组选择。 | |

| 时钟信号 | CK_N/CK_P | IN | 差分时钟信号,由DDR Controller输出。 |

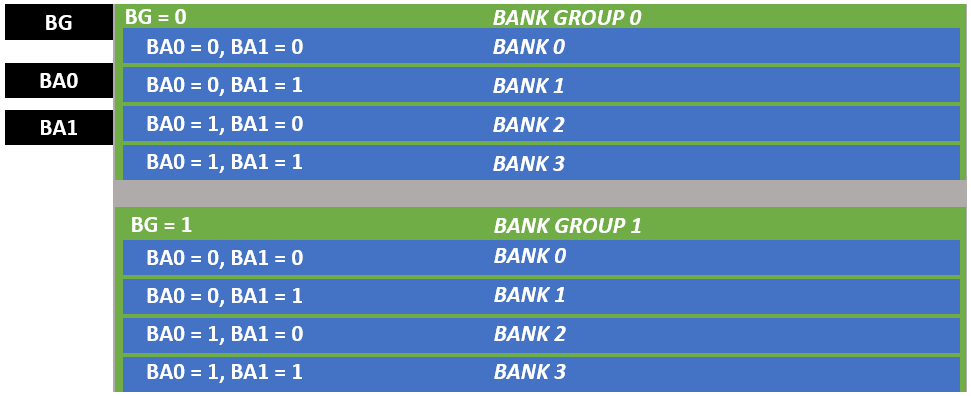

| 地址信号 | BG0 | IN | Bank Group地址选择 |

| BA[0:1] | IN | Bank地址选择 | |

| A[0:16] | IN | 地址选择信号,其中A16还有RAS_N功能,A15有CAS_N功能,A14有WE_N功能,A12有BC_N功能,A10有AP功能。 | |

| 数据信号 | DQ[0:15] | IN/OUT | 低8位数据和高8位数据信号线,共16位数据信号线。 |

| LDM/LDBI | IN/OUT | 低8位数据掩码 | |

| UDM/UDBI | IN/OUT | 高8位数据掩码 | |

| LDQS_N/LDQS_P | IN/OUT | 低8位数据选通信号 | |

| UDQS_N/UDQS_P | IN/OUT | 高8位数据选通信号 |

控制信号控制的是DDR4与DDR4控制器之间的状态切换,较复杂的是地址信号和数据信号。

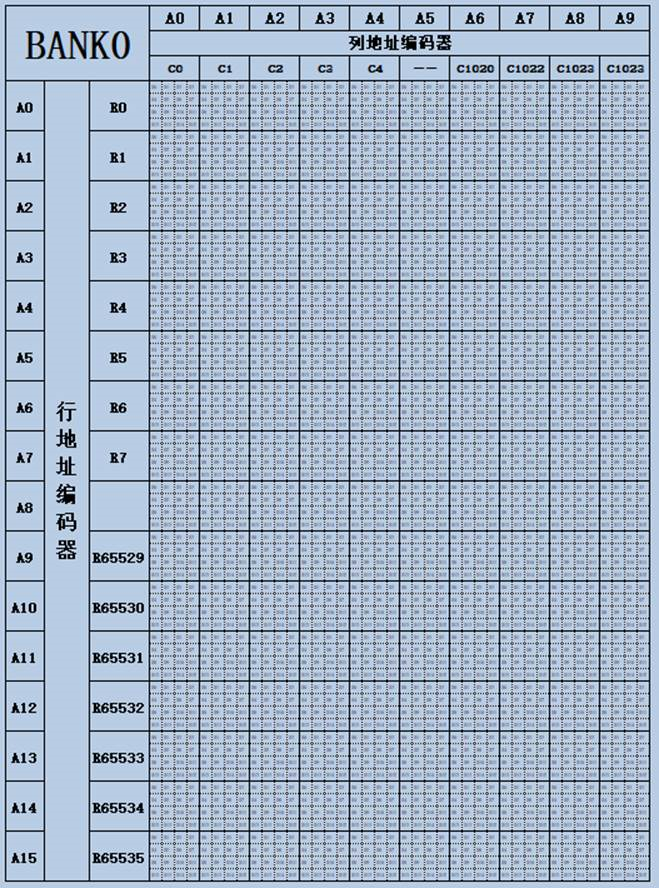

20根地址线,1根用来控制Bank group BG, 再拿2根控制每个Bank group 下的bank

这时还有17根地址线,存储块是个二维寻址,需要列和行,如果把17根一分为二,那么存储空间就比较有限,如何扩展存储空间的,很自然的就是用时间换空间,于是,再拿出1根用来表示此时此刻地址线是表示行,还是列。于是最终用来表示地址的线将是16根。

下一步就是怎么用这16根地址线的问题了。

比如,第一时刻传输,使能行地址,那么这16根地址线就代表2^16 = 65536 = 64k个行地址。紧接着第二个时刻传输,禁用行地址,本来可列也可以是64k个地址,但是数据的传输必须要考虑冗余和状态可控,于是,在列地址使能时,又拿出来6根地址线用来完成比如读写状态,刷新状态,行使能等复用功能,所以列地址线就剩下10根了,那么列的地址就为2^10 = 1024个地址。

这么看来,1个BANK就有65535*1024 = 67108864 = 64MEG个地址,如下图,

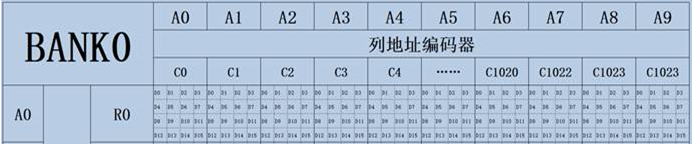

在每个地址空间中,我们一次存储16位数据。

所以1个BANK可以分成65536行,每行1024列,每个存储单元16bit。

每行可以存储102416bit=2048bit=2KB。每行的存储的容量,称为Page Size。

单个BANK共65536行,所以每个BANK存储容量为655362KB=128MB。

单个BANK GROUP共4个BANK,每个BANK GROUP存储容量为512MB。

单个DDR4芯片有2个BANK GROUP,故单个DDR4芯片的存储容量为1024MB=1GB。

原理清楚了,接下来就是硬件上如何设计了。

这里如果能跑DFSS的流程,那将很完美,但目前国内企业鲜有用这个流程来系统的选型,都是靠经验,这不是一个好现象,笔者仍会表明每一步应该用到DFSS中哪些工具,后续有时间允许时,更新对应的工具。

第一步,比如通常获取的需求就是需要给产品配置1GB的DDR。《DFSS中VOC,KJ,KANO》

ok,拿到了需求,《Concept Design, Pugh Concept Matrix, QFD1》

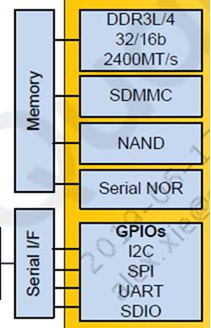

第二步,先看主平台规格书,查看主平台DDR Controller的规格,比如下面这颗主芯片,

支持DDR3L/4,32b/16b,2400MT/s,拿到这三个参数,就可以选DDR了,

第三步,选DDR,通常硬件选型有几个原则要遵循,不选太偏门冷门的器件,不选太新的器件,不选停产的器件,不选难以购买的器件,器件不要过性能,核心器件尽量选大厂,满足性能的同时要考虑成本,基于以上原则,选择目前绝大部分都为16b的DDR,用两颗DDR来实现,接下来用8Gb,2400MHz和温度过滤一下,很快就能确定用哪颗DDR。 MT40A512M16JY-083E

选型到此就结束了,接下来就是硬件设计了,为了完成DDR设计,需要认真阅读DDR规格书,获取DDR的电气特性和外围电路(这一条通用),首先需要分类,按照之前DDR信号类型把DDR分为7类,然后分类设计,这也有助于后期的仿真分析。前面已分类,不再赘述。

接下来就是电路的搭建了,注意事项如下,

控制信号中,需要注意CS0和CS1,2个片选信号的可以用来进行,多RANK内存容量扩展的,说明DDR控制器,最多支持2组RANK。每组RANK分配单独的片选信号。我们此处设计2个16位芯片组成1个RANK,即CS0要同时接在目前选的2个DDR颗粒的CS上,组成菊花链。其余控制信号一般无时序要求,能传递逻辑即可。

地址信号通常要参考时钟信号,来进行寻址,所以地址信号要严格与时钟信号保持长度一致,来保证所有地址位在采样的时候同时到达。因为同一块单板上,每根线上电子的传递速度是一样的,所以信号线长度约长,信号越晚到达,信号线长度越短,信号越早到达,地址采样的时候,是有时间期限的,所以,所有的地址信号必须保证在采样时间范围内,全部到达,因此要求地址线相对时钟线进行长度控制。前面一节我们讲了内存寻址原理,先用BG信号选择BANK GROUP,再用BA信号进行BANK选择,再用A[0:16]进行行列选择,再用A[0:16]进行列选择,完成寻址。可以看到,Address信号在进行行选择和列选择时,BG和BA信号都是保持的,所以BG信号和BA信号的等长要求会相对略宽。

DDR控制器有2根BG信号,2根BA信号,17根Address信号,同一个RANK有2个DDR颗粒,每个DDR颗粒有1根BG信号,2根BA信号,17根Address信号,前面CS0同时连接了2个DDR颗粒的片选,所以寻址时两颗DDR会被同时片选,那么DDR控制器如何区分开寻址其中1颗DDR颗粒呢?硬件又该怎么连接?其实很简单,根据上节讲的内存寻址原理,我们知道每个DDR颗粒有2个BANK GROUP(1根BG信号),4个BANK(2根BA信号),与CS扩展容量的原理一致,我们把BG0接在DDR颗粒1上,BG0拉高拉低,我们可以寻址CHIP1的8个BANK。BG1接在DDR颗粒2上,BG1拉高拉低,我们可以寻址CHIP1的8个BANK。BA、ADDR进行菊花链连接,同时接在2颗DDR芯片上。

接下来,我们看看数据信号的链接,数据信号是内部分组的,由于DDR数据信号传输的时候双边沿数据传输,而且如果所有信号都参考时钟去做等长,会导致等长控制非常困难,增加DDR的设计难度,所以聪明的人类想出了另外一招,额外增加数据选通信号来作为数据信号的采样时钟,每8位信号,参考一组差分。所以我们很轻易可以看出DDR控制器有4组DQS差分信号,32根数据信号。我们的RANK中有2个DDR颗粒,每个颗粒有2组DQS差分信号,16根数据信号。所以

控制器的DQS[0:1]连接DDR CHIP0的DQS[0:1],

控制器的DQ[0:15]连接DDR CHIP0的DQ[0:15]。

控制器的DQS[2:3]连接DDR CHIP1的DQS[0:1],

控制器的DQ[16:31]连接DDR CHIP1的DQ[0:15]。至此所有信号连接完成。接下来是阻抗匹配,地址信号都需要外部加49欧姆匹配电阻到电源或者GND,数据信号,则不需要。因为DDR内部集成ODT功能,只需要通过配置,即可完成每组数据线的阻抗匹配。

浙公网安备 33010602011771号

浙公网安备 33010602011771号