ZYNQ AXI-Uartlite串口回环(一) (基于Vivado 2024.2和Vitis 2024.2)

创建Vivado工程

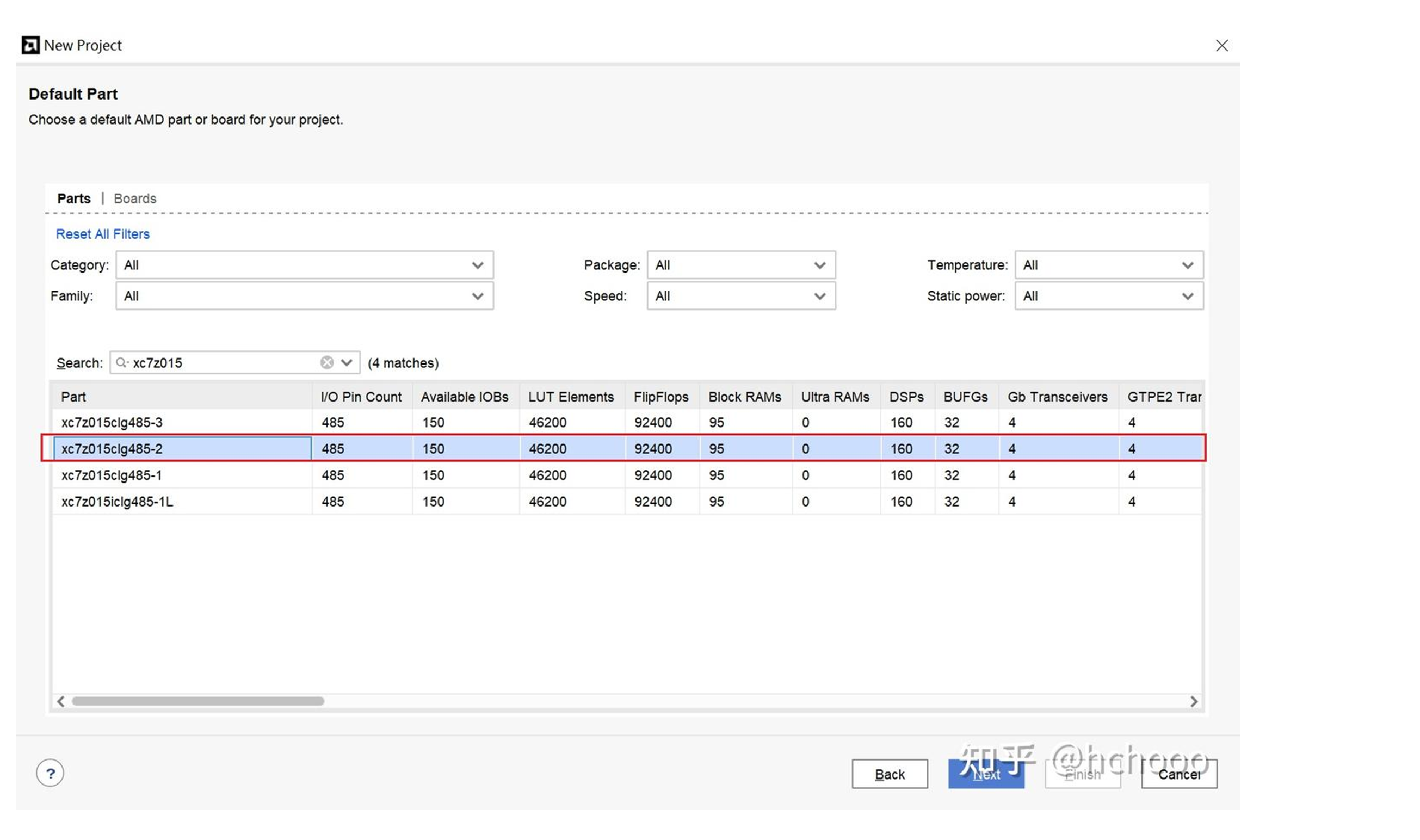

选择vivado工程目录,工程命名为axi_uartlite_loopback,器件为xc7z015clg484-2

工程创建好后创建Block Design,点击+创建ZYNQ Processing System IP核。

双击进入PS配置界面,这里选择GP0 Master接口,后续将AXI Uartlite挂载到此处。

PS端串口使能UART1,选择根据开发板引脚分配配置到MIO48-49

根据开发板实际资源,配置引脚电平标准

根据开发板实际资源,配置PS端输入时钟,输出时钟

根据开发板实际资源,配置DDR3

使能中断

PS配置完成,点击OK保存。再次点击+添加AXI Uartlite,配置波特率(后续如果需要更改波特率需要回到这里修改)。这里配置不使用奇偶校验。

让vivado软件自动帮我们连接,并添加必要的IP。随后手动将AXI Uartlite的中断信号连接到PS到中断

在Address Editor界面确认地址已分配,如果没有分配可右击选择Assign All

回到Diagram界面验证设计正确性

Generate Output Products

Create HDL Wrapper

添加AXI Uartlite输入输出引脚约束

set_property PACKAGE_PIN V18 [get_ports uart_rtl_0_txd]

set_property PACKAGE_PIN W18 [get_ports uart_rtl_0_rxd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rtl_0_txd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rtl_0_rxd]

点击生成比特率。等待综合、实现完成后导出硬件文件xsa,注意包含比特流。

启动Vitis 2024.2

浙公网安备 33010602011771号

浙公网安备 33010602011771号