实现 nRF54L15 设备上的 sQSPI 应用程序所需的必要配置和要求

1:以下结构展示了 sdk-nrfxlib 仓库中的相关文件和目录:

nrfxlib/

├──...

└── softperipheral/

├── include

│ ├── softperipheral_meta.h

│ └── softperipheral_regif.h

├── ...

└── sQSPI

├── include

│ ├── hal

│ │ └── nrf_qspi2.h

│ ├── nrf54l15

│ │ ├── sqspi_firmware.h

│ │ ├── sqspi_firmware_v0.1.0.h

│ │ └── ...

│ ├── nrf_sp_qspi.h

│ ├── nrfx_config_qspi2.h

│ ├── nrfx_qspi2.h

└── src

└── nrfx_qspi2.c

为了使 sQSPI 应用程序正确运行,它需要驱动代码(内部路径)使用的特定头文件以及用于 nrfx(外部依赖)的特定头文件。必须在构建环境的包含路径列表中包含这些文件的路径。以下列表是必要的路径

internal paths:

1. softperipheral/include - Soft peripherals register interface and metadata(软件外设寄存器接口和元数据) 2. softperipheral/sQSPI/include - sQSPI register interface and driver header(sQSPI 寄存器接口和驱动头文件) 3. softperipheral/sQSPI/include/nrf54l15 - The sQSPI firmware for the Fast Lightweight Perpipheral Processor (FLPR)

External dependencies(外部依赖)

1.nrfx - 包含主 nrfx 头文件( nrfx.h ) 2.nrfx/drivers/include - 包含 nrfx 驱动程序头文件,例如,nrfx_dppi.h 文件 3.应用程序特定头文件和宏的路径。例如, nrfx_glue.h 、 nrfx_log.h 或配置头文件

2:编译源文件

为了使 sQSPI 应用程序正常运行,您必须从源文件 nrfx_qspi2.c 编译驱动程序实现

3:Application core and FLPR configuration(应用核和 FLPR 配置)

必须调整 nRF54L15 SoC 的设置,以使其运行在最高的基本时钟频率,要使用以下任何设置,请确保已完成以下操作:

3.1:您已为 sQSPI 驱动程序使用的数据指针分配了内存。该内存独立于 RAM 配置小节中概述的内存。它被指定为用于通信的共享内存,而不是包含 sQSPI 可执行代码

3.2:您已启用对 MEMCONF 外设的 FLPR 访问,此访问对于正确停用 sQSPI 是必要的

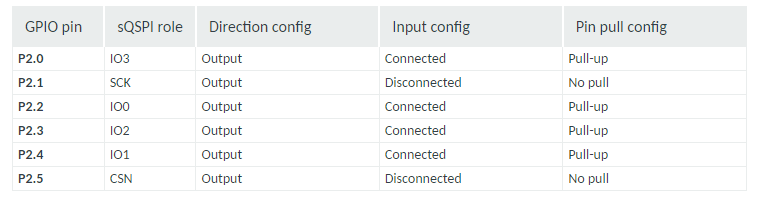

3.3:GPIO的配置

该表详细说明了在 sQSPI 应用中使用的每个 GPIO 引脚的配置。以下选项可用,前提是 FLPR 核心可以访问这些端口和引脚:

sQSPI 驱动提供默认的 GPIO 配置和复用。您可以通过将 nrfx_qspi2_cfg_t.skip_gpio_cfg 和 nrfx_qspi2_cfg_t.skip_pmux_cfg 设置为 false 来应用此设置

以下代码片段显示了应用程序代码如何分配所需的引脚并覆盖 sQSPI 驱动程序的默认配置:

//qspi pin config

static nrfx_qspi2_cfg_t qspi_config = {

.pins =

{

.sck = NRF_PIN_PORT_TO_PIN_NUMBER(1, 2),

.strobe = NRFX_QSPI2_PINS_UNUSED,

.io =

{

NRF_PIN_PORT_TO_PIN_NUMBER(2, 2),

NRF_PIN_PORT_TO_PIN_NUMBER(4, 2),

NRF_PIN_PORT_TO_PIN_NUMBER(3, 2),

NRF_PIN_PORT_TO_PIN_NUMBER(0, 2),

},

},

.skip_gpio_cfg = false,

.skip_pmux_cfg = false,

};

nrfx_qspi2_dev_cfg_t qspi_dev_config = {.csn_pin = NRF_PIN_PORT_TO_PIN_NUMBER(5, 2),

.sck_freq_khz = ...,

...

};

nrfx_qspi2_init(&qspi, &qspi_config);

if (qspi_config.skip_gpio_cfg == false) { //This overrides the driver's default configuration

// Set drive strength E0E1, as it is non-standard.

nrf_gpio_cfg(qspi_dev_config.csn_pin, NRF_GPIO_PIN_DIR_OUTPUT, NRF_GPIO_PIN_INPUT_DISCONNECT, NRF_GPIO_PIN_NOPULL,

NRF_GPIO_PIN_E0E1, NRF_GPIO_PIN_NOSENSE);

nrf_gpio_cfg(qspi_config.pins.sck, NRF_GPIO_PIN_DIR_OUTPUT, NRF_GPIO_PIN_INPUT_DISCONNECT, NRF_GPIO_PIN_NOPULL,

NRF_GPIO_PIN_E0E1, NRF_GPIO_PIN_NOSENSE);

for (int i = 0; i < 4; i++) {

nrf_gpio_cfg(qspi_config.pins.io[i], NRF_GPIO_PIN_DIR_OUTPUT, NRF_GPIO_PIN_INPUT_CONNECT,

NRF_GPIO_PIN_PULLUP, NRF_GPIO_PIN_E0E1, NRF_GPIO_PIN_NOSENSE);

}

}

if (qspi_config.skip_pmux_cfg == false) { //This overrides the driver's default configuration

// Set pin source as FLPR.

nrf_gpio_pin_control_select(p_config->pins.sck, NRF_GPIO_PIN_SEL_VPR);

nrf_gpio_pin_control_select(p_config->csn_pin, NRF_GPIO_PIN_SEL_VPR);

for (int i = 0; i < NRFX_QSPI2_MAX_NUM_DATA_LINES; i++) {

nrf_gpio_pin_control_select(p_config->pins.io[i], NRF_GPIO_PIN_SEL_VPR);

}

}

此外,sQSPI 应用需要 FastPad 偏置配置,以便在 SCLK 上以高频运行

// If drive strength (E0E1), set bias on the gpio port to 3 (FastPad configuration) volatile unsigned* reg = (unsigned*)(0x50050430); *reg = 0x3;

浙公网安备 33010602011771号

浙公网安备 33010602011771号