stm32硬件I2C时钟为啥不稳定

今天在做i2c实验遇到了一个问题:

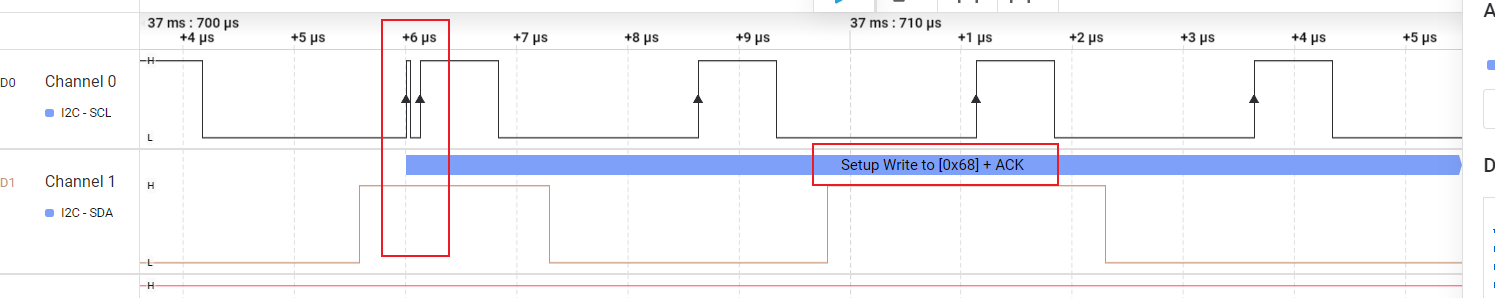

用逻辑分析仪抓取scl、sda波形,可以看到scl时钟有抖动的情况,导致解析出错误的从机地址0x68,正确从机地址应该是0x50。

疑惑点在于为什么地址错误了从机还会应答?怀疑可能存在的情况:

- logic软件解析错误,实际mcu和at24c02通讯数据是正常的(软件错误解析把第一个毛刺信号当成了一个时钟周期),为什么这样怀疑呢下面给出证据:

- 从机地址如果是发错了那么从机是不可能给出ack信号,由此有理由怀疑问题出在了上位机解析协议。

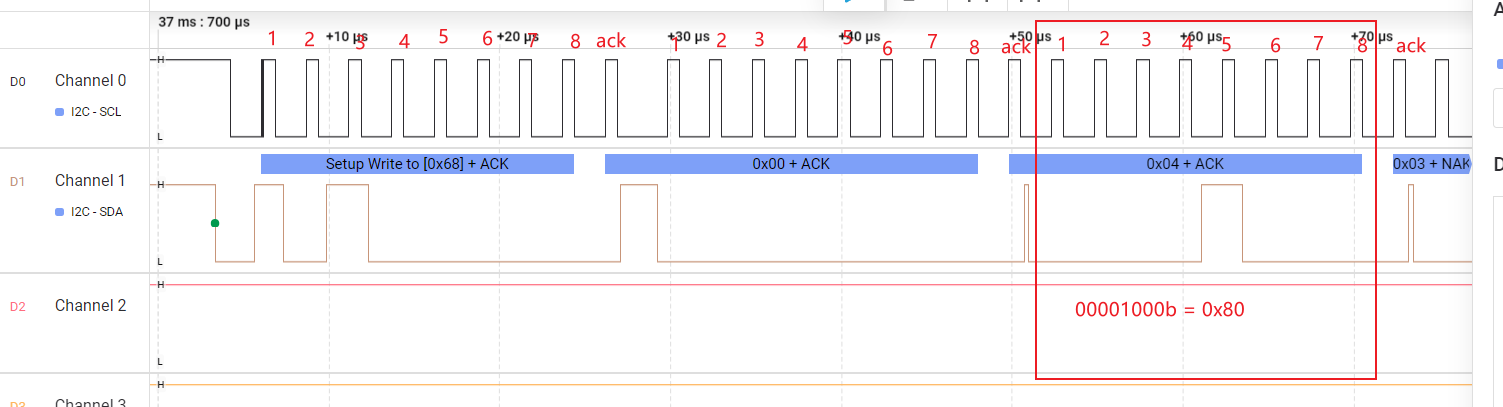

验证:持续发送buff数组中数据到at24我们可以分析解析错误地址的波形有这样的特点,如果忽略第一个毛刺信号,手动去计算数据都能和发出的对的上

总结:由于 SCL 起始阶段存在毛刺,上位机逻辑分析仪在起始位后的第一个时钟发生位对齐错误(bit slip),从而导致地址字段解码错误。

ps:上图二进制换算十六进制错了,应该是0x08.

int main(void)

{

uint8_t buff[8] = {8,7,6,5,4,3,2,1};

uint32_t i = 0xfffff;

i2c1_init();

//oled_init();

//at24c02_read(0,buff,8);

while(1)

{

i = 0xffffff;

while(i--);

at24c02_writepage(0,buff,8);

at24c02_waitnobusy();

}

}

浙公网安备 33010602011771号

浙公网安备 33010602011771号