CACHE 介绍

内存

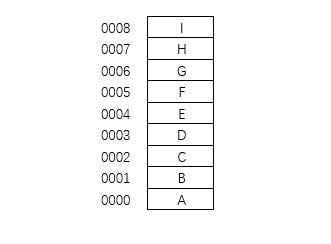

要想理解cache,先理解内存。内存的简单表示如下图,内存里面的内容的查找是根据地址来进行的,也就是说内存包含两点①地址②内存的内容(存的数据),根据地址来找数据。

上图的0000~0008是地址,A~I是存的数据,cpu根据地址去寻找数据。图中的一个字母代表一个字节的数据。

CACHE

cache和数据的三种映射关系

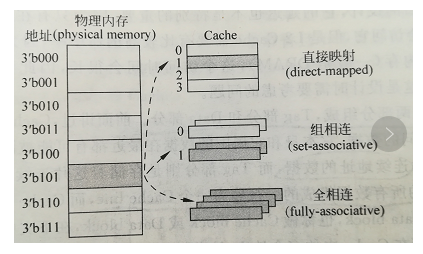

cache中的数据就是物理内存中的数据的子集,那么对于物理内存的一个数据,根据cache中可以放置这个数据位置的多少,可以分为三种:

- 这个数据只能放在cache的某一个位置,称为直接映射的cache

- 这个数据可以放在cache任一位置,称为全相连的cache

- 这个数据可以放在cache某几个位置,称为组相连的cache

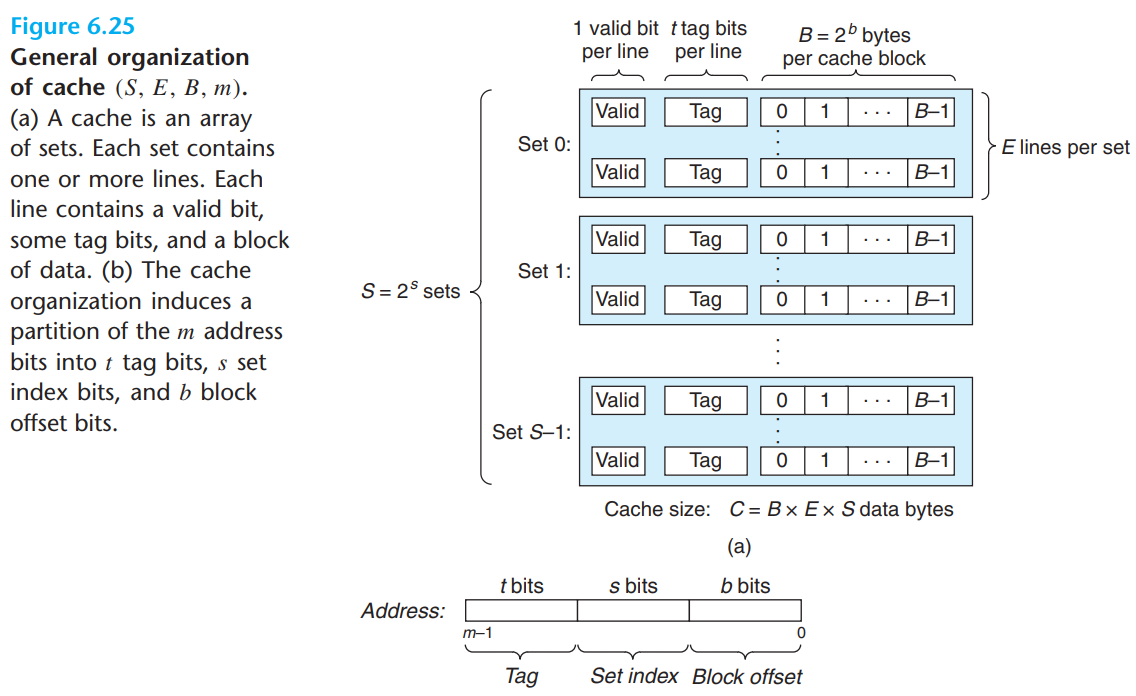

cache 结构

cache的结构其实和内存的结构类似,也包含地址和内容,只是cache的内容除了存的数据(data)之外,还包含存的数据的物理内存地址信息(tag),因为CPU发出的寻址信息都是针对物理内存发出的,所以cache中除了要保存数据信息之外,还要保存数据对应的地址,这样才能在cache中根据物理内存的地址信息查找物理内存中对应的数据。(当然为了加快寻找速度,cache中一般还包含一个有效位(valid),用来标记这个cache line是否保存着有效的数据)。一个tag和它对应的数据组成的一行称为一个cache line。如下图所示,下表中的一行就是一个cache line。

一个物理内存地址只存储一个字节数据,但是一个cache line可以存储多个字节数据,

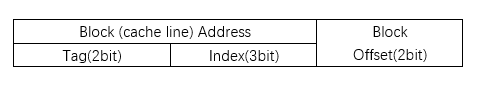

物理内存地址被分为tag、index 和 block offset。

举例来讲,对于一段物理内存(block),该物理内存上每个字节的地址划分为以下几段:

block offset占2bit,所以一个cache line存储4字节数据

直接映射(Direct Mapping)

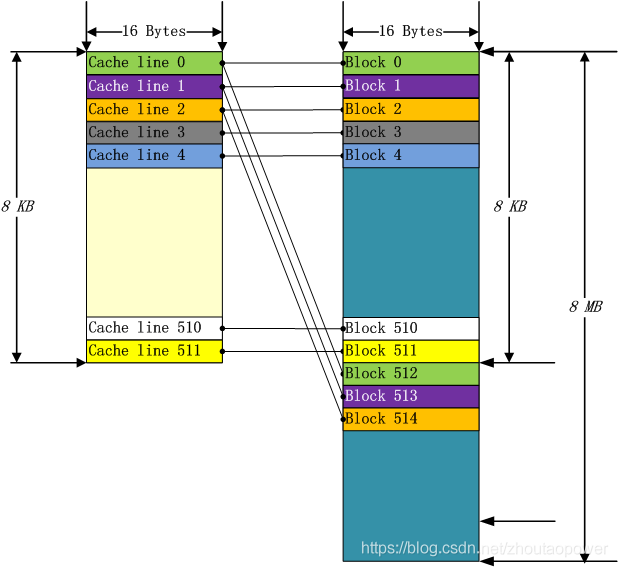

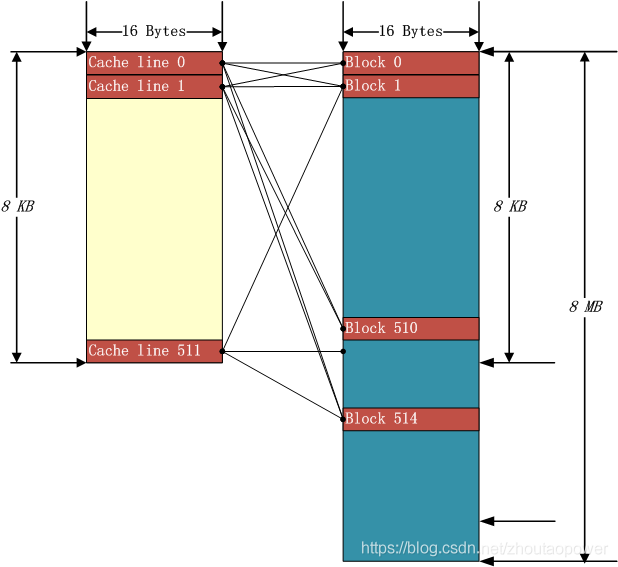

物理内存中的数据到cache的映射关系如下图所示,block offset占4bit

物理内存的每个数据只能映射到某个cache line。

在直接映射中,主存块地址(Block Address)通过模运算确定Cache中的目标行(Cache Line):

- 主存块号:主存地址按块大小分割后的块编号。

- Cache行数:Cache中可存储的块数量。

行选择

- Index通过截取主存地址的低位部分,直接对应Cache的行号。

- 示例:

- Cache行数 = 8<span class="katex"><span class="katex-html"><span class="base"><span class="strut"><span class="mord"><span class="mord"><span class="msupsub"><span class="vlist-t"><span class="vlist-r"><span class="vlist"><span class="pstrut"><span class="sizing reset-size6 size3 mtight"><span class="mord mtight">,则Index占3位。

- 主存地址

0x12345678的Index为低3位0x7,直接选择Cache的第7行。

与Tag的关系

- Index仅用于选择行,Tag用于验证该行是否存储了目标主存块。

- 若Tag匹配且有效位为1,则命中;否则未命中。

缺点:冲突率高(多个主存块可能竞争同一Cache行),导致命中率下降。

全相连映射(Fully Associative Mapping)

全映射就是所有cache line可以对应所有地址,即物理内存数据可以存在任一cache line,index所占bit数为0。查找Cache命中与否的代价(Over head)很高,只根据要寻址的地址的tag来逐一与cache中的tag字段比较,如果有与之匹配的cache line,也就是cache hit了,如果遍历整个cache,也没有找到匹配的cache line,那就是cache miss了。

n 路组相联映射(n-ways Set-Associative mapping)

组相联映射(Set-Associative Mapping)结合了直接映射和全相联映射的特点,通过组(Set)和组内全相联的方式实现高效查找。以下是其查找Cache行的详细步骤和机制:

从主存地址中提取Tag、Set Index和Offset,使用Set Index定位Cache中的某一组,在选定的组内,并行比较所有行的Tag与主存地址的Tag,若某行的Tag匹配且有效位为1,则命中;否则未命中

带 Cache 的 CPU 内存读写

在CPU与主存之间增加了Cache之后,便存在数据在CPU和Cache及主存之间如何存取的问题。读写各有2种方式。

1. 贯穿读出式(Look Through)

该方式将Cache隔在CPU与主存之间,CPU对主存的所有数据请求都首先送到Cache,由Cache自行在自身查找。如果命中,则切断CPU对主存的请求,并将数据送出;不命中,则将数据请求传给主存。

该方法的优点是降低了CPU对主存的请求次数,缺点是延迟了CPU对主存的访问时间。

2. 旁路读出式(Look Aside)

在这种方式中,CPU发出数据请求时,并不是单通道地穿过Cache,而是向Cache和主存同时发出请求。由于Cache速度更快,如果命中,则 Cache在将数据回送给CPU的同时,还来得及中断CPU对主存的请求;不命中,则Cache不做任何动作,由CPU直接访问主存。

它的优点是没有时间延迟,缺点是每次CPU对主存的访问都存在,这样,就占用了一部分总线时间。

3. 写穿式(Write Through)

任一从CPU发出的写信号送到Cache的同时,也写入主存,以保证主存的数据能同步地更新。

它的优点是操作简单,但由于主存的慢速,降低了系统的写速度并占用了总线的时间。

4. 回写式(Write Back)

为了克服贯穿式中每次数据写入时都要访问主存,从而导致系统写速度降低并占用总线时间的弊病,尽量减少对主存的访问次数,又有了回写式。

它是这样工作的:数据一般只写到Cache,这样有可能出现Cache中的数据得到更新而主存中的数据不变(数据陈旧)的情况。但此时可在Cache 中设一标志地址及数据陈旧的信息,只有当Cache中的数据被再次更改时,才将原更新的数据写入主存相应的单元中,然后再接受再次更新的数据。这样保证了 Cache和主存中的数据不致产生冲突。

浙公网安备 33010602011771号

浙公网安备 33010602011771号