沁恒微 Ble 芯片CH58x/CH59x 硬件设计说明 - 实践

理一理沁恒微蓝牙芯片的硬件设计注意事项 ..... 矜辰所致前言

我们学习沁恒微的 Ble 芯片也有一段时间了,主要都是通过 EVT 进行代码上的一些学习,但是实际应用,我们总归是要自己设计产品的。

所以本文我们主要就是理一理 沁恒微 蓝牙芯片的硬件设计的注意事项。

相关文章:

沁恒微 RISC-V 蓝牙 CH5xx GPIO使用说明

沁恒微 RISC-V 蓝牙芯片低功耗测试

系列博文目录:

【导航】沁恒微 RISC-V 蓝牙 入门教程目录 【快速跳转】

.

我是矜辰所致,全网同名,尽量用心写好每一系列文章,不浮夸,不将就,认真对待学知识的我们,矜辰所致,金石为开!

目录

一、 基本资料说明

对于硬件设计部分,官方也已经给了足够全的资料。

1.1 文档资料

在不同型号的 EVT 包下,都会有对应的设计资料(这些东西都是沁恒微官网直接能够下载的):

上面是 CH585 的资料,提供开发板的原理图和 PCB 。可能有些型号没有 PCB 文件,也提供了 PDF 的文件,他们的设计规范都是通用的。

1.2 封装库

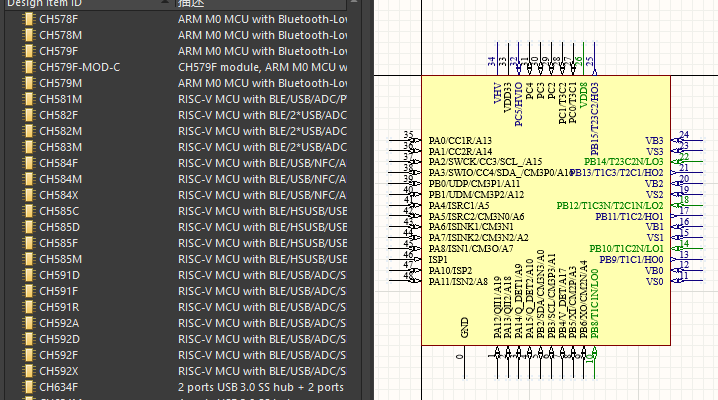

官方可以下载所有芯片的原理图 和 PCB 库(里面也包含天线的 PCB 库,按照设计官方文档说明的设计规则选择使用即可 ):

原理图库 :

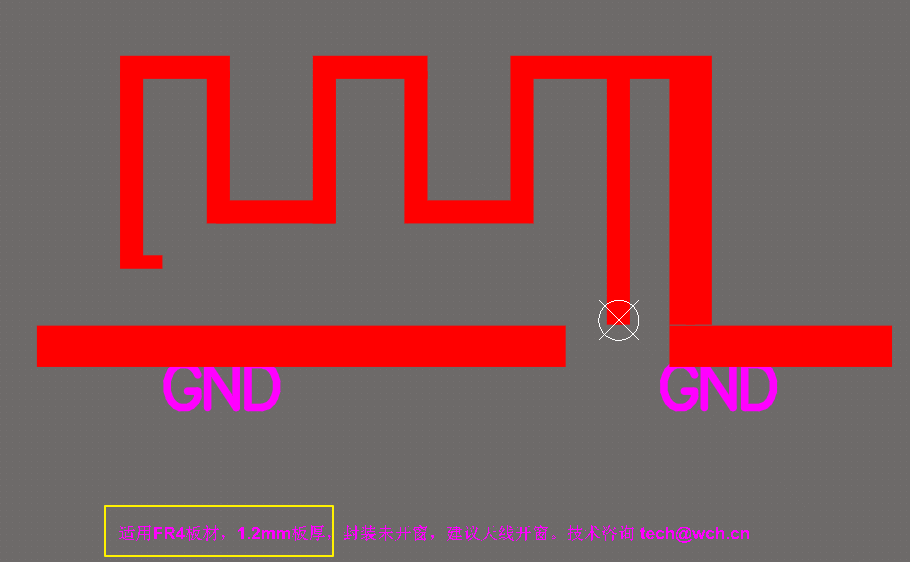

PCB 封装天线示例:

二、 设计说明

除了基本的设计资料,当然还需要对一些特定的部分有一定的认识,比如晶振, GPIO 特殊引脚等细节。本小节我们对一些关键的部分进行说明。

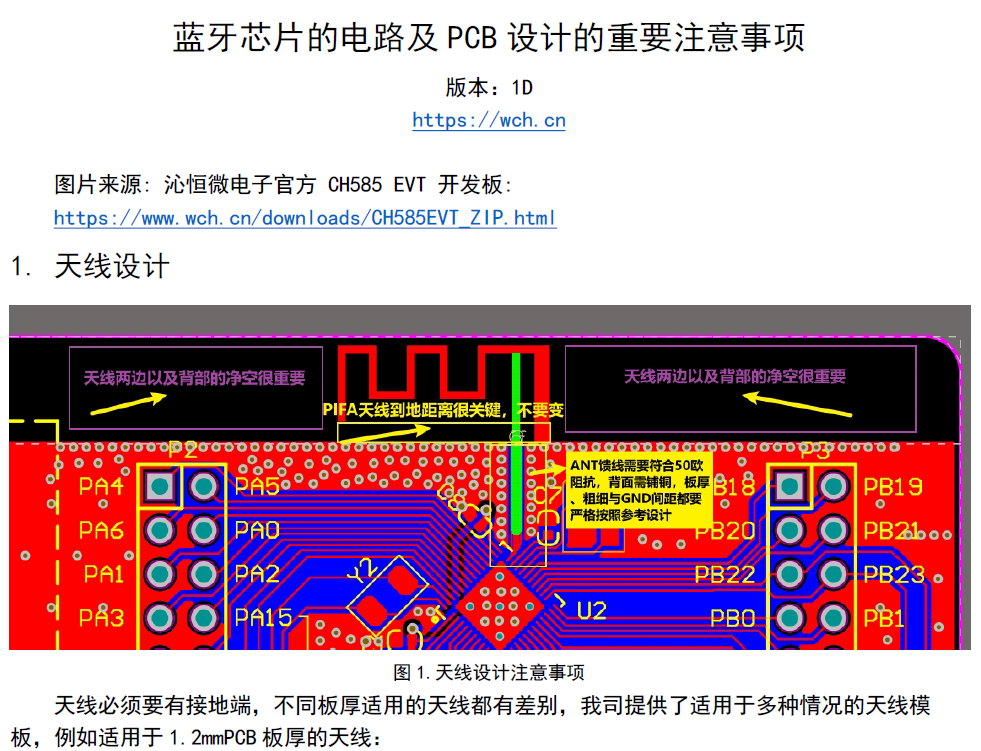

2.1 天线

把最受关注的 天线 放在第一位。

在官方文档《 蓝牙芯片的电路及PCB设计的重要注意事项 》(就在 EVT 目录的 PUB 文件夹下面)有详细的说明:

不止一次提过,使用学习一款芯片官方有的文档一定要去看,很多东西其实都给了,但是往往我们还费时费力的去网上到处找,还不一定找到合适的答案。

PCB 设计部分的资料篇幅不多,花不了大家多少时间,但是很重要,自己设计之前大家还是要自己下载看看。

这里额外说明一些基本事项:

- 天线设计的通用注意事项:比如 ANT 线尽可能的短,走线平滑,确保净空区,远离金属等。

- 官方的开发本使用的都是板载 PCB 天线,提供了设计说明,用户也可以外接 SMA/IPEX 的天线 。

- 也可以是陶瓷天线,但是要注意,虽然理论上来说陶瓷天线 会比 PCB 天线效果好,但是必须严格按照陶瓷天线规范设计,布局、地平面、净空等等,如果没有处理好,可能还不如 PCB 天线。

- 建议预留 π 型匹配,以便后期做一些认证的时候进行参数匹配,正常使用 0 Ω 电阻直连即可。

- 官方提供了不同的天线封装,在尺寸允许的情况下,尽量用大的封装。

这里有一个 ANT线 50Ω 阻抗匹配的表格仅供参考:

| 板厚/mm | 线宽/mil | 距 GND 间隙/mil |

|---|---|---|

| 0.6 | 19.8 | 6 |

| 0.8 | 23.0 | 6 |

| 1.0 | 25.0 | 6 |

| 1.2 | 26.5 | 6 |

| 1.6 | 28.1 | 6 |

表格来自:https://www.cnblogs.com/gscw/p/17387204.html

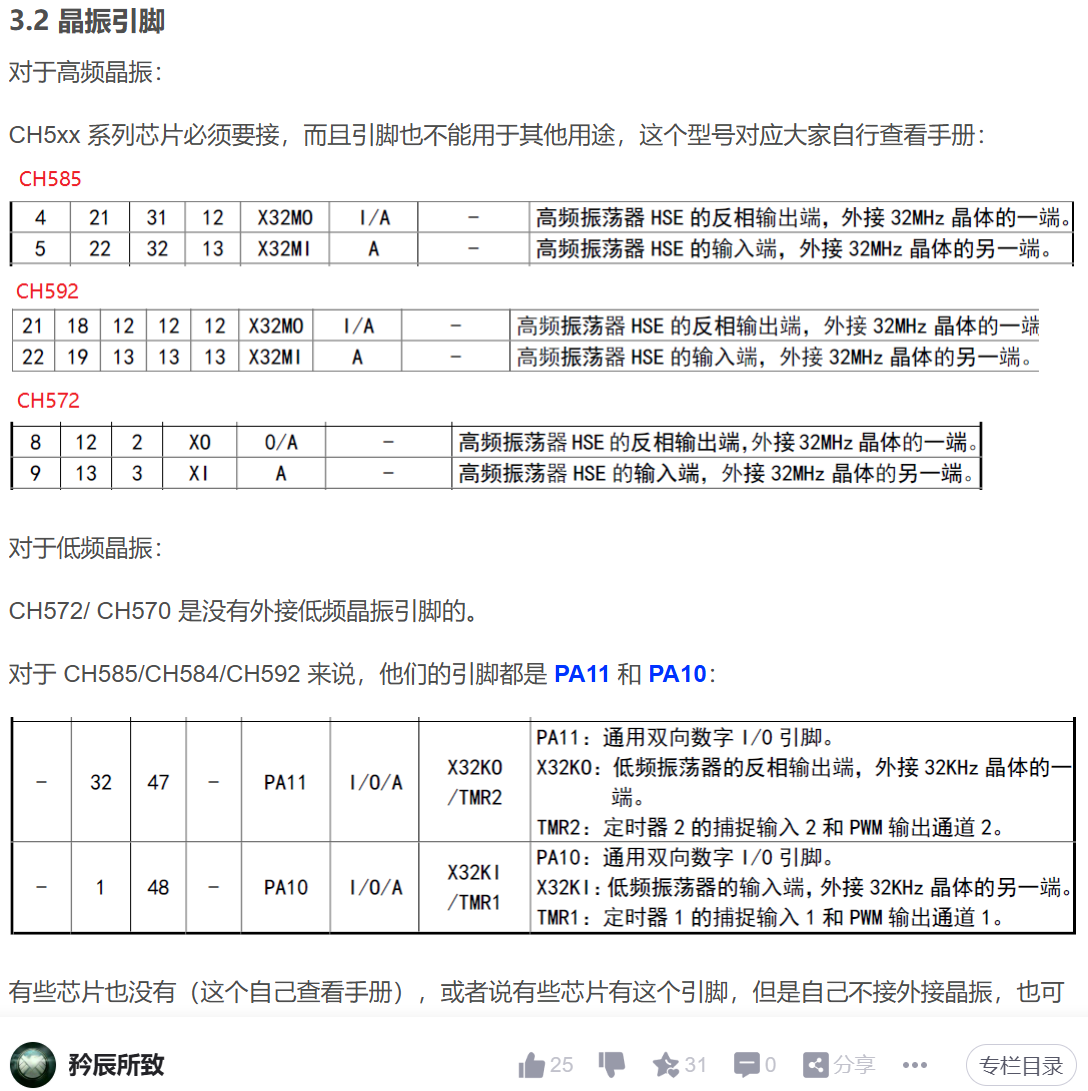

2.2 晶振

在博主的文章《沁恒微 RISC-V 蓝牙 CH5xx GPIO使用说明》有过说明:

2.2.1 高频晶振

外接晶振必须要接,固定引脚(自行查看手册)。

推荐型号: 32Mhz /10ppm /12pF

注意一下,沁恒微 CH57x/58x/59x 系列芯片的外接晶振(不管高频还是低频)都不需要外接匹配电容。 芯片有内置负载电容可调节。

比如上面使用了外部 32Mhz 晶振,在程序开头会有:

HSECFG_Capacitance(HSECap_18p); //先设置匹配电容

SetSysClock(SYSCLK_FREQ); //再设置系统时钟下面晶振规格说明来自文章(仅供参考):https://www.cnblogs.com/gscw/p/17387204.html

使用8pf的晶振规格是否可以使用?

答:晶体标称的规格是指在该规格时,晶振的振荡频率为最吻合的。

可以通过公式计算,芯片内置负载电容选择最低为10pf,再加上板子的寄生电容约2pf,则负载电容值最低为7pf左右。

因此如使用8pf的规格,则不需要外挂电容。

但是需要注意一点,使用蓝牙功能的2.4G信号是通过32M倍频上去的,因此32M如果有偏差则2.4G也会产生对应的频偏。一般建议的是如果2.4G频偏最准的情况下,则频偏可以调整为18或者20pf。这与上面选择10pf的内置负载电容是有偏差的,但是实际使用理论上不受到影响(针对蓝牙频偏则是建议在最准的情况下使用,偏差范围在±60K使用也是没问题的)。

官方建议使用12pf的电容,是因为在不同的板子上即使寄生电容偏差较大也可以有较好的调整空间。

在使用的8pf规格晶振时,可以适当调整芯片的内置匹配电容参数,如10\12\14pf进行实际测试,注意查看晶振起振和蓝牙连接。

但是最终还是建议使用12pf规格参数的晶振。

2.2.2 低频晶振

低频晶振如果需要使用 Ble 主机,必须要接外部晶振,有些不支持外部晶振的芯片,就直接无法做 Ble 主机。

如果确保设备不需要用作主机,而且对 RTC 定时没有什么要求的话,可以用内部低频晶振做 RTC 时钟。RTC 引脚可以空闲出来用作普通 GPIO 口。

一般需要 RTC 定时,可能用到主机功能,要外接 32.768Khz 晶振。

推荐型号: 32.768Khz / 20ppm / 12.5pF

2.3 电源

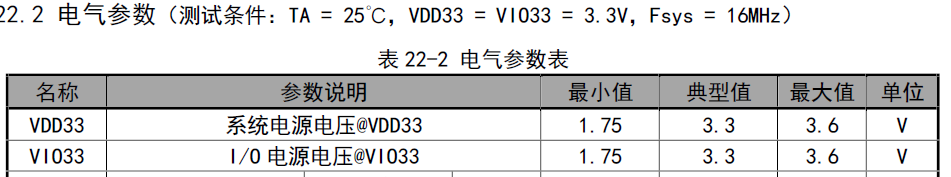

电源部分严格参考手册 参数 章节:

芯片最大供电电压为3.6V, 如果使用标压正好为 3.6V 的锂亚电池,建议串联一个肖特基二极管,因为锂亚电池的满电电压一般都是大于 3.6 V 的。

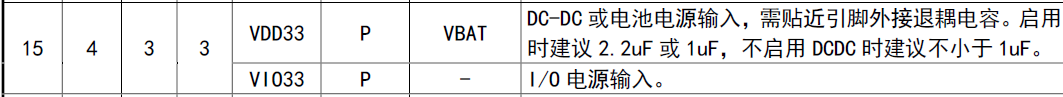

电源引脚为 VIO33/VDD33 (查看手册):

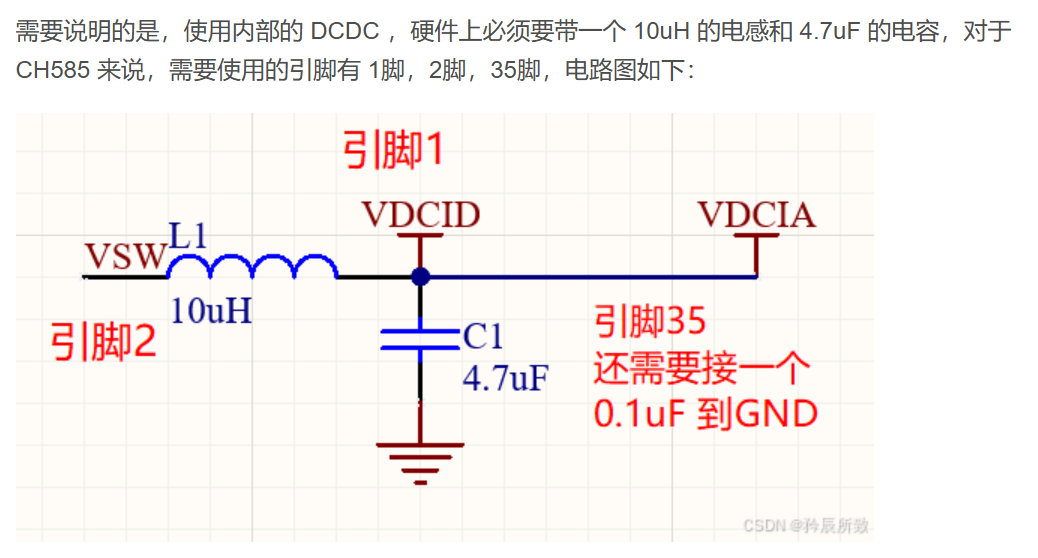

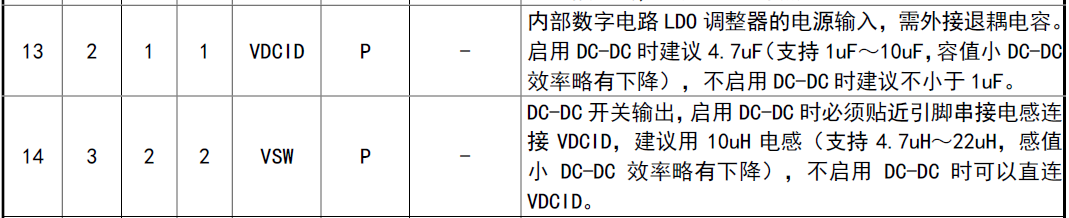

2.3.1 内部 DCDC

这里需要特别说明的是 内部 DCDC 是否启用对电路设计的影响。

我在文章《沁恒微 RISC-V 蓝牙芯片低功耗测试》提到过 DCDC :

上面有3个引脚: VSW VDCID VDCIA 。 具体的说明手册中也有:

如果开启了 DCDC ,就按照上面的图示连接,这也是官方开发板原理图的接法,如果确定自己不用 DCDC,那么可以省去电感,VSW VDCID VDCIA 三个引脚直连,并且在 VDCID VDCIA 引脚处挂退耦电容(参数规格参考官方手册,上图是以 CH585 为示例)。

2.4 GPIO

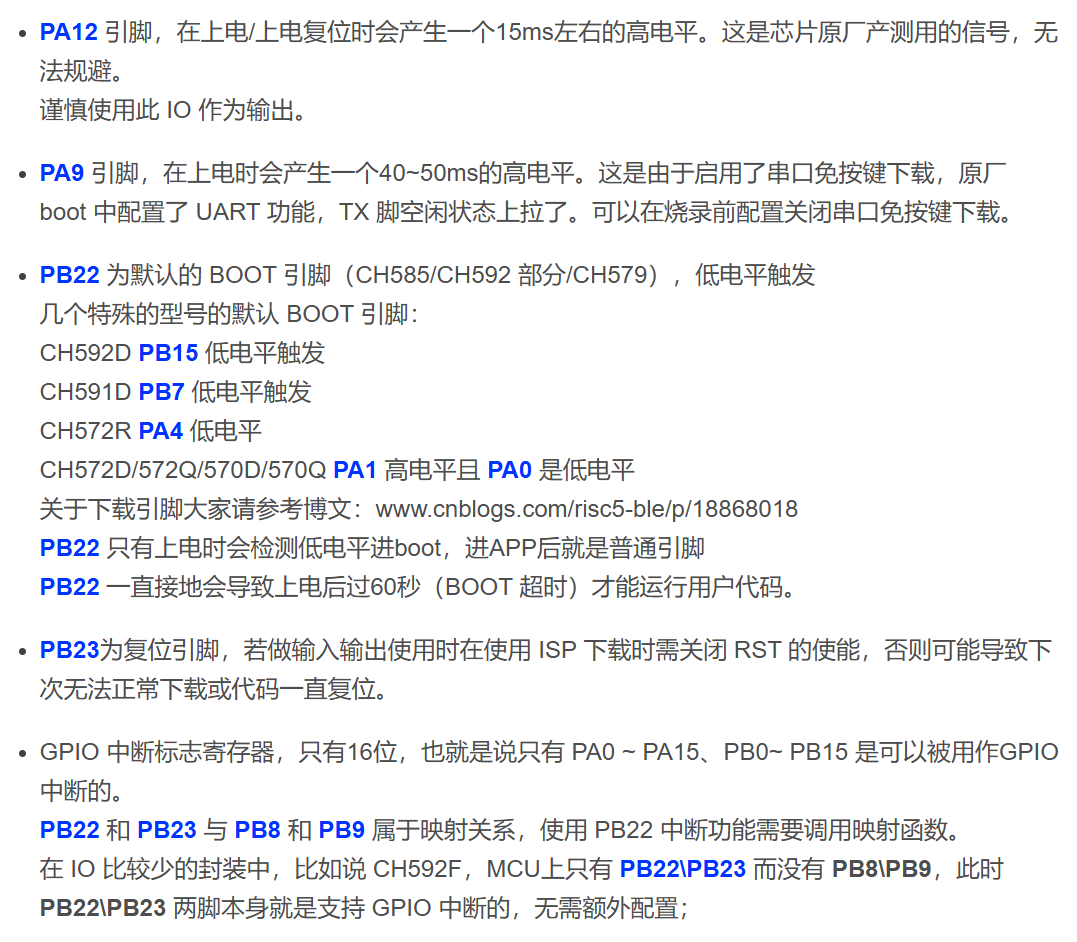

GPIO 设计呢,主要是要了解有一些特殊的 GPIO 引脚,这个在博主的文章《沁恒微 RISC-V 蓝牙 CH5xx GPIO使用说明》中的第三小节 GPIO 引脚说明 有过说明,如下图:

如果引脚足够,可以避开某些 IO 口,如果必须要用到,要注意到他们的特殊性,合理的分配这些特殊引脚。

2.5 关于下载引脚

如果以前习惯了 STM32 开发的小伙伴,都会想着下载仿真的 SWD 引脚需要单独预留出来的 。

对于 CH58x/CH59x 芯片来说也是支持 SWD 仿真下载(此 SWD 不是传统的 ARM 内核上的 SWD,是沁恒微自己的,需要配合沁恒微官方的 WCH_Link 使用)。

但是我不准备说明需要预留哪几个引脚,因为我个人压根就不想用这个 SWD 方式。

USB 和 串口已经足够方便,而且不需要额外的下载器。 有的小伙伴说没有 SWD 无法仿真,我就想问问市面上有哪一家蓝牙芯片是建议仿真来解决问题的? 芯片仿真会导致蓝牙断连,这是不可避免的,蓝牙芯片厂家都不会建议使用仿真查找问题 。

所以实际应用中,我并不建议特意预留 SWD 引脚,就把他们当作普通的 IO 口使用就好了,所以也不需要知道哪个引脚是 SWD 引脚,当然如果有特殊需求非要不可,大家可以自己查手册和对应资料。

至于下载,我们只需要根据上面 GPIO 口使用推荐的文章中的表格说明,考虑到自己应用使用 串口 还是 USB 下载把对应的引脚引出来就好了,比如:

表格参考文章:https://www.cnblogs.com/risc5-ble/p/18868018

而且下载完毕还能当作正常的串口 USB 口使用。

结语

本文博主按照自己应用设计的思路,说明了一下沁恒微 CH58x/CH59x 芯片的注意事项。

按照惯例,后面有机会的话会手把手教大家画一块应用板子 (●’◡’●) 。

好了,本文就到这里。谢谢大家!

浙公网安备 33010602011771号

浙公网安备 33010602011771号