【Cache缓存】基本概念 - 实践

目录

为什么需要cache

对于没有接触过底层技术的朋友来说,或许从未听说过cache。毕竟cache的存在对程序员来说是透明的。在接触cache之前,先看看下面的代码。

int arr[10][128];

for (i = 0; i < 10; i++)

for (j = 0; j < 128; j++)

arr[i][j] = i+j; 1;学习过C语言对这段code不会陌生。将arr数组所有元素置1。 这段code还有下面的一种写法。

int arr[10][128];

for (i = 0; i < 128; i++)

for (j = 0; j < 10; j++)

arr[j][i] = i+j; 1;功能完全一样,但是我们一直在重复着第一种写法(或许很多的书中也是建议这么编码),你是否想过这其中的缘由?文章的主角是cache,那cache是如何影响这2段code的呢?

Cache的局部性

1、时间局部性:当前正在提取的数据或指令可能很快就需要使用,因此将数据或指令存储在缓存中,这样可以避免再次在主存中搜索相同的数据。例如代码循环里的数据等

2、空间局部性:主要是指存储在最近执行的指令附近的所有指令都有很高的执行机会。同时指的是对存储位置相对较近的数据元素(指令)的使用

在思考为什么需要cache之前,我们首先先来看看另一个问题:程序是如何运行起来的?

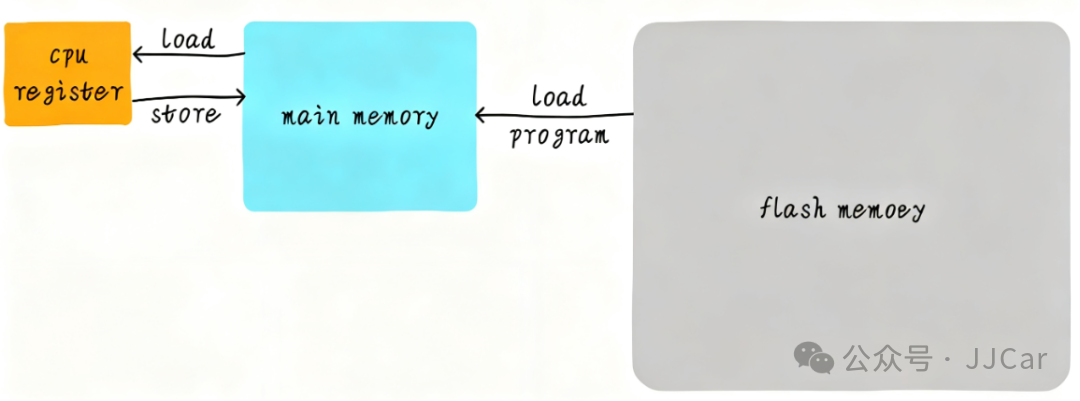

我们知道程序是运行在 RAM中的,RAM 就是我们常说的DDR(例如: DDR3、DDR4等)。我们称之为main memory(主存)。当我们需要运行一个进程的时候,首先会从磁盘设备(例如,eMMC、UFS、SSD等)中将可执行程序加载到主存中,然后开始执行。在CPU内部存在一堆通用寄存器(register)。如果CPU需要将一个变量(假设地址是A)加1,一般分为以下3个步骤:

(1)CPU 从主存中读取地址A的数据到内部通用寄存器 x0(ARM64架构的通用寄存器之一)。

(2)通用寄存器 x0 加1。

(3)CPU 将通用寄存器 x0 的值写入主存。

我们将这个过程可以表示如下:

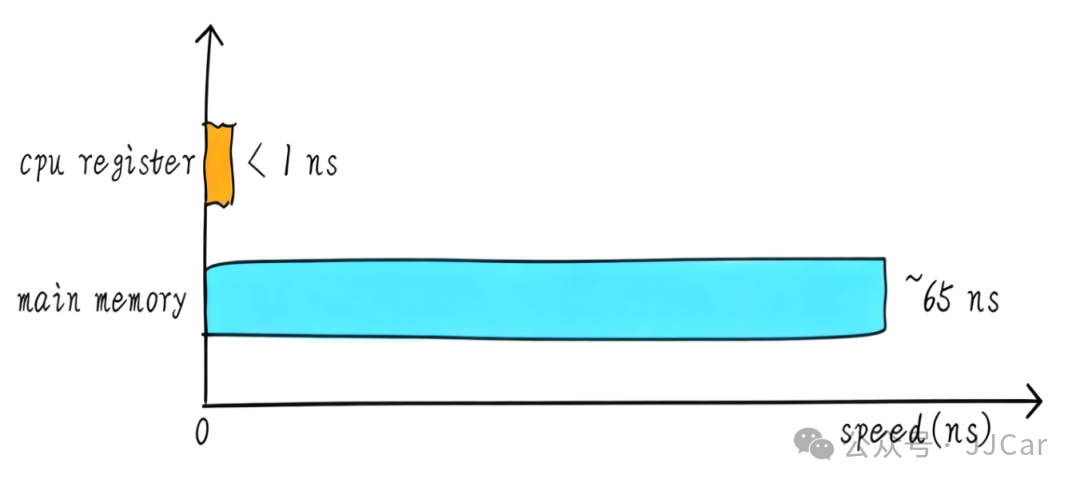

其实现实中,CPU通用寄存器的速度和主存之间存在着太大的差异。两者之间的速度大致如下关系:

CPU register的速度一般小于1ns,主存的速度一

浙公网安备 33010602011771号

浙公网安备 33010602011771号